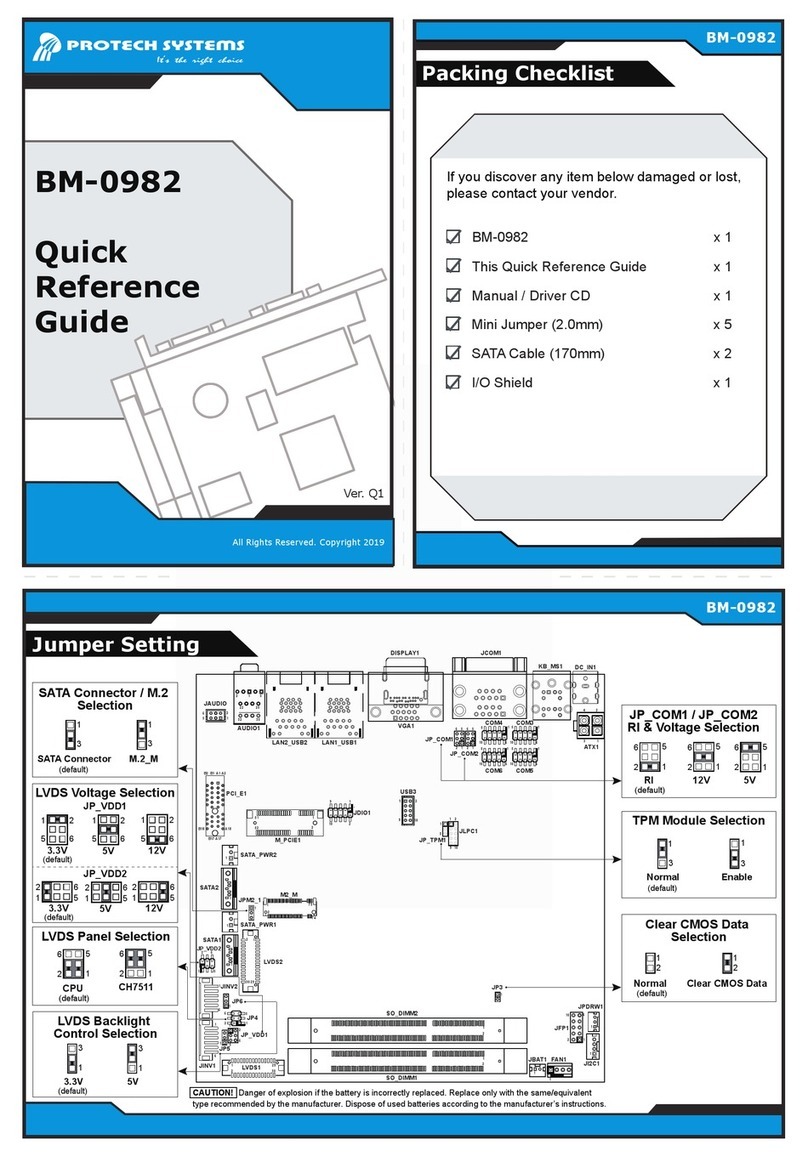

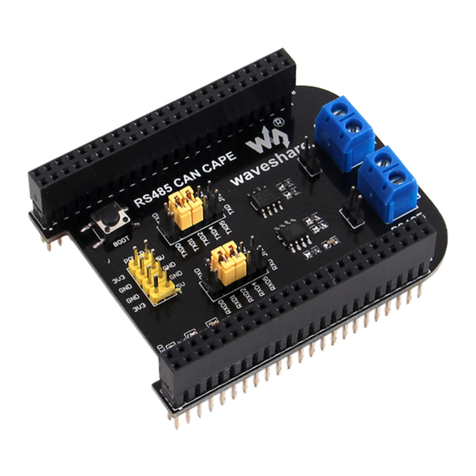

2.5 Holdover Mode

The DSPLL will automatically enter Holdover mode when the selected input clock becomes invalid and no other valid input clocks

are available for selection. It uses an averaged input clock frequency as its final holdover frequency to minimize the disturbance of

the output clock phase and frequency when an input clock suddenly fails. The holdover circuit stores up to 120 seconds of historical

frequency data while locked to a valid clock input. The final averaged holdover frequency value is calculated from a programmable

window within the stored historical frequency data. Both the window size and the delay are programmable as shown in the figure below.

The window size determines the amount of holdover frequency averaging. This delay value allows recent frequency information to be

ignored for Holdover in cases where the input clock source frequency changes as it is removed.

Programmable delay

Clock Failure

and Entry into

Holdover

time

0s

Historical Frequency Data Collected

Programmable historical data window

used to determine the final holdover value

120s

1s,10s, 30s, 60s

30ms, 60ms, 1s,10s, 30s, 60s

Figure 2.3. Programmable Holdover Window

When entering Holdover, the DSPLL will pull its output clock frequency to the calculated averaged holdover frequency. While in

Holdover, the output frequency drift is determined by the reference clock temperature drift. If a clock input becomes valid, the DSPLL

will automatically exit the Holdover mode and reacquire lock to the new input clock. This process involves pulling the output clock

frequency to achieve frequency and phase lock with the input clock. This pull-in process is Glitchless and its rate is controlled by the

DSPLL bandwidth or the Fastlock bandwidth, if Fastlock is enabled. These options are register programmable.

The recommended mode of exit from holdover is a ramp in frequency. Just before the exit begins, the frequency difference between the

output frequency while in holdover and the desired, new output frequency is measured. It is quite possible that the new output clock

frequency will not be exactly the same as the holdover output frequency because the new input clock frequency might have changed

and the holdover history circuit may have changed the holdover output frequency. The ramp logic calculates the difference in frequency

between the holdover frequency and the new, desired output frequency. Using the user selected ramp rate, the correct ramp time is

calculated. The output ramp rate is then applied for the correct amount of time so that when the ramp ends, the output frequency will

be the desired new frequency. Using the ramp, the transition between the two frequencies is smooth and linear. The ramp rate can be

selected to be very slow (0.2 ppm/sec), very fast (40,000 ppm/sec) or any of approximately 40 values that are in between. The loop

BW values do not limit or affect the ramp rate selections and vice versa. CBPro defaults to ramped exit from holdover. Ramping is also

used for ramped input clock switching. See 3.2.4 Ramped Input Switching for more information. See AN1057: Hitless Switching using

Si534x/8x Devices for more information on Hitless and Ramped Switching with Rev. E devices.

As shown in Figure 2.1 Modes of Operation on page 10 the Holdover and Free run modes are closely related. The device will only

enter Holdover if a valid clock has been selected long enough for the holdover history to become valid, i.e., HOLD_HIST_VALID = 1.

If the clock fails before the combined HOLD_HIST_LEN + HOLD_HIST_DELAY time has been met, HOLD_HIST_VALID = 0 and the

device will enter Free run mode instead. Note that when switching between input clocks with different (non-0 ppm offset) frequencies,

the holdover history requires a time of 2 * HOLD_HIST_LEN + HOLD_HIST_DELAY to update the average frequency value. If a switch

is initiated before this time, the average holdover frequency will be a value between the old input frequency and the new one.

Note: The Holdover history accumulation is suspended when the input clock is removed and resumes accumulating when a valid input

clock is again presented to the DSPLL.

Si5386 Rev. E Reference Manual • Modes of Operation

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 •

[email protected] • www

.skyworksinc.com

14 Rev. 1.2 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • December 9, 2021 14