ACC-JTAG-BR Hardware Reference Guide

Rev 1.0 www.bittware.com 5

BittWare Proprietary - Do Not Distribute Without Permission from BittWare

Contents

1. ACC-JTAG-BR Overview...........................................................................................................8

1.1 Product Description.................................................................................................................8

1.2 Feature List .............................................................................................................................8

1.3 Supported JTAG Programming Cables ..................................................................................9

1.4 Supported BittWare FPGA Cards ...........................................................................................9

2. Usage with 250-SoC................................................................................................................11

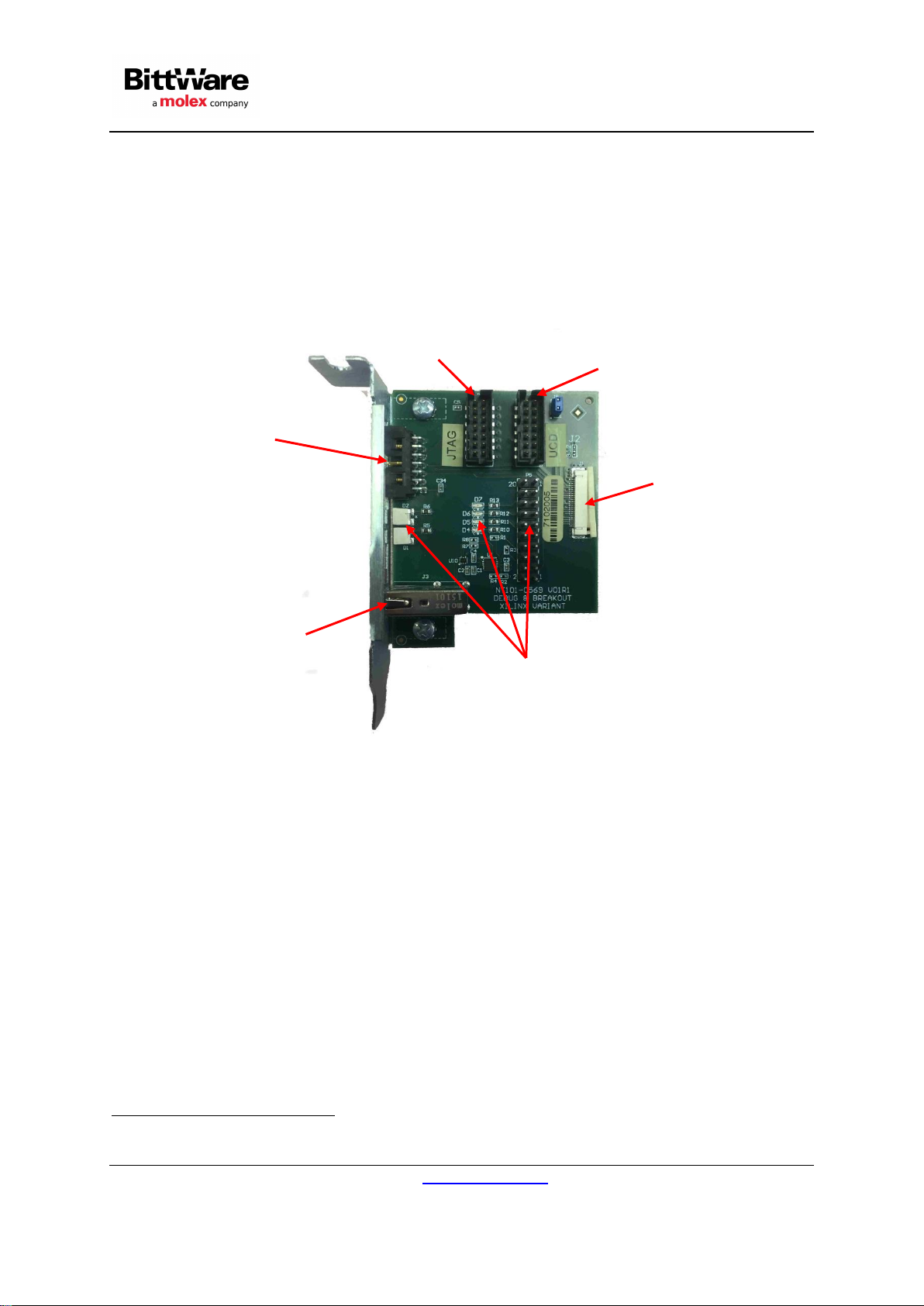

2.1 Physical Connections............................................................................................................11

2.1.1 Connection to JTAG Programming Cables.......................................................................11

2.1.2 Connection to FPGA Card ................................................................................................11

2.2 JTAG Chain...........................................................................................................................12

2.3 Other Features......................................................................................................................12

2.3.1 I2C Bus..............................................................................................................................12

2.3.2 PS Reset Push Button ......................................................................................................12

3. Usage with 250S+....................................................................................................................14

3.1 Physical Connections............................................................................................................14

3.1.1 Connection to JTAG Programming Cables.......................................................................14

3.1.2 Connection to FPGA Card ................................................................................................14

3.2 JTAG Chain...........................................................................................................................15

3.3 Other Features......................................................................................................................15

3.3.1 FPGA Output Signals (LED Indicator) ..............................................................................15

3.3.2 FPGA Input Signal.............................................................................................................16

3.3.3 FPGA-driven UART...........................................................................................................16