3(E)

Notes

• The MONITOR OUT signals are available only

when the power of the video monitor is ON. The

MONITOR OUT signals are not available when the

monitor is in standby mode.

• The MONITOR OUT signals do not satisfy the ON-

LINE signal specifications.

Input of analog signals

You can input a Y or G signal to connector 5, a P

B

or

B signal to connector 7, a P

R

or R signal to connector

9. You can obtain loop-through output of those

signals from connectors 6, 8, and 0. If you do not

wish to use loop-through output, attach 75-ohm

terminators to connectors 6, 8, and 0.

Assigning input signals to connectors

Before inputting signals to the BKM-41HD/42HD, you

must specify the type and format of the signal that will

be input to each connector. To assign input signals to

each connector, use the on-screen INPUT

CONFIGURATION menu of your video monitor.

For information about using the INPUT CONFIGURATION

menu, refer to the manual of your video monitor.

Specifications

General

Power requirements +5V, ±6V

(supplied from the monitor)

Power consumption BKM-41HD: 9W

BKM-42HD: 14.5W

Recommended operating temperature

20°C to 30°C (68°F to 86°F)

Permissible operating temperature

0°C to 35°C (32°F to 95°F)

Operating humidity 30% to 85% (no condensation)

Maximum external dimensions (w/h/d)

50 ×256 ×245 mm

(2

×10

1

/

8

×9

3

/

4

inches)

Mass BKM-41HD: Approx. 1280g

(2lb 13oz)

BKM-42HD: Approx. 1400 g

(2lb 14oz)

Input/Output Connectors

Digital input BKM-41HD: BNC ×1,

with monitor output

BKM-42HD: BNC ×2,

with monitor output

Analog input Both BKM-41HD and BKM-

42HD: BNC ×3, with loop-

through output

Signal Characteristics

Analog signals

Signal level 1Vp-p±6dB (sync on Y or G)

Frequency characteristics

60Hz to 30MHz±1dB

Delay time error 10nsec max.

Gain error 3%max.

Return loss 40 dB min.

(10MHz, 75-ohm terminated)

Digital signals

HD SDI signal input

Input impedance 75 ohms, unbalanced

Data rate 1.4835Gbps to 1.485Gbps

Conform to SMPTE 292M, BTA-S004A

MONITOR OUT

Output signal amplitude

800mVp-p±10%

Output impedance75 ohms, unbalanced

Frequency response

Y: 60Hz to 30MHz±1dB

P

B

, P

R

: 60Hz to 15MHz±1dB

Delay time error 13.5nsec max.

Gain error 3% max.

Transmission distance100m (approx. 40ft) max.,

When using 5C-FB coaxial

cables (Fujikura, Inc.) or

equivalent.

Accessory Supplied

Installation manual (1)

Design and specifications are subject to change

without notice.

4(E)

Installing into Video Monitors

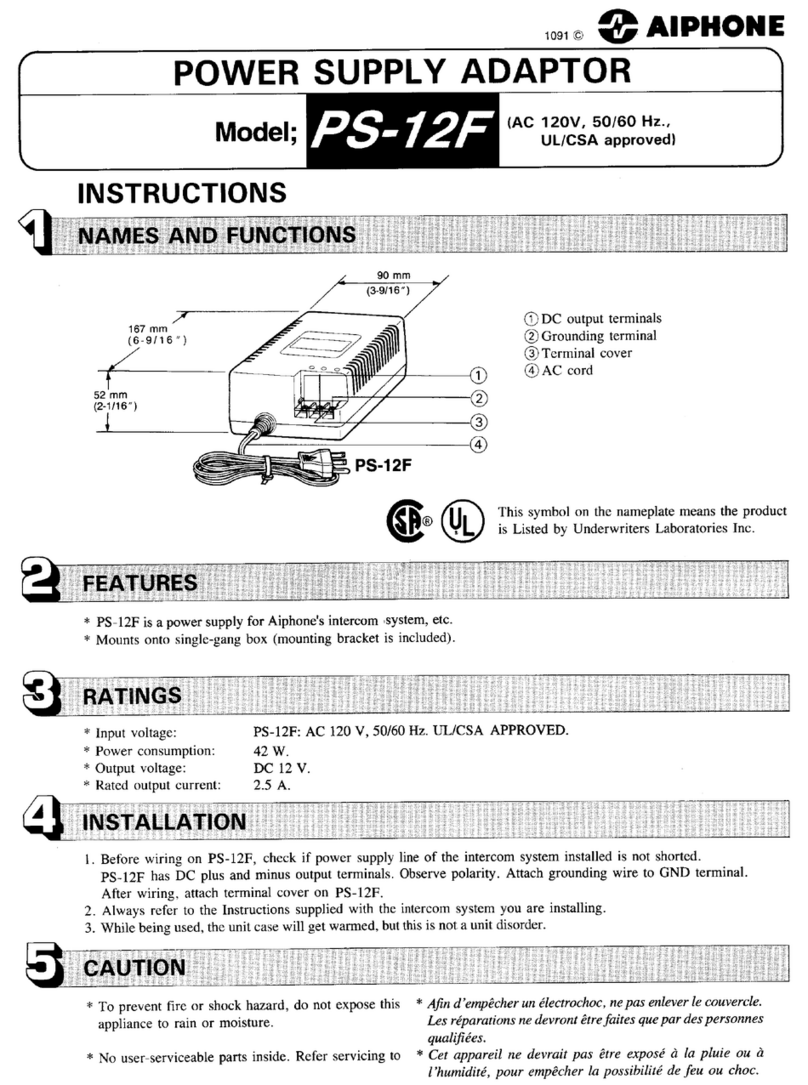

1

Remove the two covers of the

input option slots on the rear

panel of your video monitor.

2

Insert the adaptor below the

alignment mark on the left of

the upper screw hole of the

slot.

3

Push the adaptor in until it is

firmly seated in the connector

inside your video monitor.

4

Tighten the both upper and

lower screws to retain the

adaptor.

Check to be sure that the video monitor's MAIN POWER switch is off.

Each adaptor can be installed in any input option slot .

The BKM-41HD/42HD require two slots. Always turn your video monitor's MAIN POWER

switch off before installing or removing the adaptor.

Alignment mark

Insert the adaptor

below the mark.

Covers of input

option slots