1

CONTENTS

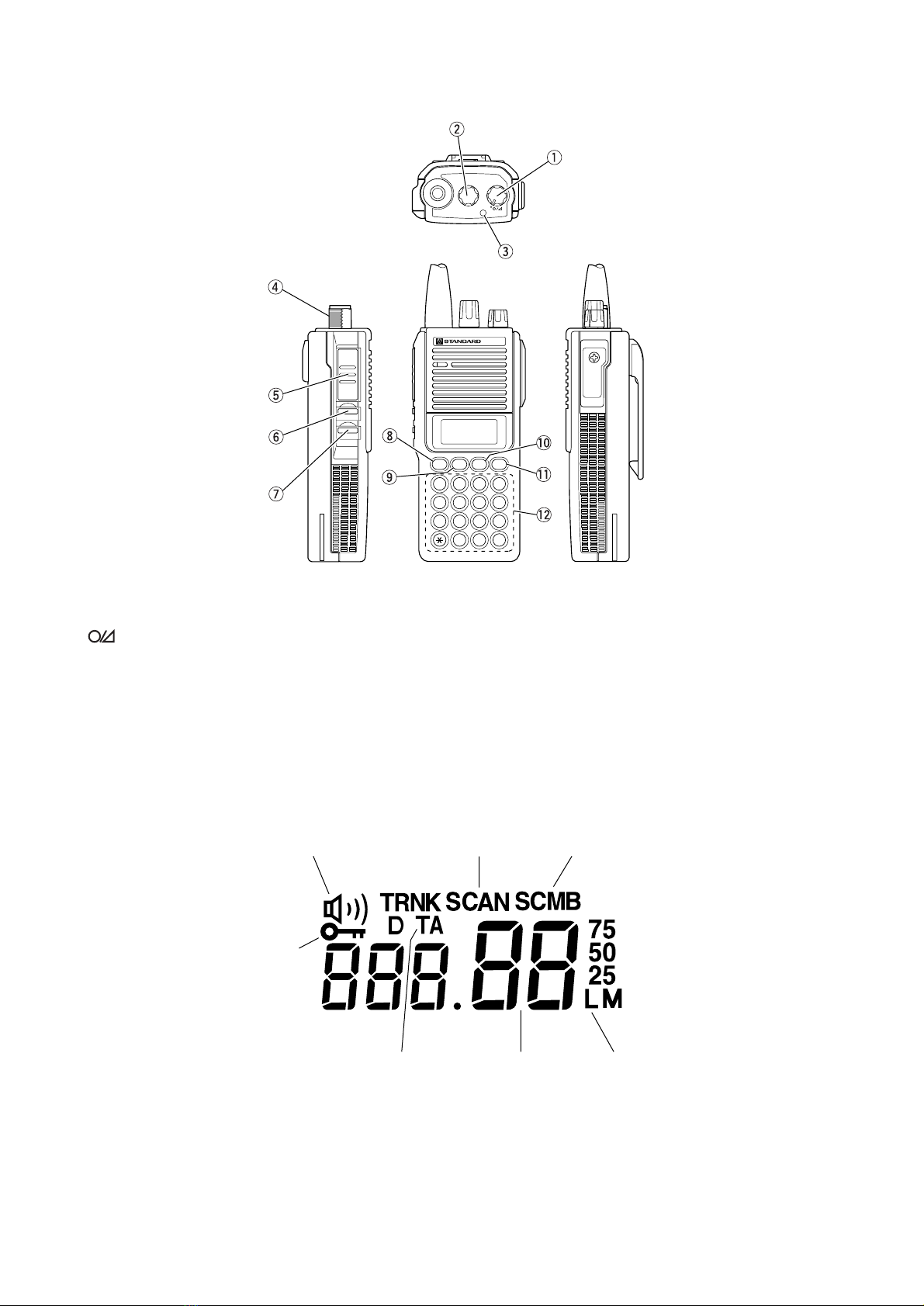

1. CONTROLS AND CONNECTIONS..........................................................................................................................................2

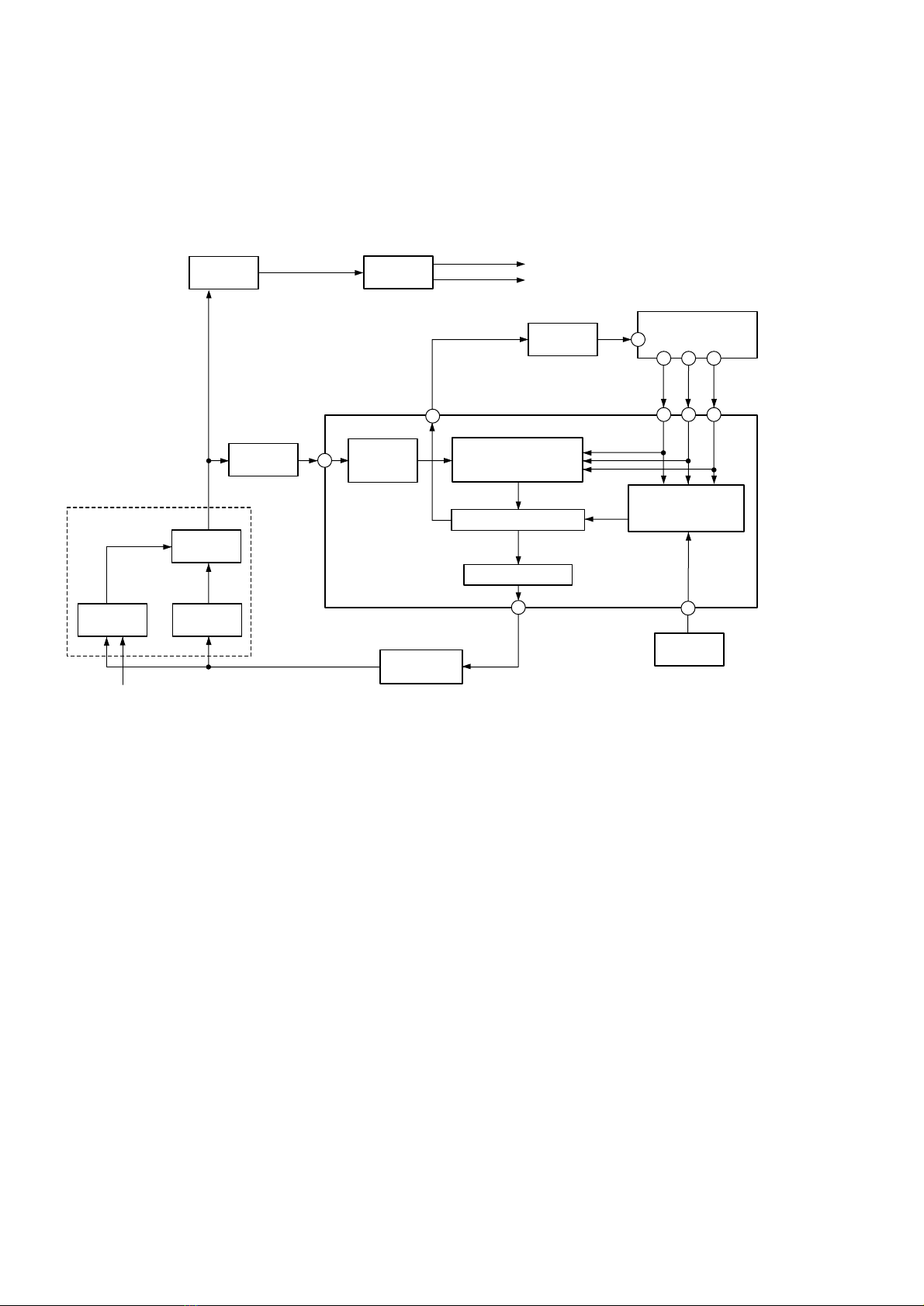

2. THEORY OF OPERATIONS.....................................................................................................................................................3

2.1 PLL Block ...........................................................................................................................................................................3

2.2 Receiver Block ...................................................................................................................................................................4

2.3 Transmitter Block ..............................................................................................................................................................6

2.4 Control Block .....................................................................................................................................................................7

2.5 Power Supply Block ........................................................................................................................................................10

3. DISASSEMBLY ......................................................................................................................................................................11

3.1 Removing the Diecast frame ..........................................................................................................................................11

3.2 Removing the TX/RX/CONTROL P.C.board...................................................................................................................12

4. ADJUSTMENT........................................................................................................................................................................13

4.1 Adjustment Connection Diagrams.................................................................................................................................16

4.2 Adjustment Point Diagrams............................................................................................................................................17

4.3 HX290UKA Adjustment and Confirmation ....................................................................................................................18

4.3.1 PLL Block ................................................................................................................................................................18

4.3.2 Transmitter Block ...................................................................................................................................................18

4.3.3 Receiver Block ........................................................................................................................................................19

5. SPECIFICATIONS ..................................................................................................................................................................21

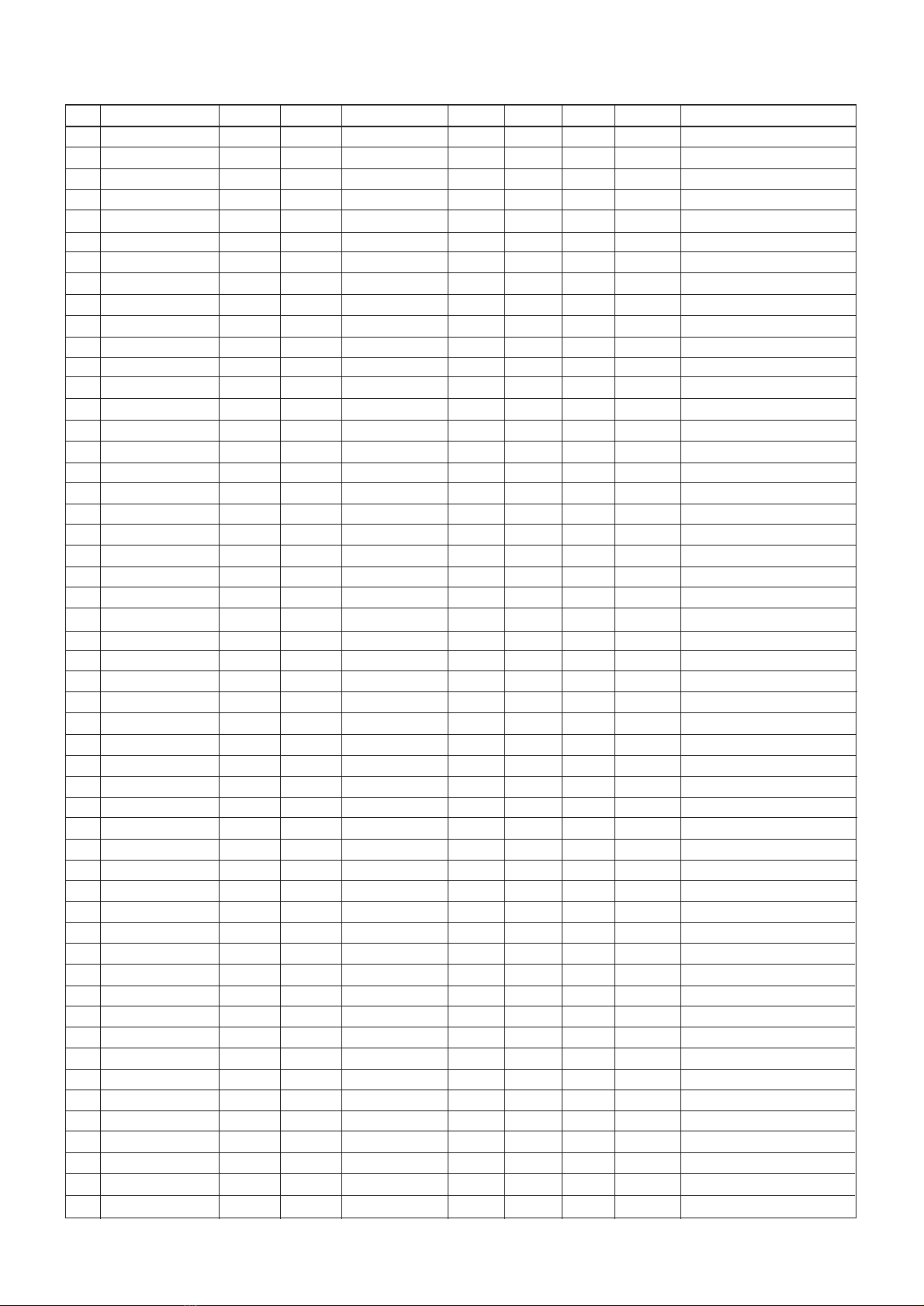

6. PARTS LIST ...........................................................................................................................................................................22

7. EXPLODED PARTS VIEW .....................................................................................................................................................30

8. PACKING DIAGRAM AND PARTS LIST...............................................................................................................................31

9. BLOCK DIAGRAM .................................................................................................................................................................32

10. SCHEMATIC DIAGRAM ........................................................................................................................................................33

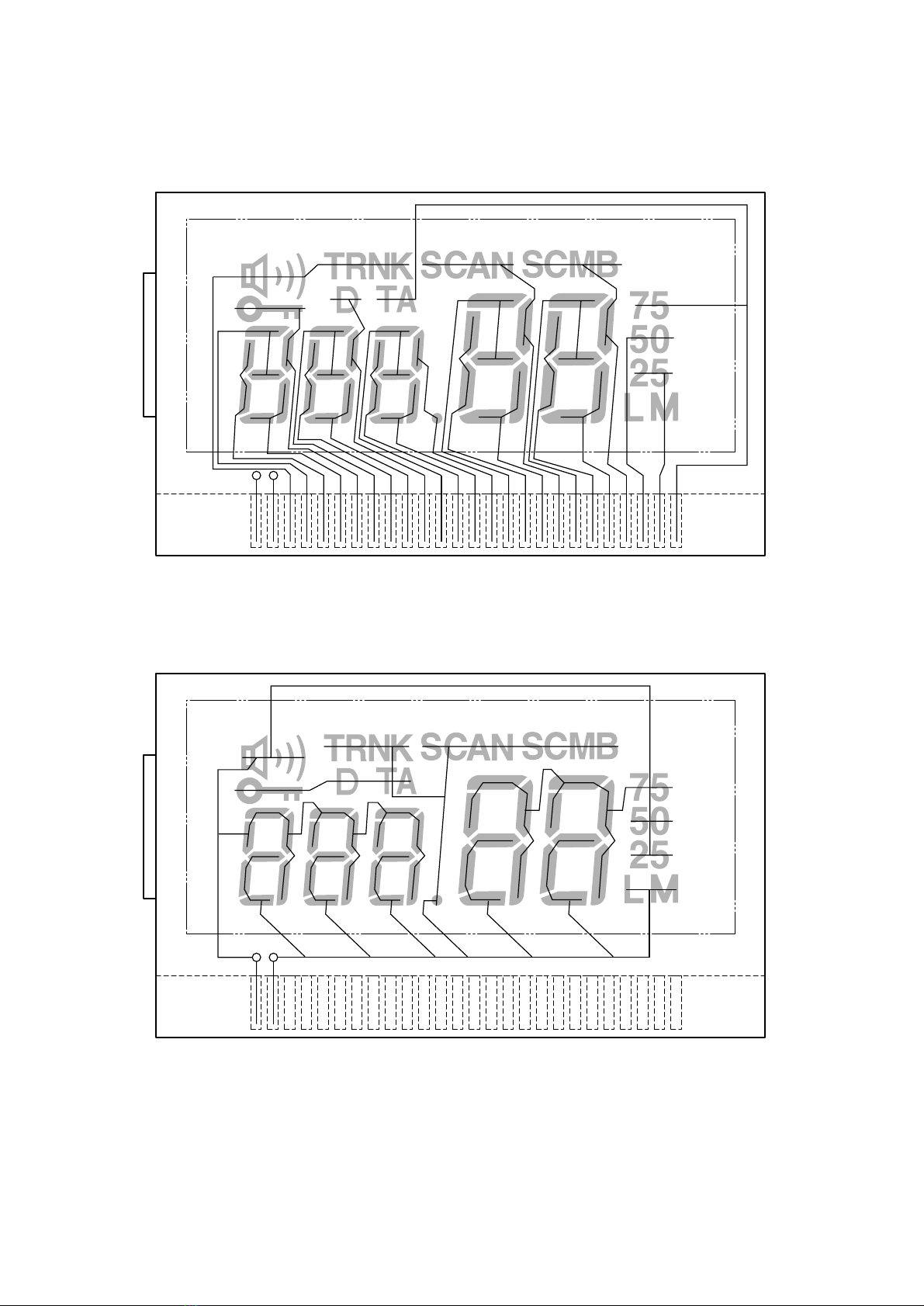

10.1 HX290UKA131 ................................................................................................................................................................33

10.2 HX290UKA191 ................................................................................................................................................................34

10.3 HX290UKA181 ................................................................................................................................................................35

10.4 HX290UKA111 ................................................................................................................................................................36

11. COMPONENT OVERLAY DIAGRAM ....................................................................................................................................37

This service manual is for use with the HX290UKA131/191/181/111 transceiver.

The HX290UKA131 is a transceiver for use with the 450MHz to 470 MHz.

The HX290UKA191 is a transceiver for use with the 370MHz to 390 MHz.

The HX290UKA181 is a transceiver for use with the 345MHz to 370 MHz.

The HX290UKA111 is a transceiver for use with the 405MHz to 430 MHz.

• Accessories

HX290 Transceiver

Flexible antenna

Beltclip

Owner's manual

•Options

CNB290 : Ni-Cd battery pack (7.2 V 1100 mAh)

CNB291 : Ni-Cd battery pack (7.2 V 1500 mAh)

CSA290 : Charger

CSA291 : Rapid charger