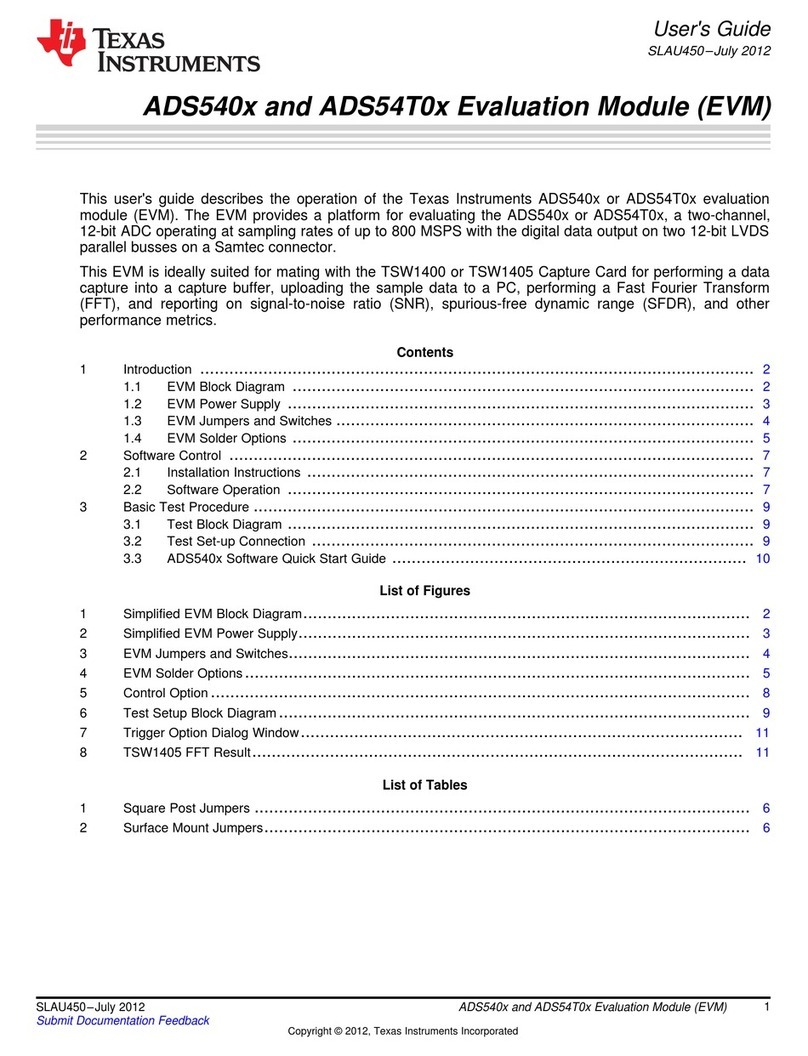

3.1 Issue 1 - HDMI/DSS Incorrect Colors on E1.................................................................................................................... 64

3.2 Issue 2 - J9 and J10 Header Alignment on E1.................................................................................................................64

3.3 Issue 3 - USB Boot descoped on E1................................................................................................................................65

3.4 Issue 4 - OLDI Connector Orientation and Pinout............................................................................................................65

3.5 Issue 5 - Bluetooth descoped on E2 EVMs......................................................................................................................65

3.6 Issue 6 - Ethernet PHY CLK Skew Default Strapping Changes...................................................................................... 65

3.7 Issue 7 - TEST_POWERDOWN changes........................................................................................................................66

3.8 Issue 8 - MMC1_SDCD spurious interrupts..................................................................................................................... 66

3.9 Issue 9 - PD Controller I2C2 IRQ Not Pinned Out........................................................................................................... 66

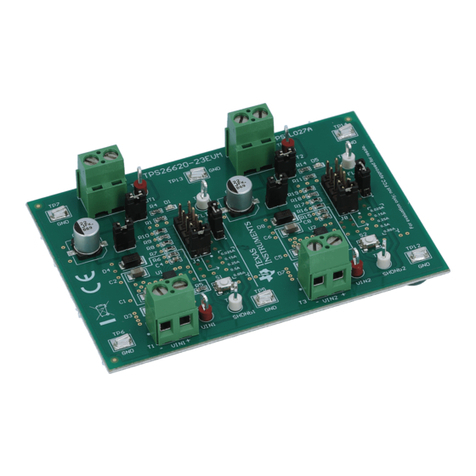

3.10 Issue 10 - INA Current Monitor Adress Changes...........................................................................................................66

3.11 Issue 11 - Test Automation I2C Buffer Changes.............................................................................................................66

Regulatory Compliance...........................................................................................................................................................68

Revision History.......................................................................................................................................................................68

List of Figures

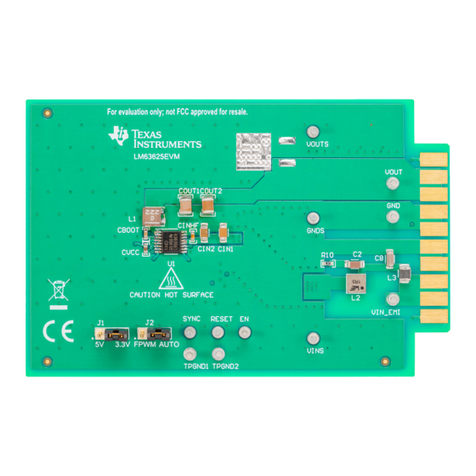

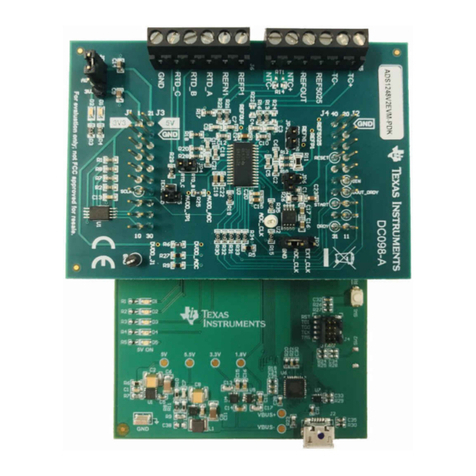

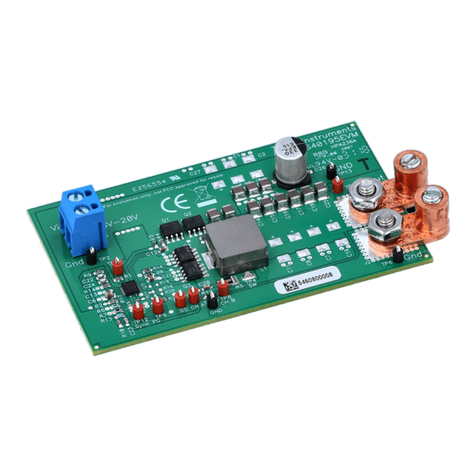

Figure 2-1. SK-AM62 Top View....................................................................................................................................................5

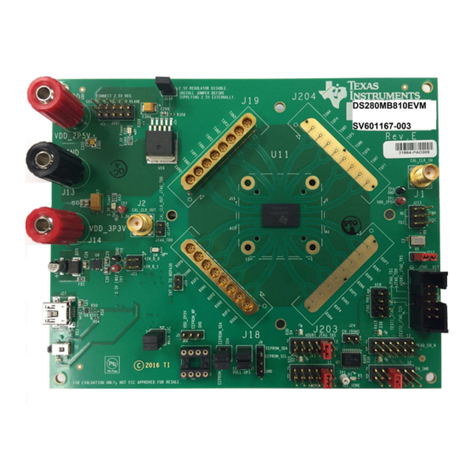

Figure 2-2. SK-AM62 Back View................................................................................................................................................. 6

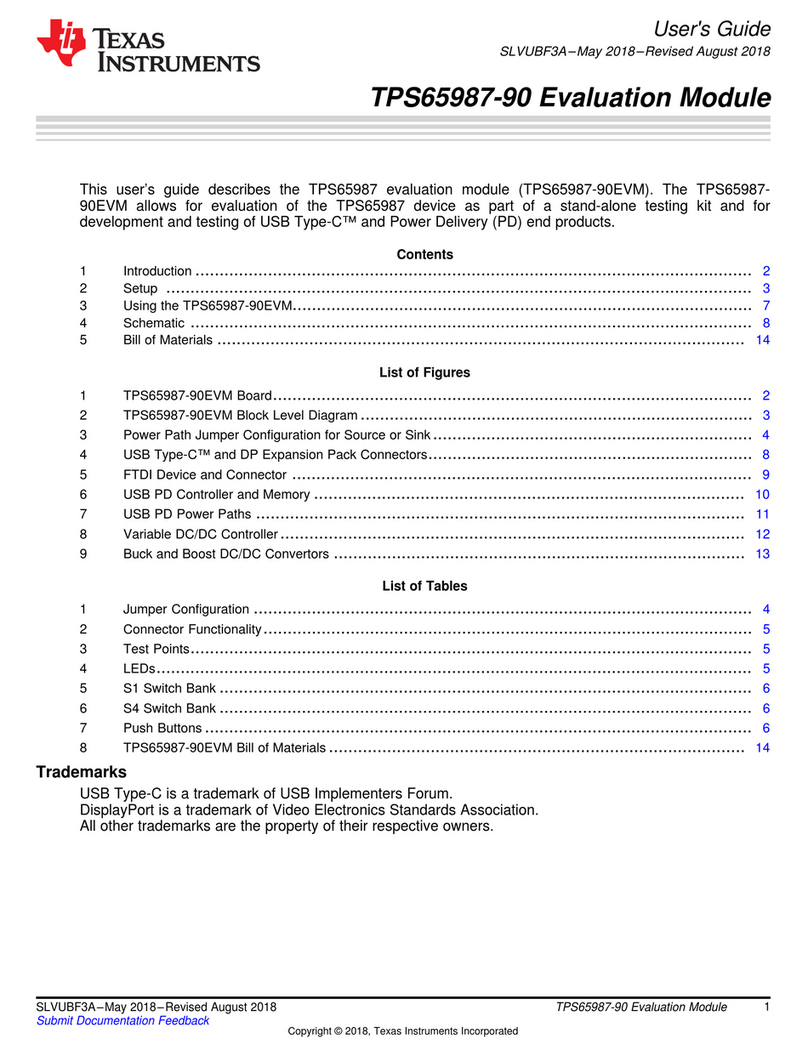

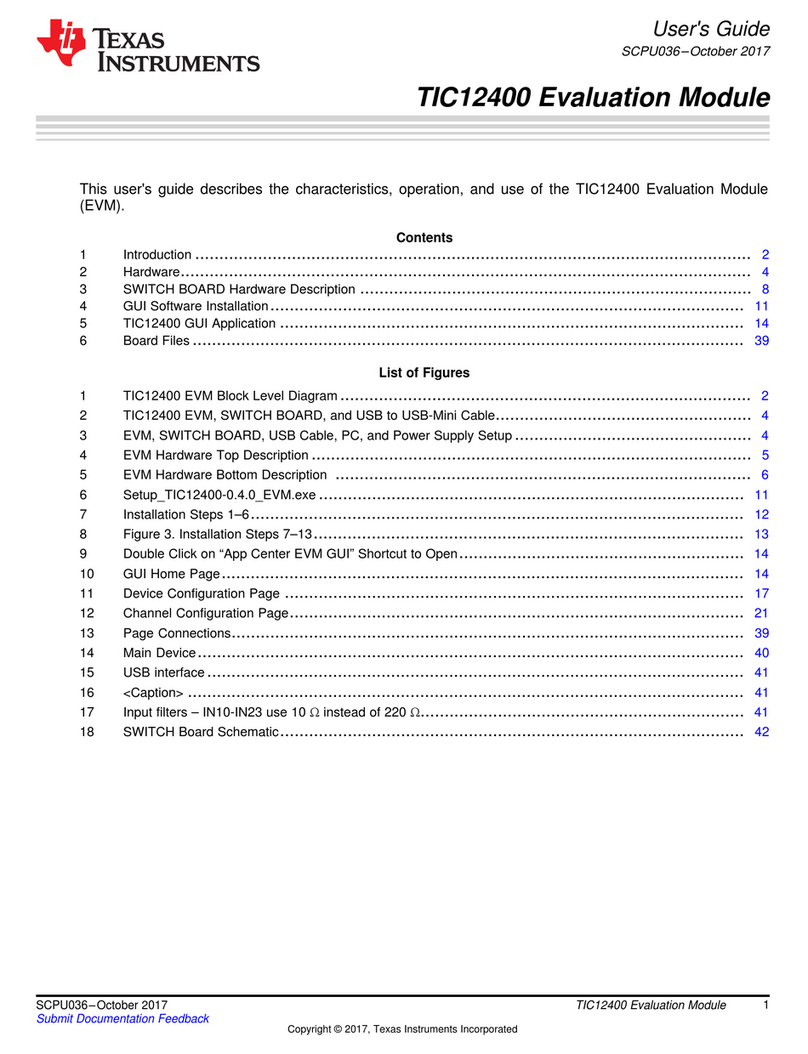

Figure 2-3. Functional Block Diagram of the AM62x SKEVM Board........................................................................................... 9

Figure 2-4. Functional Block Diagram of the AM62x SKEVM Board with TPS65219 PMIC......................................................10

Figure 2-5. SD Bootmode Switch Setting Example (E2, E3)..................................................................................................... 12

Figure 2-6. SD Bootmode Switch Setting Example (E1)........................................................................................................... 13

Figure 2-7. Clock Architecture of AM62x SKEVM..................................................................................................................... 14

Figure 2-8. SoC WKUP Domain................................................................................................................................................ 14

Figure 2-9. Bootmode Switch Configuration for SD Boot (E2, E3)............................................................................................ 50

Figure 2-10. Bootmode Switch Configuration for SD Boot (E1).................................................................................................51

Figure 3-1. PRU Connector Missalignment on E1 Boards........................................................................................................ 65

Figure 3-2. Schematic of I2C Buffer Section..............................................................................................................................67

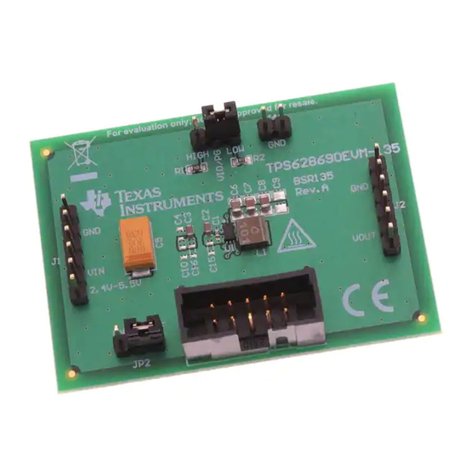

Figure 3-3. Location on AM62x SK E3 (Bottom Side)............................................................................................................... 67

List of Tables

Table 1-1. SK EVM PCB design revisions, and asssembly variants............................................................................................4

Table 2-1. Interface Mapping .....................................................................................................................................................11

Table 2-2. Power Test Points..................................................................................................................................................... 13

Table 2-3. Clock Table............................................................................................................................................................... 15

Table 2-4. Display Connector Pinout (As used by display and the E3 EVM).............................................................................16

Table 2-5. Display Connector Pinout (E1/E2)............................................................................................................................ 17

Table 2-6. CSI Camera Connector J19 Pin-out......................................................................................................................... 18

Table 2-7. JTAG Connector (J17) Pin-out.................................................................................................................................. 21

Table 2-8. Test Automation Connector (J23) Pin-out................................................................................................................. 23

Table 2-9. UART Port Interface..................................................................................................................................................24

Table 2-10. IO Expander Signal Detail.......................................................................................................................................36

Table 2-11. GPIO Mapping.........................................................................................................................................................38

Table 2-12. Type-C port Power roles......................................................................................................................................... 40

Table 2-13. Recommended External Power Supply.................................................................................................................. 40

Table 2-14. SoC Power Supply..................................................................................................................................................48

Table 2-15. INA I2C Device Address (E1)................................................................................................................................. 48

Table 2-16. INA I2C Device Address (E2)................................................................................................................................. 49

Table 2-17. BOOT-MODE Pin Mapping..................................................................................................................................... 51

Table 2-18. PLL Reference Clock Selection BOOTMODE [2:0]................................................................................................ 51

Table 2-19. Boot Device Selection BOOT-MODE [6:3]..............................................................................................................52

Table 2-20. Backup Boot Mode Selection BOOT-MODE [12:10]...............................................................................................52

Table 2-21. Primary Boot Media Configuration BOOT-MODE [9:7]........................................................................................... 52

Table 2-22. Backup Boot Media Configuration BOOT-MODE [13]............................................................................................ 53

Table 2-23. User test LEDs .......................................................................................................................................................53

Table 2-24. PRU Header (J10) Pin-out...................................................................................................................................... 54

Table 2-25. 40 Pin User Expansion Connector..........................................................................................................................55

Table 2-26. Pin MCU Connector (J9).........................................................................................................................................57

Table 2-27. EVM Push Buttons..................................................................................................................................................59

Table 2-28. I2C Mapping Table (SK-AM62 E3 and SK-AM62-P1 Variants)...............................................................................60

Table 2-29. I2C Mapping Table (SK-AM62 E2)..........................................................................................................................62

Table 3-1. AM62x SK EVM Known Issues and Modifications....................................................................................................64

Table of Contents www.ti.com

2AM62x SK EVM User's Guide SPRUJ40A – MAY 2022 – REVISED FEBRUARY 2023

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated