List of Figures

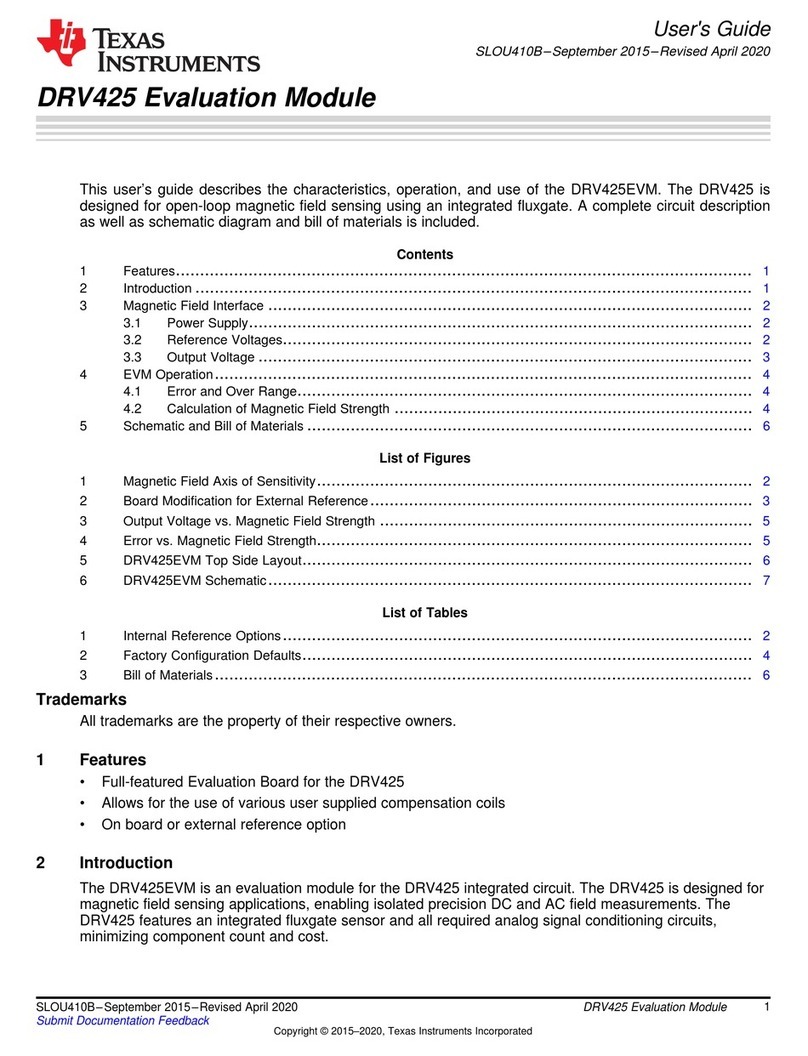

Figure 1-1. ADS1x48EVM Functional Block Diagram................................................................................................................. 5

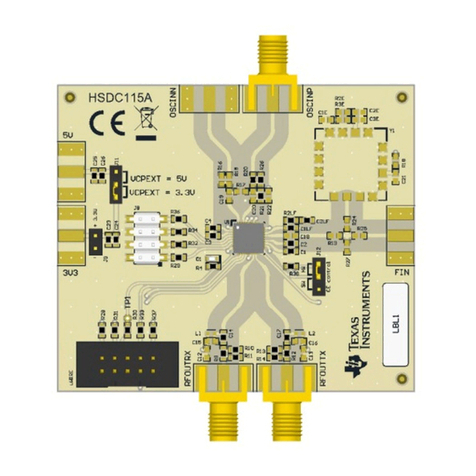

Figure 2-1. Connecting the ADS1x48EVM to the PAMB Board...................................................................................................6

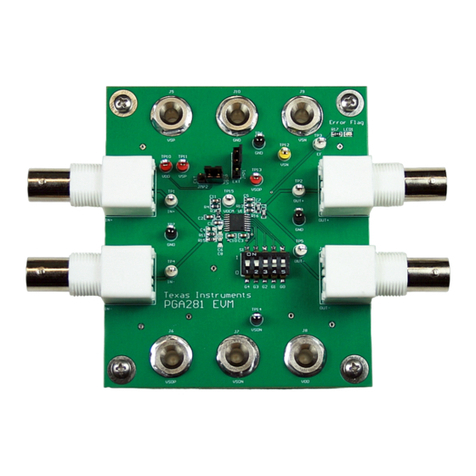

Figure 3-1. LED Indicators D1 and D5.........................................................................................................................................7

Figure 3-2. Jumper (JP1) Selects AVDD on the ADS1x48EVM.................................................................................................. 8

Figure 3-3. ADS1x48EVM VREF Options (Yellow) and Test Points (Red).................................................................................. 9

Figure 3-4. ADC Clock Options on the ADS1x48EVM.............................................................................................................. 10

Figure 3-5. ADS1x48EVM-to-PAMBoard Connections.............................................................................................................. 11

Figure 3-6. ADS1x48EVM Analog Input Terminal Blocks (J5, Left; J6, Right)...........................................................................12

Figure 3-7. Thermocouple Input Structure on the ADS1x48EVM..............................................................................................13

Figure 3-8. Using REF5025 (input J5:3) to Bias a Thermocouple............................................................................................. 13

Figure 3-9. Thermistor Input Structure on the ADS1x48EVM....................................................................................................15

Figure 3-10. Connecting a Thermistor to the J5 Terminal Block on the ADS1x48EVM.............................................................15

Figure 3-11. PCB Layout for J5 Terminal Block Showing Copper Pours for CJC Measurement............................................... 16

Figure 3-12. RTD Input Structure on the ADS1x48EVM............................................................................................................17

Figure 3-13. Connection Diagram for a 2-Wire RTD Using a Low-Side RREF .......................................................................... 19

Figure 3-14. Connection Diagram for a 2-Wire RTD Using a High-Side RREF ..........................................................................20

Figure 3-15. Connection Diagram for a 3-Wire RTD Using One IDAC and a Low-Side RREF ..................................................21

Figure 3-16. Connection Diagram for a 3-Wire RTD Using One IDAC and a High-Side RREF ................................................. 22

Figure 3-17. Connection Diagram for a 3-Wire RTD Using Two IDACs and a Low-Side RREF ................................................ 23

Figure 3-18. Connection Diagram for a 3-Wire RTD Using Two IDACs and a High-Side RREF ................................................24

Figure 3-19. Connection Diagram for a 4-Wire RTD Using a Low-Side RREF .......................................................................... 25

Figure 3-20. Connection Diagram for a 4-Wire RTD Using a High-Side RREF ..........................................................................26

Figure 3-21. Using the TC± Inputs on J5 as General-Purpose Signal Inputs............................................................................27

Figure 4-1. Browser Extension and TI Cloud Agent Installation................................................................................................ 28

Figure 4-2. ADS1x48EVM GUI Home Page.............................................................................................................................. 29

Figure 4-3. Connected Hardware Information........................................................................................................................... 29

Figure 4-4. File Menu.................................................................................................................................................................30

Figure 4-5. Data Capture Window............................................................................................................................................. 31

Figure 4-6. Capture Settings Slide-Out......................................................................................................................................31

Figure 4-7. Capture Statistics.................................................................................................................................................... 32

Figure 4-8. Time Domain Plot....................................................................................................................................................32

Figure 4-9. Histogram Plot.........................................................................................................................................................33

Figure 4-10. Register Map......................................................................................................................................................... 34

Figure 4-11. Register Read and Write Controls.........................................................................................................................34

Figure 4-12. Auto Read Options................................................................................................................................................ 35

Figure 4-13. Register Write Options.......................................................................................................................................... 35

Figure 5-1. Composite PCB Layout........................................................................................................................................... 38

Figure 5-2. Top Silkscreen......................................................................................................................................................... 39

Figure 5-3. Top Layer.................................................................................................................................................................39

Figure 5-4. Internal Ground Layer 1.......................................................................................................................................... 39

Figure 5-5. Internal Ground Layer 2.......................................................................................................................................... 39

Figure 5-6. Bottom Layer........................................................................................................................................................... 40

Figure 5-7. Bottom Silkscreen................................................................................................................................................... 40

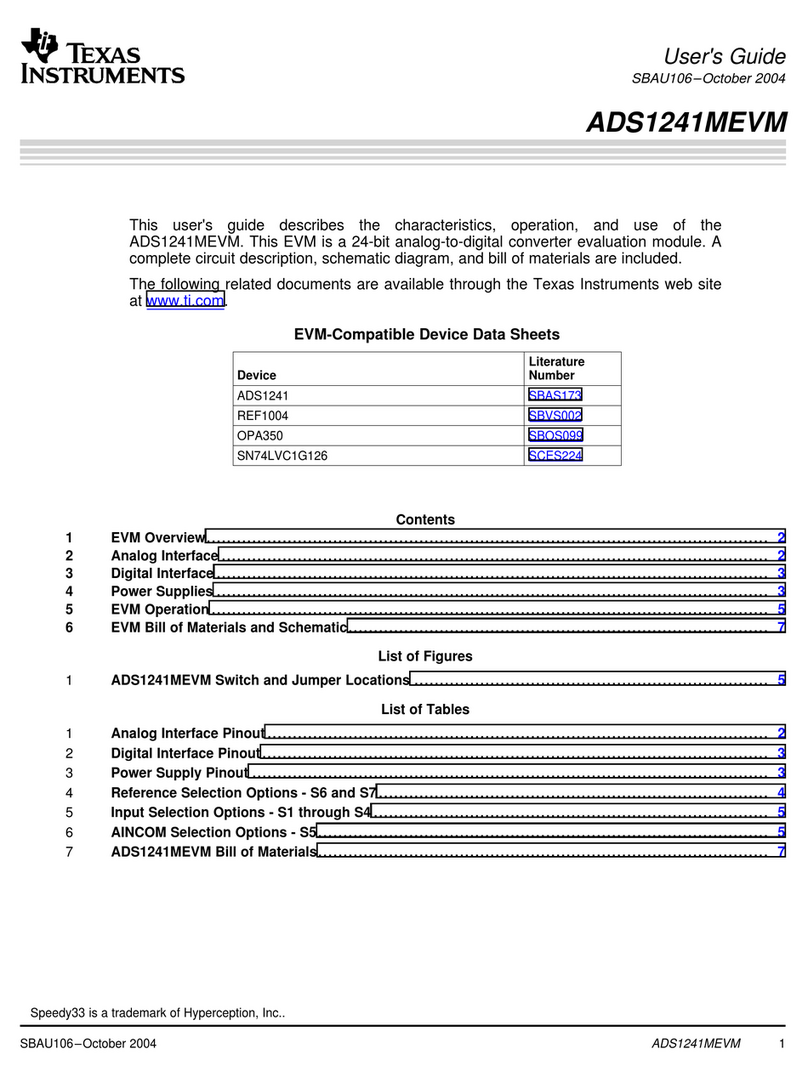

Figure 5-8. ADS1x48EVM Schematic........................................................................................................................................41

www.ti.com Table of Contents

SBAU378A – SEPTEMBER 2021 – REVISED JANUARY 2022

Submit Document Feedback

ADS1x48EVM Evaluation Module 3

Copyright © 2022 Texas Instruments Incorporated