TC32306FTG

2015-10-01

TOSHIBA CMOS Integrated Circuit Silicon Monolithic

TC32306FTG

Single-Chip RF Transceiver for Low-Power Systems

1. General Description

The TC32306FTG is a single-chip RF transceiver, which

provides many of the functions required for UHF-band

transceiver applications. It has the most features transmitting

and receiving the signal.

Furthermore, by digital processing, it can reduce significantly the

number of external components and allow fine adjustments.

Various type of applications are supported by this chip as

configuring various settings such as supply voltage, frequency,

modulation and detection.

2. Applications

Remote keyless entry (remote door lock / unlock of equipment),

automotive equipment applications such as tire pressure monitoring system, and remote controller, etc

3. Features

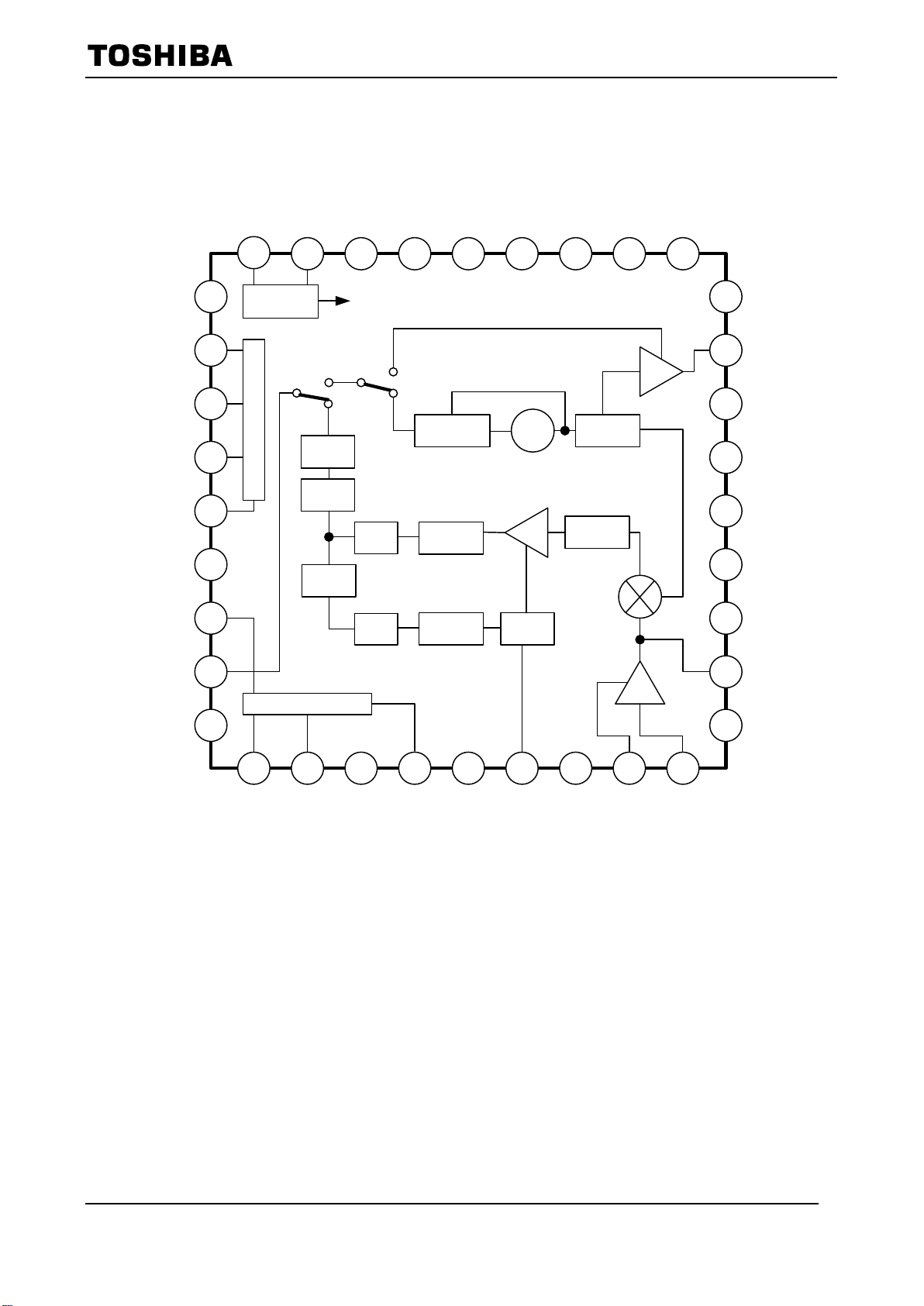

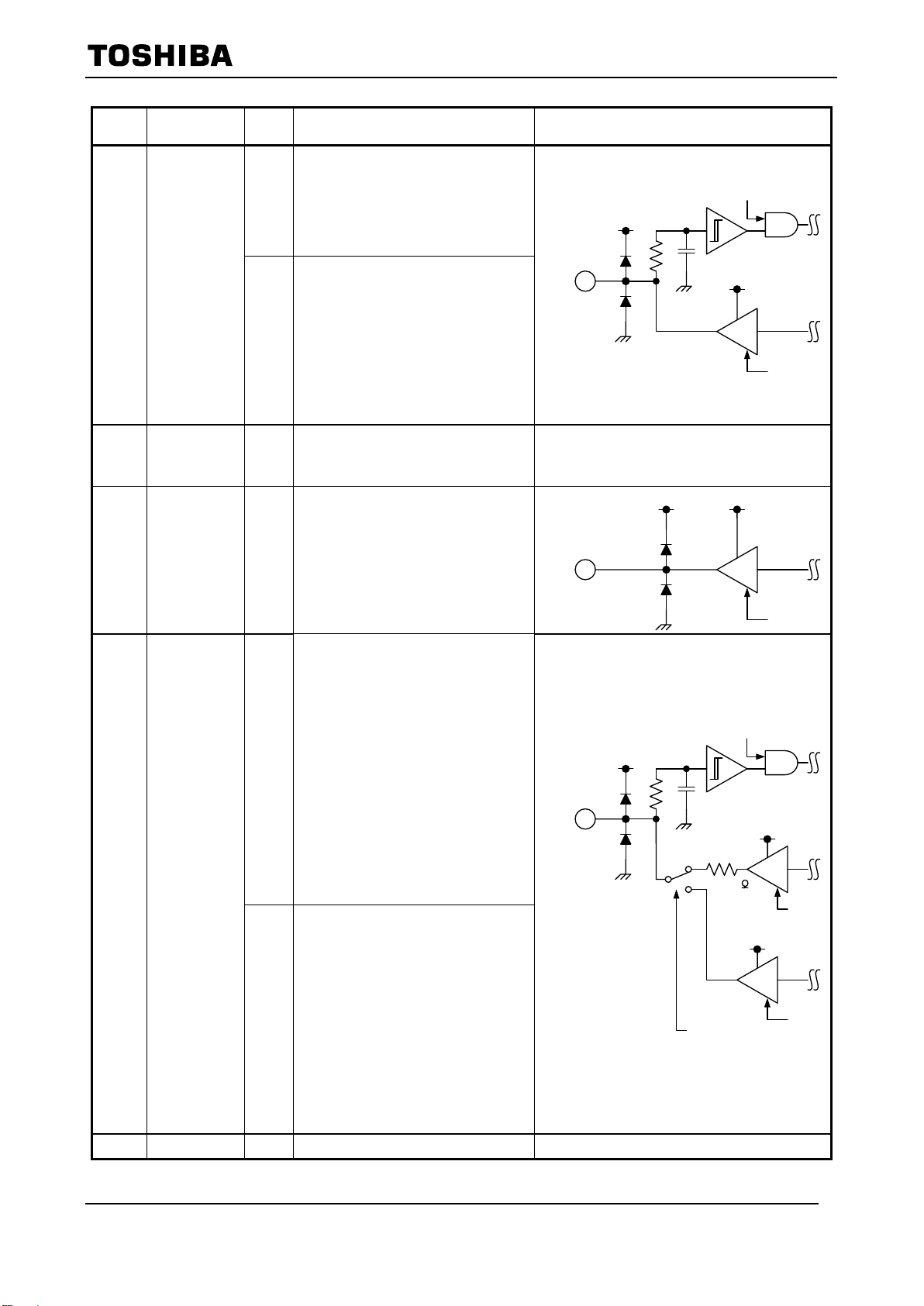

•Integrates LNA, Mixer, IF Filter, IF AMP, RSSI, Signal Detector, Bit Rate Filter, Data Comparator, PLL, VCO

and PA into a single IC.

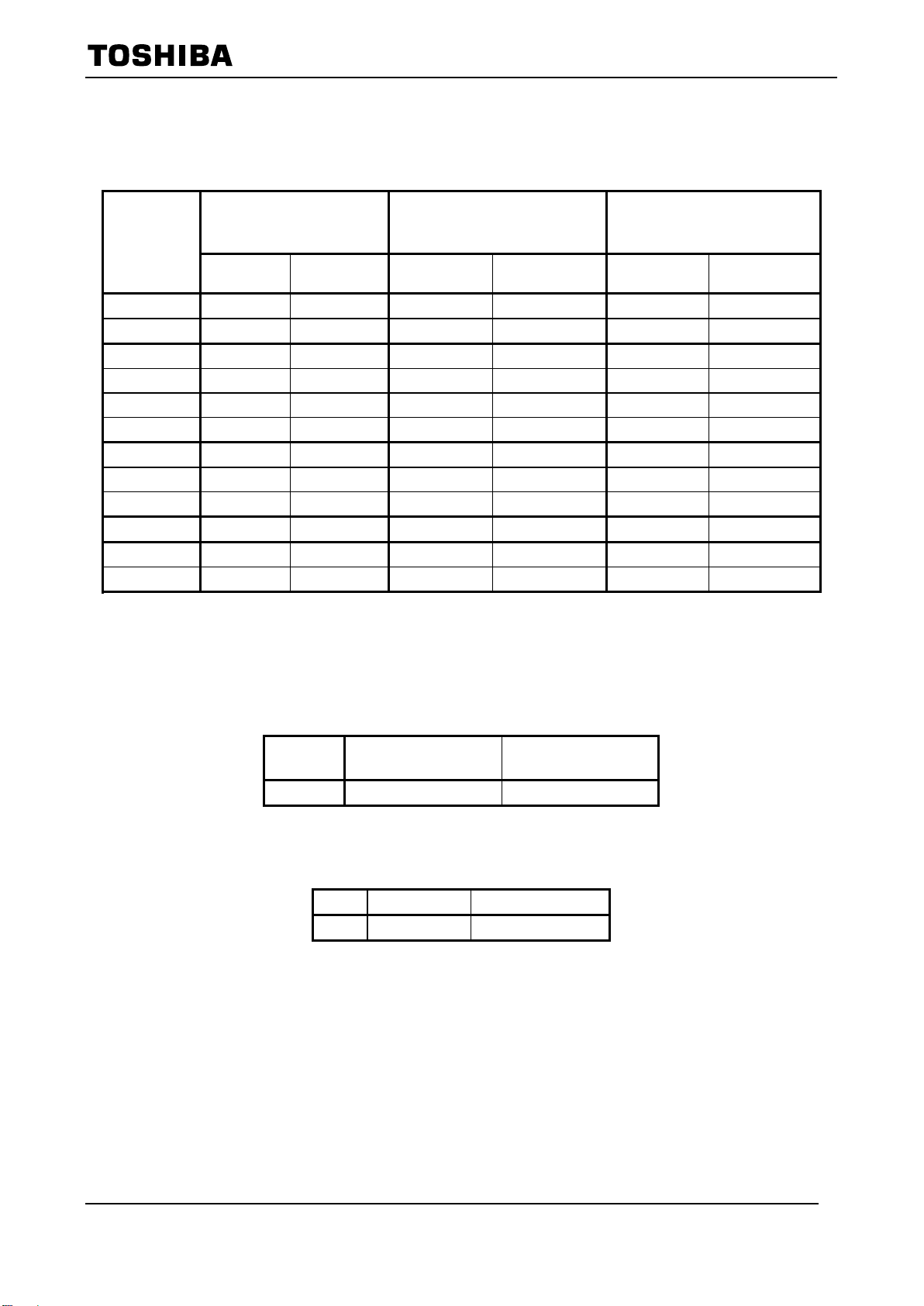

•Operating voltage range: 2.0 to 3.3 V (For 3V Use), 2.4V to 5.5V (For 5V Use)

•Current consumption: TX 12 mA at +10dBm output level / RX 9.7 mA / Battery Saving 0μA (typ.)

•Use for four RF Band: 315, 434, 868 / 915 MHz

•Supported modulation: ASK / FSK

•Single conversion system

•Two IF Filter bandwidth: wide 320kHz(typ.) at IF = 230kHz / middle 270kHz(typ.) at IF = 280kHz

•Signal Detections: RSSI detection, Noise detection (Only for FSK), Preamble detection

•Receiver sensitivity: under -116dBm (At IF BW = 320kHz, data rate = 600Hz, frequency deviation = +/-40kHz)

•Transmitter power: +10dBm (typ. at setting maximum output)

•Serial control (4 wire SPI) / EEPROM control

•Data Comparator Quick Charge / AutoOff Control / Antenna Switch Control