Board Hardware User Guide

2/21

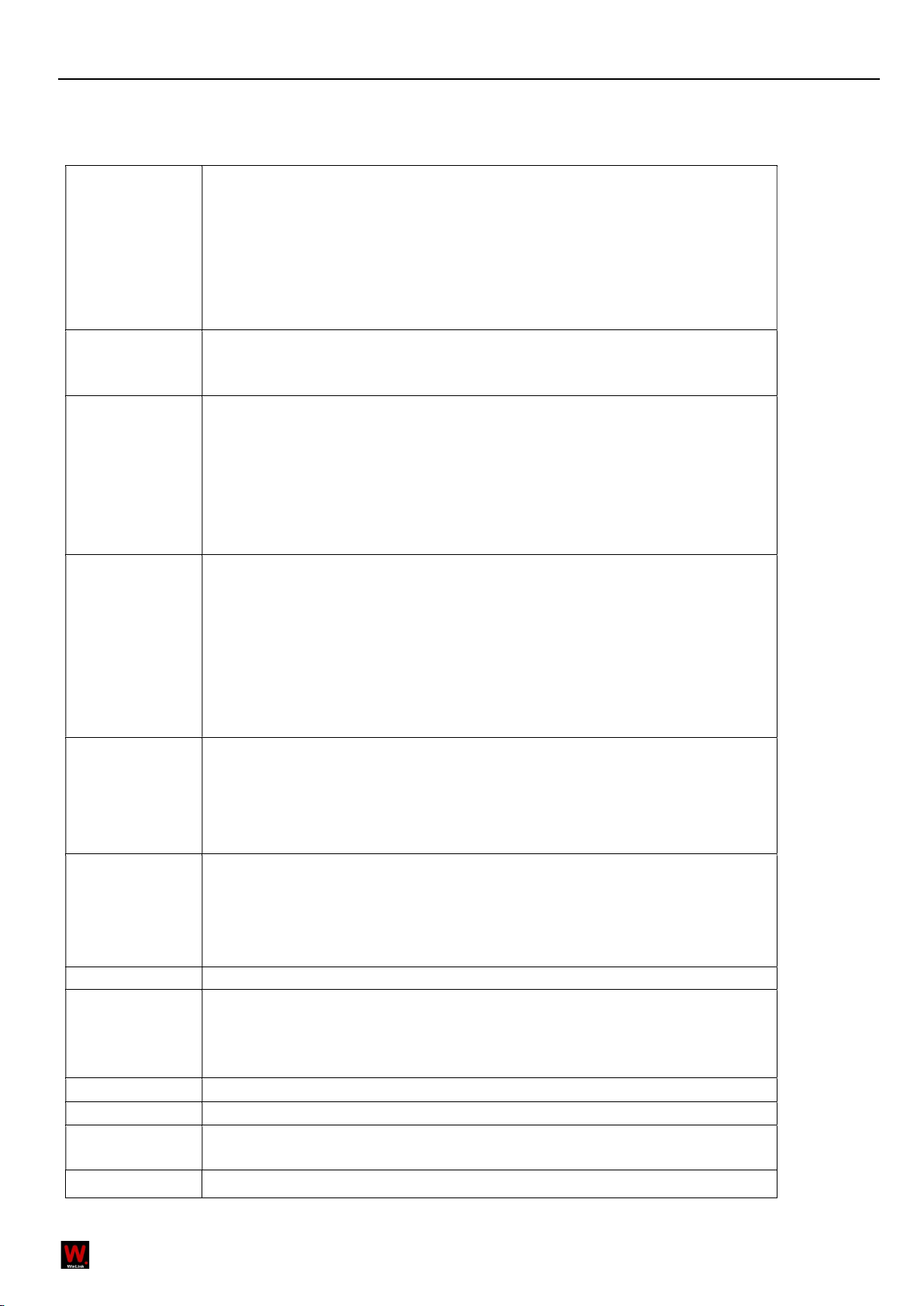

Table of Contents

Table of Contents .......................................................................................................................................................................... 2

Introduction .................................................................................................................................................................................. 3

What’s in the Box ......................................................................................................................................................................... 4

Board Overview ............................................................................................................................................................................ 5

Key Components ........................................................................................................................................................................... 6

System Block Diagram .................................................................................................................................................................. 7

Getting Started ............................................................................................................................................................................. 7

Prerequisites ......................................................................................................................................................................... 7

Starting the board for the first time ..................................................................................................................................... 7

Component Details ....................................................................................................................................................................... 8

Processor .............................................................................................................................................................................. 8

PMIC ..................................................................................................................................................................................... 8

Memory (DRAM) .................................................................................................................................................................. 8

Storage.................................................................................................................................................................................. 8

Micro SDHC ........................................................................................................................................................................... 8

Boot ROM ............................................................................................................................................................................. 8

Networking ........................................................................................................................................................................... 8

WiFi ....................................................................................................................................................................................... 8

Bluetooth .............................................................................................................................................................................. 9

HDMI .................................................................................................................................................................................... 9

MIPI-DSI ................................................................................................................................................................................ 9

Camera Interface .................................................................................................................................................................. 9

USB Ports .............................................................................................................................................................................. 9

USB Host ports.................................................................................................................................................................... 10

USB Device ports ................................................................................................................................................................ 10

Audio .................................................................................................................................................................................. 10

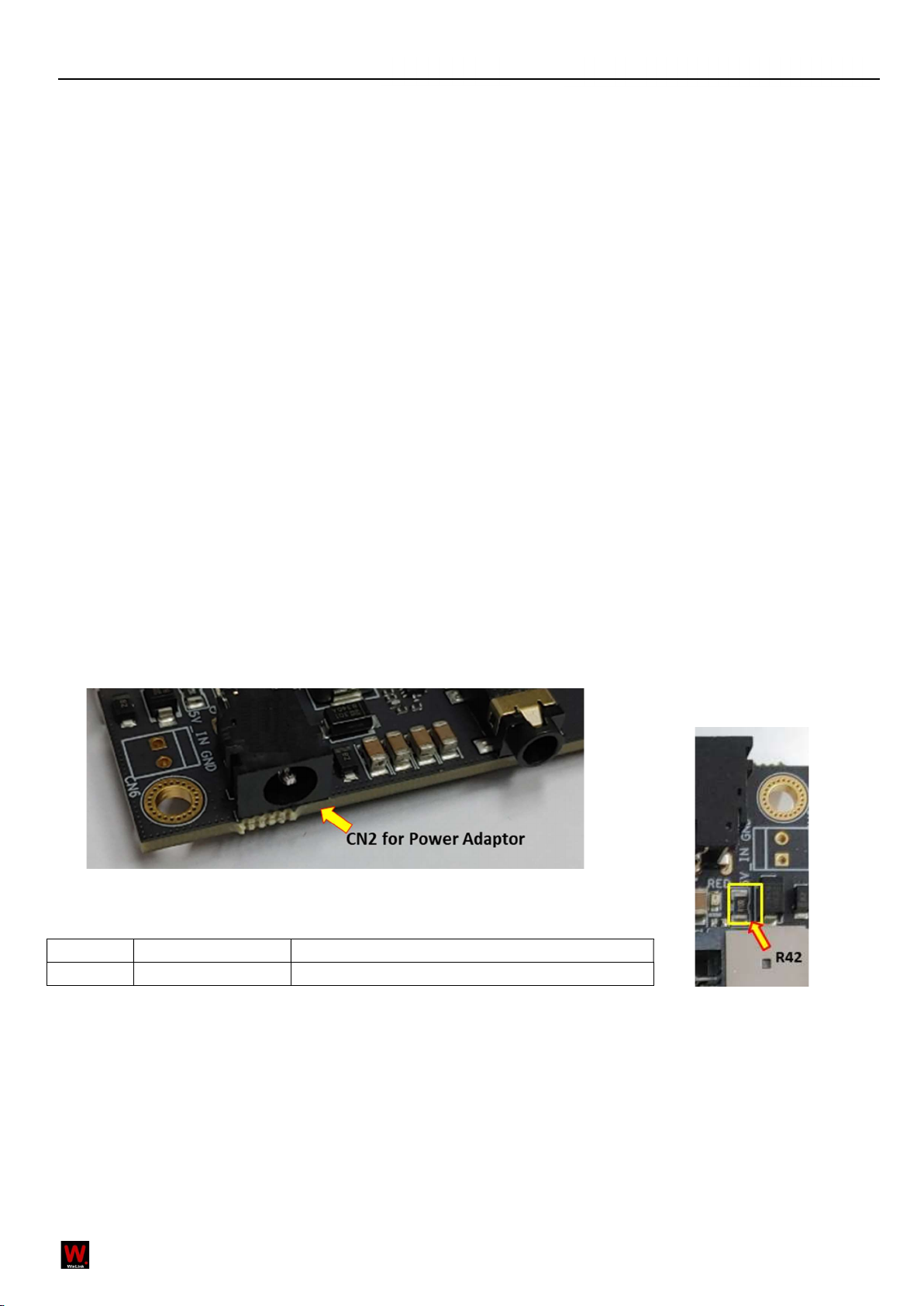

DC Power ............................................................................................................................................................................ 10

Power Measurement .......................................................................................................................................................... 10

UART ................................................................................................................................................................................... 10

Buttons ............................................................................................................................................................................... 11

LED Indicators ..................................................................................................................................................................... 12

Additional Functionality ..................................................................................................................................................... 12

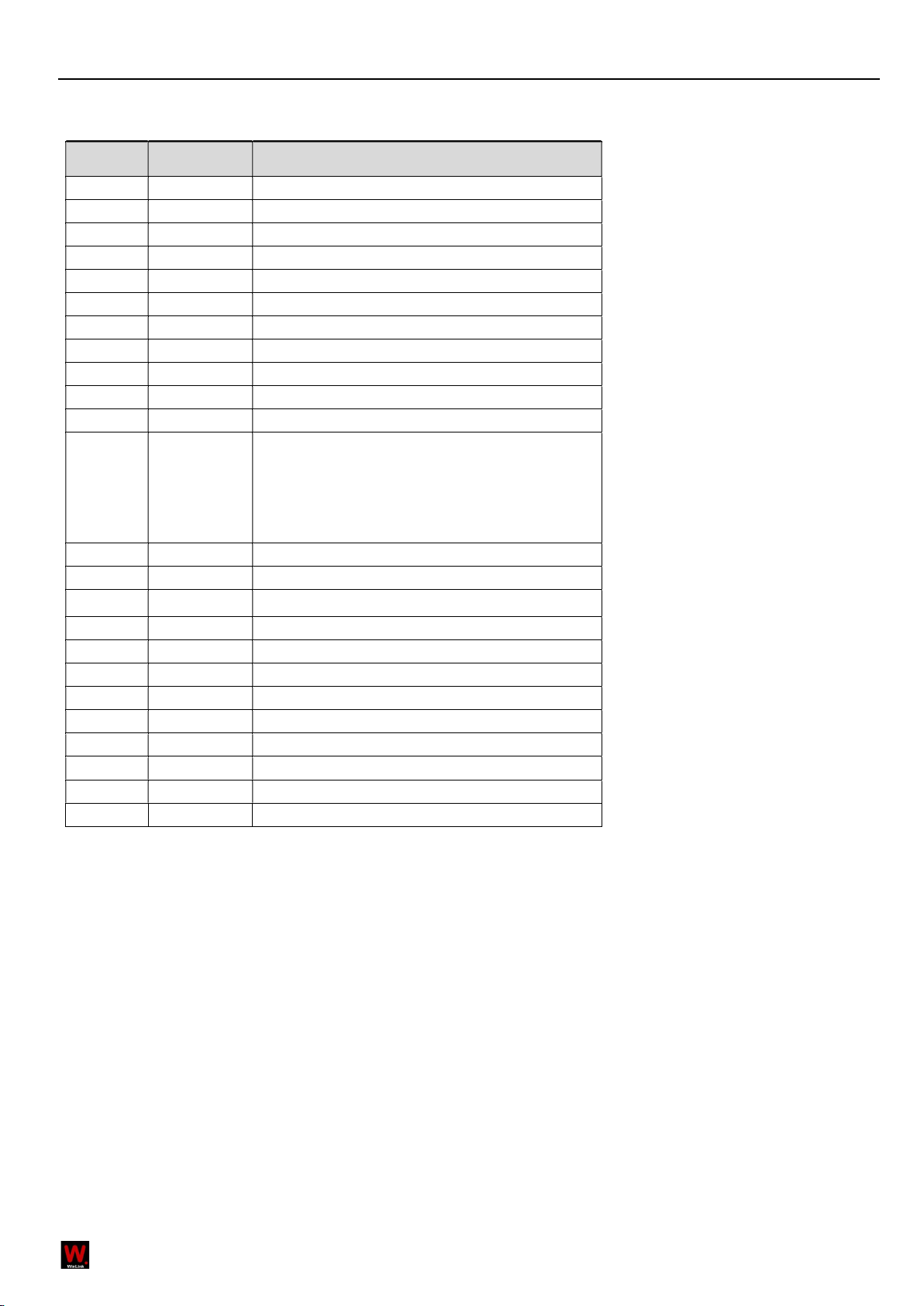

Expansion Connectors ................................................................................................................................................................ 14

Low Speed Expansion Connector ....................................................................................................................................... 14

High Speed Expansion Connector ...................................................................................................................................... 16

Audio Connector................................................................................................................................................................. 18

Power Management Overview ................................................................................................................................................... 19

Block Diagram ..................................................................................................................................................................... 19

DC Power Input ................................................................................................................................................................... 19

Voltage Rails ....................................................................................................................................................................... 20

Mechanical specification ............................................................................................................................................................ 21