Acorn Computers Limited Winchester disk 110 User manual

WINCHESTER DISC

110 & 130

SERVICE MANUAL

Part No 0427,001

Issu 1

August 1984

Within this publication th t rm 'BBC' is us d as an abbr viation for '

British Broadcasting Corporation'.

Copyright Acorn Comput rs Limit d 1984

N ith r th whol or any part of th information contain d in, or th product

d scrib d in, this manual may b adapt d or r produc d in any mat rial form

xc pt with th prior writt n approval of Acorn Comput rs Limit d (Acorn

Comput rs).

Th product d scrib d in this manual and products for us with it, ar

subj ct to continuous d v lopm nt and improv m nt. All information of a

t chnical natur and particulars of th product and its us (including th

information and particulars in this manual) ar giv n by Acorn Comput rs in

good faith. How v r, it is acknowl dg d that th r may b rrors or omissions

in this manual. A list of d tails of any am ndm nts or r visions to this

manual can b obtain d upon r qu st from Acorn Comput rs T chnical Enquiri s.

Acorn Comput rs w lcom comm nts and sugg stions r lating to th product and

this manual.

All corr spond nc should b addr ss d to:-

T chnical Enquiri s

Acorn Comput rs Limit d

N wmark t Road

Cambridg

CB5 8PD

All maint nanc and s rvic on th product must b carri d out by Acorn

Comput rs' authoris d d al rs. Acorn Comput rs can acc pt no liability

whatso v r for any loss or damag caus d by s rvic or maint nanc by

unauthoris d p rsonn l. This manual is int nd d only to assist th r ad r in

th us of this product, and th r for Acorn Comput rs shall not b liabl

for any loss or damag whatso v r arising from th us of any information or

particulars in, or any rror or omission in, this manual, or any incorr ct

us of th product.

This manual is for th sol us of Acorn Comput rs' authoris d d al rs and

must only b us d by th m in conn ction with th product d scrib d within.

ACORN and ECONET ar trad marks of ACORN Comput rs Limit d.

First publish d 1984

Publish d by Acorn Comput rs Limit d

WINCHESTER DISC SERVICE MANUAL

Cont nts pag

1 Introduction 1

2 Packaging and installation 2

3 Sp cification 3

3.1 Disc driv 3

3.2 ADAPTEC ACB-4000 Winch st r disc controll r 3

3.3 Host Adapt r 3

3.4 Pow r supply 3

3.5 Environm ntal 4

3.6 Outsid dim nsions 4

3.7 Conn ctions 4

4 Disass mbly and ass mbly 5

5 Circuit d scription 8

5.1 Th disc controll r board 8

5.1.1 SCSI control and data lin s 9

5.1.2 SCSI conn ctor pinout (PL2 and J4) 10

5.1.3 Bus phas s 10

5.1.4 Th r s t condition 12

5.1.5 Th ST-412 disc int rfac conn ctor pinouts (J2 and J0) 13

5.2 Th 1MHz xpansion bus 14

5.2.1 Control, addr ss and data lin s 14

5.2.2 Conn ctor pinout 14

5.3 Winch st r Disc Host Adapt r 15

5.3.1 Addr ss d coding and handshaking 15

5.3.2 Buff ring 16

5.3.3 T rmination 16

6 T st quipm nt and formatting 17

7 Fault finding 18

7.1 Pow r supply 18

7.2 Addr ss d coding 19

7.2.1 &FC40 r ad data 19

7.2.2 &FC40 writ data 19

7.2.3 &FC41 r ad status 20

7.2.4 &FC42 writ s l ct 20

7.2.5 &FC43 writ IRQ nabl 21

7.3 Handshaking 21

7.4 Bus lin s 22

App ndix

Host Adapt r PCB circuit diagram 25

Winch st r Disc unit block diagram 27

Winch st r Disc unit parts list 28

Winch st r Disc unit ass mbly diagram 29

Winch st r Disc unit wiring diagram 31

LED conn ction diagram 33

Winch st r Disc Host Adapt r parts list 34

Host Adapt r PCB ass mbly diagram 35

WARNING: THE WINCHESTER DISC UNIT MUST BE EARTHED

IMPORTANT: Th wir s in th mains l ad for th apparatus ar colour d in

accordanc with th following cod :

GREEN & YELLOW - EARTH

BLUE - NEUTRAL

BROWN - LIVE

As th colours of th wir s may not corr spond with th colour d markings

id ntifying th t rminals in your plug, proc d as follows:

Th wir which is colour d gr n and y llow must b conn ct d to th t rminal

in th plug which is mark d by th l tt r E, or by th saf ty arth symbol ±

, or colour d ith r gr n or gr n and y llow.

Th wir which is colour d blu must b conn ct d to th t rminal which is

mark d by th l tt r N, or colour d black.

Th wir which is colour d brown must b conn ct d to th t rminal which is

mark d by th l tt r L, or colour d r d.

If th sock t outl t availabl is not suitabl for th plug suppli d, th plug

should b cut off and th appropriat plug fitt d and wir d as pr viously

not d. Th mould d plug which was cut off must b dispos d of as it would b

a pot ntial shock hazard if it w r to b plugg d in with th cut off nd of

mains cord xpos d.

Th mould d plug must b us d with th fus and th fus carri r firmly in

plac . Th fus carri r is of th sam basic colour* as th colour d ins rt in

th bas of th plug. Diff r nt manufactur rs' plugs and fus carri rs ar not

int rchang abl . In th v nt of loss of th fus carri r th mould d plug

MUST NOT b us d. Eith r r plac th mould d plug with anoth r conv ntional

plug wir d as pr viously d scrib d, or obtain a r plac m nt fus carri r from

an Acorn Comput rs authoris d d al r. In th v nt of th fus blowing, it

should b r plac d, aft r cl aring any faults, with a 5 amp fus that is ASTA

approv d to BS 1362.

*Not n c ssarily th sam shad of that colour.

1. Introduction

This manual is int nd d to provid th information r quir d to

diagnos and r pair faults on th Winch st r Disc unit which was

d sign d by Acorn Comput rs Limit d of Cambridg , England.

Th only d al r-s rvic abl part of th Winch st r Disc unit is th

Host Adapt r print d circuit board. Faults d t ct d in th disc

driv , disc controll r board, or pow r supply m an that th faulty

part must ith r b r turn d for r pair or r plac d. D al rs may hold

stock of th s it ms and should r f r to information provid d by th ir

suppli r for s rvic proc dur s for th s units.

Th information contain d in this manual is aim d at s rvic ngin rs

and Acorn d al rs who will b s rvicing th Winch st r Disc unit on

b half of Acorn Comput rs Ltd.

1

2. Packaging and installation

Th Winch st r Disc unit is suppli d fitt d with two xpand d poly thyl n

nd pi c s in a corrugat d card box. Suppli d with th Winch st r Disc unit

is a Us r Guid , a ROM lab ll d ADFS, a mains l ad, a 1MHz bus l ad and a

guarant card which ar all pack d in a card tray locat d in th top of th

box.

Th ADFS ROM must b plugg d into on of th host microcomput r's sid ways

ROM sock ts, or th Winch st r filing syst m will not work.

Th Winch st r Disc unit must b conn ct d to a 240V AC 50Hz supply via th

mains l ad provid d and th sock t at th r ar of th unit.

A mains pow r switch is locat d at th r ar of th unit.

A 3.15A typ F fus is locat d in a hold r b n ath th mains sock t at th

r ar of th unit.

Th Winch st r Disc unit must b conn ct d to th host microcomput r's 1MHz

xpansion bus sock t using th ribbon cabl provid d.

Th r is a gr n activity lamp on th front pan l which illuminat s wh n th

driv is b ing acc ss d.

Th Winch st r unit is fragil , and must not b subj ct d to any shock. Do not

us th unit in conditions of xtr m h at, cold, humidity or dust or in

plac s subj ct to vibration. Do not block v ntilation in front of or b hind

th unit, sp cially th fan intak at th r ar. Ensur that no for ign

obj cts ar ins rt d through any op nings in th cas . Do not mov th unit

whil it is op rating.

Th unit must b transport d in its original packing, which must b r tain d

for futur us .

2

3. Sp cification

Th Winch st r Disc unit provid s storag and r tri val of data and programs

on non-r movabl magn tic discs. This can b local storag for a

microcomput r such as th BBC Microcomput r mod l B or as a fil s rv r for an

ACORN ECONET local ar a n twork.

Th Winch st r Disc unit consists of a 10 Mbyt (mod l 110) or 30 Mbyt (

mod l 130) hard disc driv , an ADAPTEC ACB-4000 Winch st r Disc Controll r,

an Acorn Host Adapt r Board which is an int rfac b tw n th ACB-4000 and th

host comput r's 1 MHz xpansion bus, and a pow r supply unit. Th unit also

contains a 240V AC fan for cooling.

3.1 Disc driv

Capacity 10M (mod l 110) or 30M (mod l 130) formatt d

Format ADAPTEC 33 s ctors of 256 byt s

Cylind rs 306 (10M v rsion)

H ads 4 (10M v rsion)

Disc rpm 3600

3.2 ADAPTEC ACB-4000 Winch st r disc controll r

Disc int rfac ST-412

Host int rfac SCSI

3.3 Host Adapt r

SCSI to 1 MHz xpansion bus

3.4 Pow r supply

Minimum input voltag 198V AC

Maximum input voltag 264V AC

Supply fr qu ncy 47 to 53Hz

+5V output voltag 4.9 to 5.2V

+5V output curr nt 0.7 to 3.5A

+5V ov rvoltag prot ction 5.8 to 7.0V

+5V ov rcurr nt prot ction 5.0A

+12V output voltag 11.4 to 12.6V

+12V output curr nt 0.6 to 3.0A

+12V surg output curr nt 5A for 15 s conds

+12V ov rvoltag prot ction 13.0 to 16.0V

+12V ov rcurr nt prot ction 6.0A

3

3.5 Environm ntal

Minimum op rating t mp ratur 0 d gr s C

Maximum op rating t mp ratur +37 d gr s C

Minimum storag t mp ratur -30 d gr s C

Maximum storag t mp ratur +60 d gr s C

Maximum op rating humidity 80% RH at 35 d gr s C

Maximum storag humidity 80% RH at 55 d gr s C

Op rating altitud 0 to 1800 m tr s abov s a l v l

Storag altitud 0 to 3500 m tr s abov s a l v l

Th rmal gradi nt 10 d gr s C p r hour

Op ration lif tim 50,000 hours

M an tim b for failur 10,000 hours of typical usag

3.6 Outsid dim nsions

h ight 100mm (108mm including f t)

width 335mm

d pth 365mm

3.7 Conn ctions

Two 37 way D-typ sock t conn ctors ar provid d for 1MHz bus daisy chain

conn ction. Th s ar on th r ar pan l and ar lab ll d '1MHz bus IN' and '

OUT', although th y ar in fact id ntical. Thr r movabl r sistor packs ar

mount d on th Host Adapt r PCB insid th cas for 1MHz bus t rmination.

Th s packs ar fitt d as standard, but n d b r tain d only in th last

unit in th daisy chain.

Also on th r ar pan l is an IEC plug for mains pow r input.

4

4. Disass mbly and ass mbly

Warning: wh n th Winch st r Disc unit is mov d or work d upon, gr at car

must b tak n not to drop, jar or shock th unit in any way. If th hard disc

is brok n through car l ss handling th n th unit is uns rvic abl .

i) Ensur that th unit is disconn ct d from th mains pow r supply b for

dismantling it.

ii) To s rvic th Host Adapt r PCB, r mov th thr small phillips scr ws

lab ll d A in figur 1, und rn ath th front of th unit which hold on th

front pan l.

(Th unit may b turn d on its back to do this if d sir d, but th n r m mb r

that r f r nc s to l ft and right in th following d scription will b

r v rs d.)

Figur 1 Scr ws to r mov

5

iii) Ins rt a hook through th grill on th front pan l to th l ft sid and

pull th front pan l until th th conn ction to th light mitting diod (

LED) is visibl . Pull th conn ctor off th light mitting diod and mak a

not of which way round it was fitt d. R mov th front pan l compl t ly.

iv) Undo th six small phillips scr ws lab ll d B in figur 1, which conn ct

th bottom pan l to th top pan l.

(If th unit was turn d on its back to gain acc ss to th scr ws on th

bottom pan l, now turn it back th right way up.)

v) R mov th singl small phillips scr w lab ll d C in figur 1, from th

r ar pan l (middl top n ar th ribbon cabl ).

vi) Slid th top cov r forward and off, b ing car ful not to g t any of th

cabl s or compon nts caught in it. (Th lug which was locat d by th scr w in

th r ar pan l will usually b com caught in th int rnal cabling during this

proc ss.)

vii) Th back pan l can b l ft in plac .

viii) Two PCBs ar now visibl to th front l ft of th unit, on abov th

oth r, s figur 2.

Figur 2 Vi w from l ft sid

6

If it is n c ssary to t st th Host Adapt r (th low r PCB) with th syst m

running th n th top board can b r mov d with all its cabl conn ctions in

plac . Alt rnativ ly, th conn ctors can b unplugg d to as r moval of th

board and th n r conn ct d again aft rwards.

R mov th top board by undoing th four phillips scr ws which hold th PCB

on its four plastic pillars. Th Host Adapt r PCB is th low r board and may

b work d upon without r moval. If it is n c ssary to r plac th Host

Adapt r PCB th n it can b r mov d in th sam way as th top board.

ix) No furth r disass mbly must b carri d out. Th cov r of th hard disc

driv unit must NOT b r mov d.

R v rs th abov proc dur to r ass mbl th unit. Do not forg t to

r conn ct th LED cabl at iii) b for r locating th front pan l.

Not : th LED conn ctor must b conn ct d th corr ct way round or th LED

will not function.

7

5. Circuit d scription

Th only part of th Winch st r Disc unit which is s rvic abl by Acorn

d al rs is th Host Adapt r PCB (s app ndix for circuit diagram) and its

conn ctors and cabl s tc. This is an int rfac b tw n th asynchronous SCSI

int rfac to th disc controll r board, and th synchronous 1MHz xpansion bus

int rfac on th host microcomput r us d by th Winch st r Disc filing

syst m. Th following circuit d scription will provid nough information

about th disc controll r board and th 1MHz xpansion bus to allow a full

und rstanding of th op ration of th Host Adapt r board. For th full

sp cification of th SCSI int rfac s th r l vant lit ratur .

5.1 Th disc controll r board

Th disc controll r us d in th Winch st r Disc unit is a d vic which will

s nd or acc pt parall l (byt ) data to or from th host microcomput r (via

1MHz bus and Host Adapt r), and will r ad or writ this data s rially to or

from th hard disc. It contains a 256 byt cach m mory (h r aft r r f rr d to

as th "s ctor m mory" b caus 1 disc s ctor = 256 byt s). A conn ction

diagram for th disc controll r board is giv n in figur 3 b low.

Figur 3 Disc controll r board conn ction diagram

8

In th following d scription, th Host Adapt r is known as th "initiator",

and th disc controll r is known as th "targ t".

5.1.1 SCSI control and data lin s

Th 8 control and 8 data lin s on th SCSI sid of th controll r (shown on

th right sid of th Host Adapt r circuit diagram in th app ndix) ar all

activ -low op n coll ctor, and ar as follows:

SELECT (SEL, pin 44) is an op n coll ctor signal which is ass rt d by th

initiator as th first st p in any transf r of data through th int rfac .

BUSY (BSY, pin 36) is an op n coll ctor signal which is ass rt d by th

targ t to indicat that th data bus is in us . This is th first r spons of

th targ t to th initiator's ass rtion of SEL, and th SEL/BSY handshak is

th first communication in any Winch st r filing syst m op ration.

CONTROL/DATA (C/D, pin 46) is ass rt d by th targ t wh n th bus carri s

control information, and is d ass rt d wh n th bus carri s data.

INPUT/OUTPUT (I/O, pin 50) controls th dir ction of data flow, and is

ass rt d by th targ t to indicat input to th initiator (disc to comput r),

and is d ass rt d to indicat output to th targ t (comput r to disc).

REQUEST (REQ, pin 48) is ass rt d by th targ t to indicat a r qu st for a

REQ/ACK data transf r handshak .

ACKNOWLEDGE (ACK, pin 38) is ass rt d by th initiator to indicat

acknowl dg m nt of a REQ/ACK data transf r handshak . Th REQ/ACK handshak

provid s th asynchronous timing of all data transf r b tw n initiator and

targ t.

RESET (RST, pin 40) is ass rt d by th initiator on pow r-up and wh n th host

microcomput r's BREAK k y is pr ss d. It caus s th "r s t condition" (s 5.

1.3) which imm diat ly cl ars th bus and r s ts th syst m.

MESSAGE (MSG, pin 42) is ass rt d by th targ t wh n it issu s a m ssag byt

to notify compl tion of a command, s 5.1.2.

DATA BUS (DB0 to DB7, pins 2 4 6 8 10 12 14 and 16) is a parall l data bus

consisting of 8 signals from DBO (l ast significant) to DB7 (most significant)

. 1 byt of information is transf rr d across th bus with ach REQ/ACK

handshak . It is important to r m mb r that th data lin s ar activ -low and

th r for ar inv rt d in both dir ctions wh n communicating with th host

microcomput r.

All odd numb r d pins ar OV, and pin 34 is +5V.

9

5.1.2 SCSI conn ctor pinout (PL2 and J4)

Pin no

0V 1 2 DB0

0V 3 4 DB1

0V 5 6 DB2

0V 7 8 DB3

0V 9 10 DB4

0V 11 12 DB5

0V 13 14 DB6

0V 15 16 DB7

0V 17 18 }

0V 19 20 }

0V 21 22 }

0V 23 24 } For futur xpansion

0V 25 26 }

0V 27 28 }

0V 29 30 }

0V 31 32 }

0V 33 34 +5V to supply t st quipm nt

0V 35 36 BSY

0V 37 38 ACK

0V 39 40 RST

0V 41 42 MSG

0V 43 44 SEL

0V 45 46 C/D

0V 47 48 REQ

0V 49 50 I/O

5.1.3 Bus phas s

Th bus has s v ral distinct op rational phas s and cannot b in mor than

on of th s phas s at any giv n tim .

Bus phas s occur in a pr scrib d s qu nc . Th r s t condition can int rrupt

any phas and is always follow d by bus fr . Any oth r phas can also b

follow d by th bus fr phas .

Th pr scrib d s qu nc is from bus fr to s l ction to on or mor of th

information transf r phas s to bus fr again.

Th r ar no r strictions on th ord r of information transf r phas s, and a

phas will oft n follow its lf, g two data phas s on aft r th oth r.

A typical s qu nc would b :

bus fr

s l ct controll r - s l ction phas

transf r command byt s - command phas

transf r data byt s (if n c ssary) - data in/out phas

status phas

m ssag phas

10

Th phas s ar as follows:

Bus fr phas : indicat s that th bus is availabl for us . Th bus fr

phas is indicat d by all control signals d scrib d in s ction 5.1.1 b ing

d ass rt d. If SEL and BSY and RST ar not ass rt d, that is suffici nt to

guarant bus fr .

S l ction phas : allows th initiator to s l ct th targ t. Aft r d t cting

bus fr , th initiator ass rts SEL. Th targ t d t cts SEL ass rt d, and BSY

and I/O d ass rt d, and r sponds by ass rting BSY. Th initiator d ass rts

SEL and may th n chang th data signals.

Information transf r phas s: allow transf r of information across th bus.

Th r ar s v ral diff r nt typ s of information transf r phas , and th typ

is d t rmin d by MSG, C/D and I/O. Tabl 1 shows th information transf r

phas s:

SIGNALS DIRECTION OF

MSG C/D I/O PHASE NAME INFORMATION TRANSFER

1 1 1 data out phas initiator to targ t

1 1 0 data in phas targ t to initiator

1 0 1 command phas initiator to targ t

1 0 0 status phas targ t to initiator

0 0 1 m ssag out phas initiator to targ t (not us d)

0 0 0 m ssag in phas targ t to initiator

All signals activ -low: 0=ass rtion

1=d ass rtion

Tabl 1 Information transf r phas s

Th information transf r phas s us th REQ/ACK handshak to control

information transf r: ach REQ/ACK allows th transf r of 1 byt . Th

handshak s qu nc is:

1- targ t ass rts REQ to r qu st data transf r

2- initiator ass rts ACK wh n data is valid on bus

3- targ t d ass rts REQ wh n data has b n transf rr d

4- initiator d ass rts ACK r ady for n xt handshak

Prior to and during information transf r, th I/O signal d t rmin s th

dir ction of th transf r as can b s n in Tabl 1.

B for ach information transf r phas th targ t will s t up th MSG, C/D and

I/O lin s in such a way that th s control signals ar stabl for 450ns b for

th REQ of th first handshak , and r main valid until th d ass rtion of ACK

at th nd of th last handshak .

During ach information transf r phas th BSY lin r mains ass rt d and SEL

d ass rt d.

11

Each information transf r phas is as follows:

Command phas : allows th initiator to dir ct th subs qu nt action of th

targ t by transf rring command byt s. Th targ t ass rts C/D and d ass rts MSG

and I/O.

Status phas : allows th initiator to r ad th targ t's status information.

Th targ t ass rts C/D and I/O and d ass rts MSG.

Data out phas : allows data to b transf rr d from initiator to targ t. Th

targ t d ass rts MSG, C/D and I/O.

Data in phas : allows data to b transf rr d from targ t to initiator. Th

targ t ass rts I/O and d ass rts MSG and C/D.

M ssag out phas : not us d by th syst m - availabl for futur xpansion.

M ssag in phas : allows th targ t to s nd a m ssag byt to notify

compl tion of a command.

5.1.4 Th r s t condition

Th r s t condition is caus d by th ass rtion of RST, and imm diat ly cl ars

th bus and r s ts th syst m. R gardl ss of th prior bus phas , th bus

r s ts to th bus fr phas . Th Winch st r controll r r ads th driv 's

param t rs off th disc.

R s t can occur at any tim and tak s pr c d nc ov r all oth r phas s and

conditions. In practic it occurs on pow r-up or wh n th BREAK k y is

pr ss d.

12

5.1.5 Th ST-412 disc int rfac conn ctor pinouts (J2 and JO)

Th disc controll r board communicat s with th Winch st r disc via two

conn ctors: J2 carri s control information, and J0 carri s data. J1 is not

us d in this impl m ntation, but is l ctrically id ntical to J0.

J2 Pin no

0V 1 2 READ/WRITE CURRENT HEAD 2^3

0V 3 4 HEAD SELECT 2^2

0V 5 6 WRITE GATE

0V 7 8 SEEK COMPLETE 0V 9 10 TRACK 0

0V 11 12 WRITE FAULT

0V 13 14 HEAD SELECT 2^0 0V 15 16 RESERVED

0V 17 18 HEAD SELECT 2^1 0V 19 20 INDEX

0V 21 22 READY

0V 23 24 STEP

0V 25 26 DRIVE SELECT 1

0V 27 28 DRIVE SELECT 2

0V 29 30 DRIVE SELECT 3

0V 31 32 DRIVE SELECT 4

0V 33 34 DIRECTION IN

J0 Pin no

DRIVE SELECTED 1 2 0V

RESERVED 3 4 0V

RESERVED 5 6 0V

RESERVED 7 8 0V

RESERVED 9 10 RESERVED

0V 11 12 0V

+MFM WRITE DATA 13 14 -MFM WRITE DATA

0V 15 16 0V

+MFM READ DATA 17 18 -MFM READ DATA

0V 19 20 0V

Th r ad and writ MFM data lin s (pins 13 14 17 and 18 of J0) ar

diff r ntial signals.

13

5.2 Th 1MHz xpansion bus

Th following is a d scription of th 1MHz xpansion bus signals us d by th

Winch st r Disc Host Adapt r, and th ir function as appli d to th Winch st r

Disc syst m. For a full d scription of th 1MHz xpansion bus s "BBC

Microcomput r Application Not Numb r 1 - 1MHz Bus", part numb r 0407,000,

publish d by Acorn Comput rs Limit d.

5.2.1 Control, addr ss and data lin s

1MHzE (syst m 1MHz, pin 4) is a continuously running 1MHz timing signal.

During acc ss to th 1MHz bus, th proc ssor clock (normally 2MHz) is

str tch d so that th trailing dg s of 1MHzE and th proc ssor clock ar

synchronis d.

R/NW (r ad/not-writ , pin 2) is th syst m r ad/writ lin .

NIRQ (not-IRQ, pin 8) is th int rrupt r qu st lin which is op n coll ctor

and ass rt d by a d vic pulling it low. IRQ is l v l trigg r d activ -low.

NRST (not-r s t, pin 14) is output only activ -low syst m r s t lin . It is

activ on pow r-up and wh n th BREAK k y is pr ss d.

NPGFC (not-pag &FC, pin 10) is a signal d cod d from th top 8 syst m addr ss

lin s (A8 to A15). NPGFC is an activ -low signal which is low wh n th addr ss

high byt is &FC, i wh n th full addr ss is &FC00 to &FCFF. Four locations

in this rang ar us d by th Winch st r syst m: &FC40 to &FC43 inclusiv , s

7.2.

A0 to A7 (addr ss low, pins 27 to 34) ar th bottom 8 syst m addr ss lin s.

D0 to D7 (syst m data bus) ar th bi-dir ctional data lin s. Dir ction

d t rmin d by R/NW. Th data lin s ar buff r d, and th buff r nabl d only

wh n NPGFC is activ .

Pins 1 3 5 7 9 11 13 15 17 and 26 ar 0V. 5.2.

2 Conn ctor pinout

TOP Pin No BOTTOM

0V 1 2 R/NW

0V 3 4 1MHzE

0V 5 6 For oth r applications

0V 7 8 NIRQ

0V 9 10 NPGFC

0V 11 12 For oth r applications

0V 13 14 NRST

0V 15 16 For oth r applications

0V 17 18 D0

D1 19 20 D2

D3 21 22 D4

D5 23 24 D6

D7 25 26 0V

A0 27 28 Al

A2 29 30 A3

A4 31 32 A5

A6 33 34 A7

14

5.3 Winch st r Disc Host Adapt r

In conjunction with th following d scription, r f r nc should b mad to th

Winch st r Disc Host Adapt r circuit diagram in th App ndix.

Th Winch st r Disc Host Adapt r is an int rfac b tw n th SASI/SCSI

int rfac and th 1MHz xpansion bus. It consists of addr ss d coding and

handshak control, buff ring of th signals in ith r dir ction, and

t rmination.

5.3.1 Addr ss d coding and handshaking

Th Host Adapt r d cod s 4 locations in th host microcomput r's pag FC I/O

spac . Th s four locations ar as follows:

Addr ss R ad Writ

&FC4O data data (dir ction d t rmin d by R/NW)

&FC41 status ---

&FC42 s l ct

&FC43 nabl IRQ

Pag FC is d cod d in th host microcomput r and this is availabl to th Host

Adapt r as NPGFC (not-pag FC). NPGFC is synchronis d with 1MHzE by th d -

glitch circuit (half of IC10) and th cl an signal is lab ll d CNPGFC (pin 5,

IC10).

Th low ord r addr ss lin s A0 to A7 ar buff r d through IC5.

IC6, a 3 to 8 lin d cod r with thr nabl inputs, d cod s th low ord r

addr ss s &4O to &43, i output pin 15 go s low wh n th low ord r addr ss is

&40, &41, &42 or &43.

IC7 is anoth r 3 to 8 lin d cod r which tak s th output from IC6 and CNPGFC

and 1MHzE as nabl inputs. Th 2 l ast significant addr ss bits A0 and Al ar

d cod d along with R/NW into th r quir d 5 s parat signals shown abov .

Y0 (pin 15) is r ad data (R/NW = 1)

Y4 (pin 11) is writ data (R/NW = 0)

Y1 (pin 14) is status

Y6 (pin 9) is s l ct

Y7 (pin 7) is nabl IRQ

All th s outputs ar activ -low.

Wh n ith r of th two data transf r paths is s l ct d (Y0 or Y4) an ACK

signal is g n rat d by clocking a D-typ flip-flop (half of IC11). This flip-

flop is cl ar d dir ct from th REQ lin , and thus th REQ/ACK handshak is

facilitat d.

Th oth r half of IC11 facilitat s th SEL/BSY handshak . Th D-typ is

clock d by Y6 to g n rat s l ct and is cl ar d by BSY.

Wh n Y7 is s l ct d, th l ast significant bit on th data bus (D0) is clock d

into a D-typ flip-flop (half of IC10). If this valu is a 1 th n th latch (2

NANDs of IC12) is nabl d and an IRQ will b g n rat d at th n xt falling

dg of REQ. To disabl int rrupts Y7 is

s l ct d with a 0 on D0. IRQs ar nabl d only for a v ry short tim (around

10ms) wh n nsuring a s qu ntial fil buff r.

15

This manual suits for next models

1

Table of contents

Other Acorn Computers Limited Computer Hardware manuals

Popular Computer Hardware manuals by other brands

Tews Technologies

Tews Technologies TAMC261 user manual

ekwb

ekwb EK-Pro GPU WB RTX 4000 - Ni + Inox installation manual

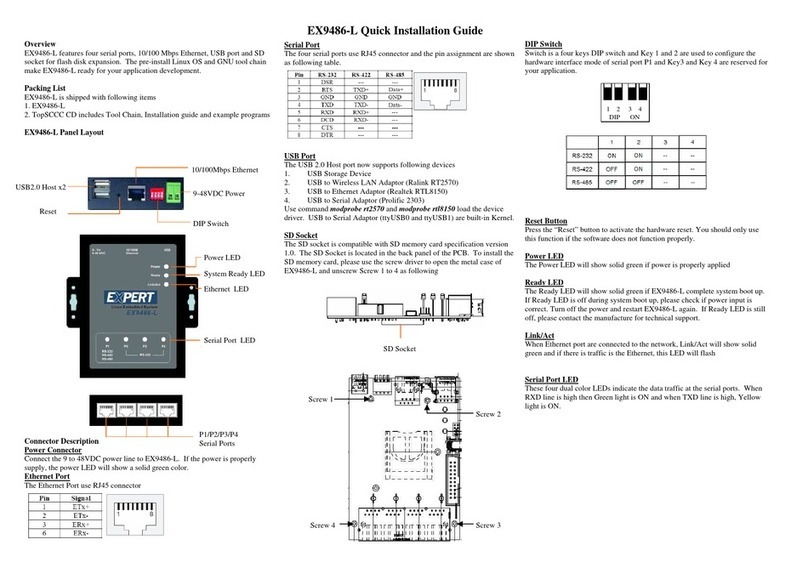

Expert

Expert EX9486-L Quick installation guide

HP

HP Xw4600 - Workstation - 2 GB RAM Read this first

StarTech.com

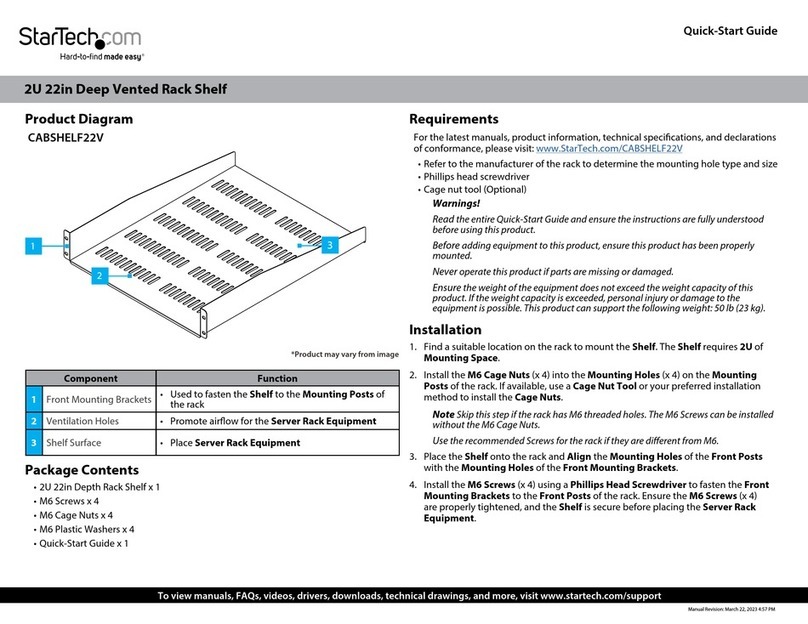

StarTech.com CABSHELF22V quick start guide

NEC

NEC NL12880BC20-05 Preliminary data sheet