5. Squelch Circuit Part of the audio signal from pin 9 of IC104 is amplified by the noise filter

amplifier consisting of R176, R186, R177, C179, C183, C191, and C194,

b

and the internai noise amplifier in IC104. The desired noise of the signal is

output through pin 11 of IC104, to be further amplified by the noise amplifier

(Q115). The amplified noise signal is rectified by oltage doubler D109 and

input to pin 4 of CPU (IC5).

2) Transmitter System The audio signal is con erted to an electric signal in either the internai or

external microphone, and input to the microphone amplifier (IC6). IC6

consiste of two operational amplifiers; one amplifier (pins 1, 2, and 3) is

composed of pre-emphasis and IDC circuits and the other (pins 5,6, and 7)

is composed of a splatter filter. The maximum frequency dé iation is

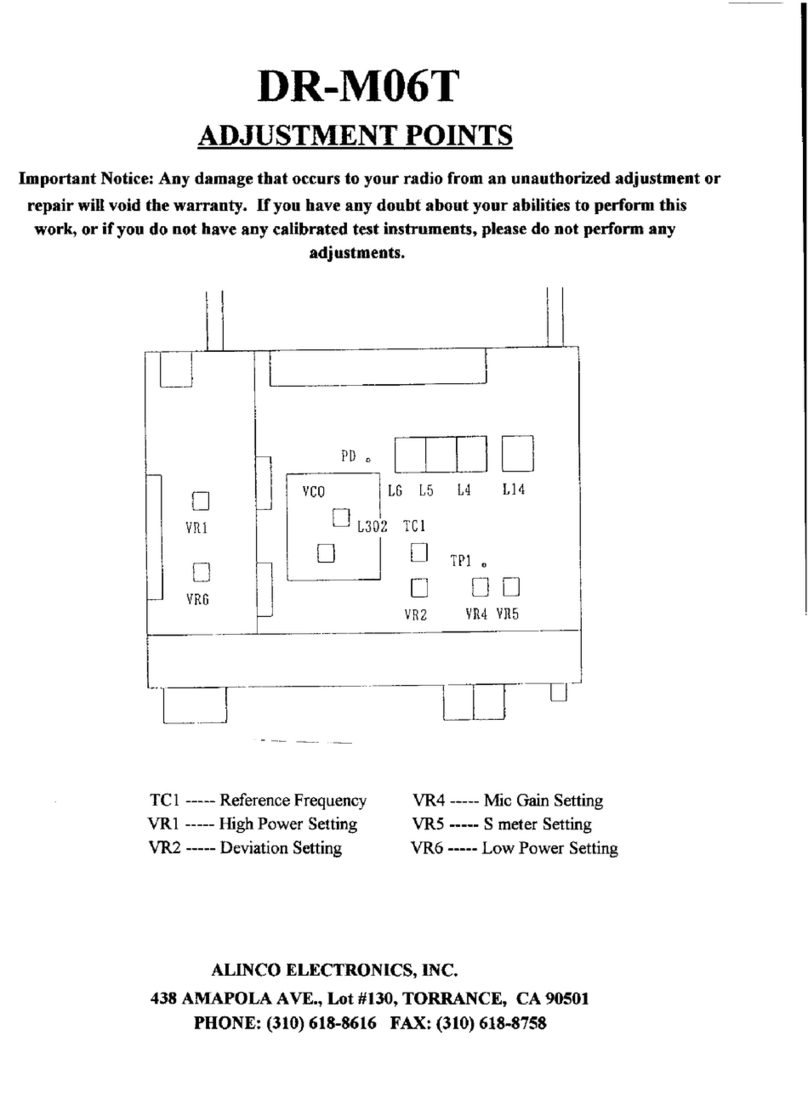

obtained by VR2 and input to the cathode of the aricap of the VCO, to

change the electric capacity in the oscillation circuit. This produces the

frequency modulation.

The transmitted signal is oscillated by the VCO, amplified by the pre-dri e

amplifier (Q102) and dri e amplifier (Q101), and input to the power module

(IC101). The signal is then amplified by the power module (IC101) and led

to the antenna switch (D101) and low-pass filter (L102, L103, L104, C113,

C107, C116, and C114), where unwanted high harmonie wa es are

reduced as needed, and the resulting signal is supplied to the antenna.

3. APC Circuit Part of the transmission power from the low-pass filter is detected by D103,

con erted to DC, and then amplified by a differential amplifier. The output

oltage Controls the bias oltage from pin 2 of the power module (IC101) to

maintain the transmission power constant.

3) PLL Synthesizer Circuit

1. PLL The di iding ratio is obtained by sending data from the CPU (IC5) to pin 2

and sending dock puises to pin 3 of the PLL IC (IC102). The oscillated

signal from the VCO is amplified by the buffer (Q117) and input to pin 6 of

IC102. Each programmable di ider in IC102 di ides the frequency of the

input signal by N according to the frequency data, to generate a

comparison frequency of 5 or 6.25 kHz.

2. Reference Frequency The reference frequency appropriate for the channel steps is obtained by

Circuit di iding the 21.25 MHz référencé oscillation (X101) by 4250 or 3400,

according to the data from the CPU (IC5). When the resulting frequency is

5 kHz, channel steps of 5,10,15,20,25, 30, and 50 kHz are used. When

itis 6.25 kHz, the 12.5 kHz channel step is used.

1. Modulator Circuit

2. Power Amplifier

Circuit