Rev. C | Page 2 of 24

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

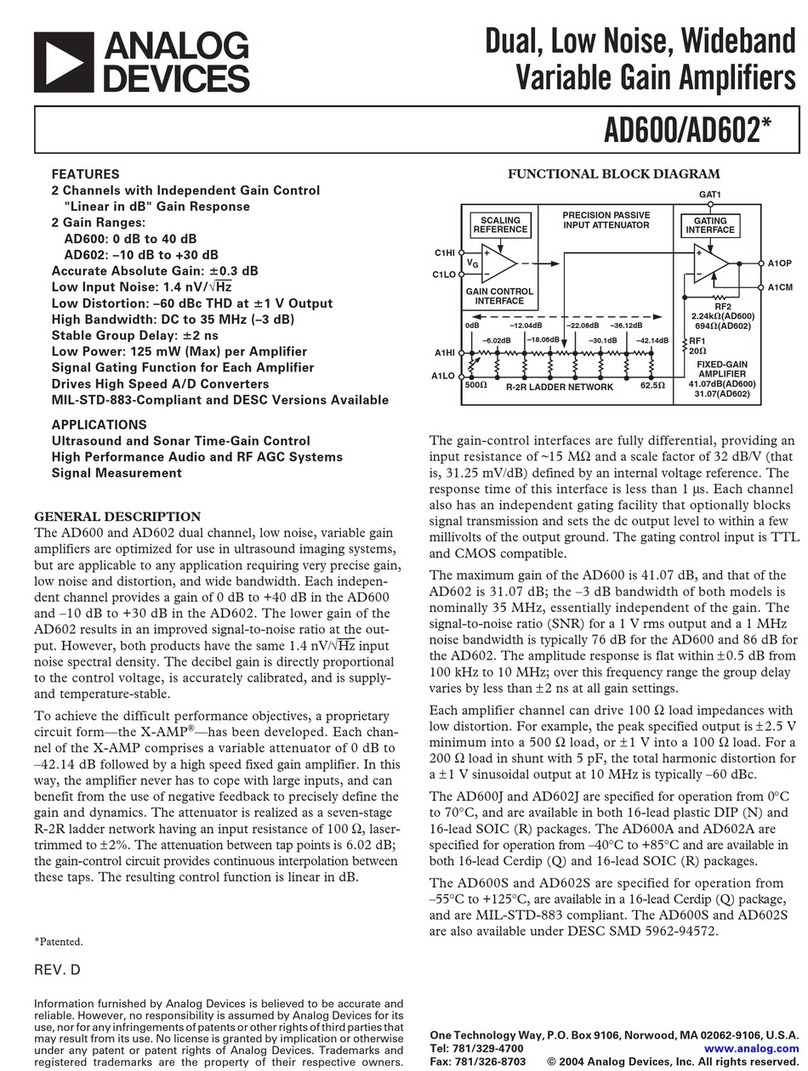

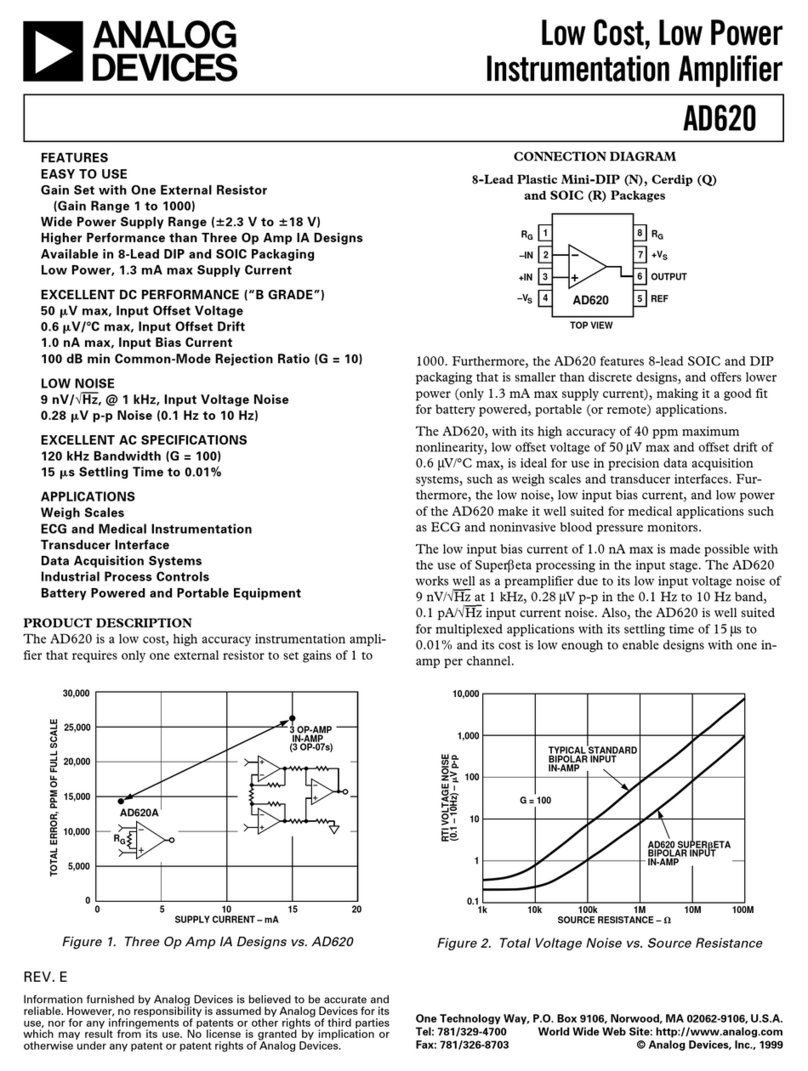

Connection Diagram ....................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 8

Thermal Characteristics .............................................................. 8

ESD Caution.................................................................................. 8

Pin Configuration and Function Descriptions............................. 9

Typical Performance Characteristics ........................................... 10

Theory of Operation ...................................................................... 17

Gain Selection ............................................................................. 18

Layout .......................................................................................... 18

Reference Terminal .................................................................... 19

Power Supply Regulation and Bypassing ................................ 19

Input Bias Current Return Path ............................................... 19

Input Protection ......................................................................... 19

RF Interference ........................................................................... 20

Precision Strain Gage................................................................. 20

Conditioning ±10 V Signals for a +5 V Differential Input

ADC ............................................................................................. 20

AC-Coupled Instrumentation Amplifier................................ 21

Die Information.............................................................................. 22

Outline Dimensions....................................................................... 23

Ordering Guide .......................................................................... 24

REVISION HISTORY

3/11—Rev. B to Rev. C

Added Pin Configuration and Function Descriptions Section.. 9

Added Die Information Section ................................................... 22

Updated Outline Dimensions....................................................... 23

Changes to Ordering Guide .......................................................... 24

9/07—Rev. A to Rev. B

Changes to Features.......................................................................... 1

Changes to Table 1 Layout............................................................... 3

Changes to Table 2 Layout............................................................... 5

Changes to Figure 15...................................................................... 11

Changes to Figures 32 .................................................................... 13

Changes to Figure 33, Figure 34, and Figure 35......................... 14

Updated Outline Dimensions....................................................... 21

Changes to Ordering Guide .......................................................... 22

11/03—Rev. 0 to Rev. A

Changes to Features.......................................................................... 1

Changes to Specifications Section.................................................. 4

Changes to Theory of Operation Section.................................... 13

Changes to Gain Selection Section............................................... 14

10/03—Revision 0: Initial Version