© 2023 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

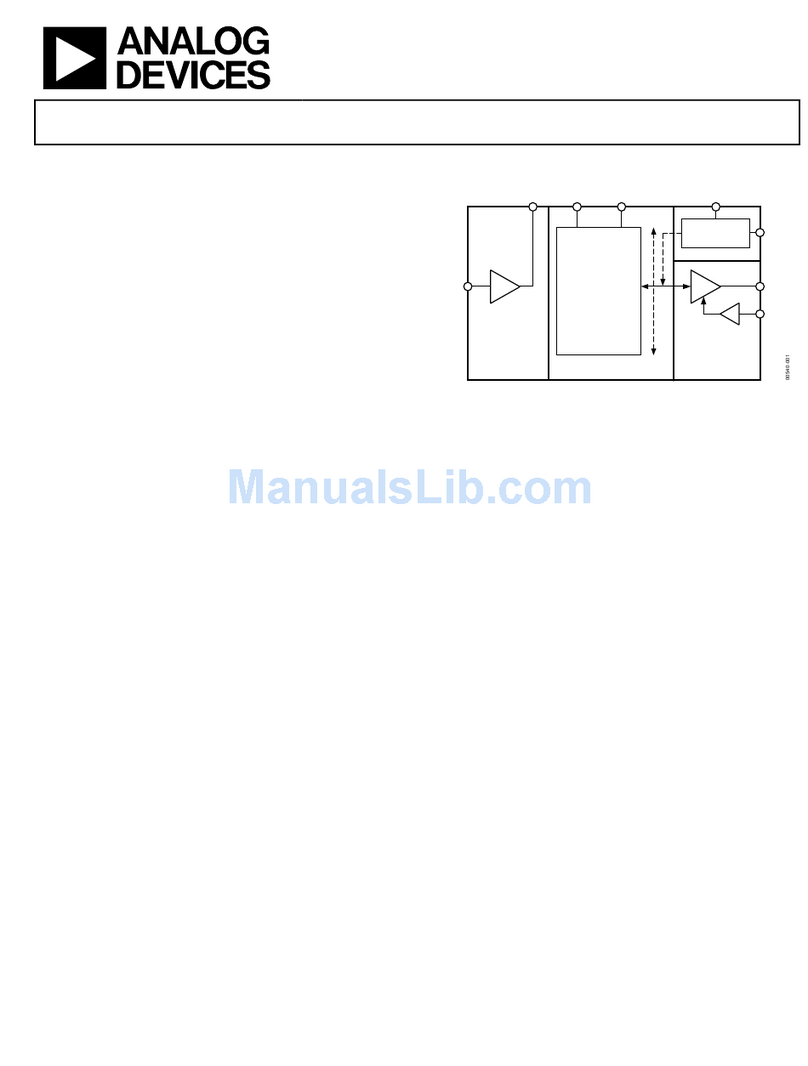

General Description

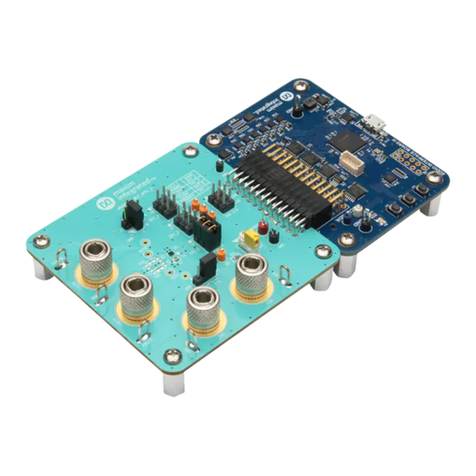

The MAX98388/MAX98389 is a small, cost-effective

mono digital input amplifier with integrated IV feedback.

The device operates over a wide supply voltage range

from 2.3V to 10V. With this supply range, both versions

support single-cell, two-cell, and externally

regulated/boosted portable applications. MAX98388 is

optimized for up to 5.5V applications (single-cell), while

MAX98389 is optimized for 5V to 10V cases (two-cell).

The Class-D playback amplifier pairs Class-AB level

audio performance with the efficiency needed to extend

battery life in portable applications. Active emissions-

limiting (AEL) and edge-rate limiting circuitry combined

with a spread-spectrum modulation (SSM) scheme

reduces EMI and eliminates the need for the output

filtering required for traditional Class-D amplifiers.

The device provides a precision output current sense

channel and an output voltage feedback channel. The

data collected by these channels can be transmitted on

the audio data output and enables algorithms such as

audio enhancement, bass boosting, speaker protection,

and haptic functions to be run on the host audio DSP.

The device includes a programmable threshold playback

channel ALC that provides brownout protection for

batteries in portable systems, and robust thermal and

overcurrent protection to prevent device damage.

The device provides a PCM interface for audio playback

and IV feedback data and pairs this with a standard I2C

interface for device control and status readback. The

PCM interface supports common audio data formats

such as I2S, left justified, and TDM timing. A unique

clocking structure eliminates the need for an external

high-frequency reference clock. In addition to reducing

device size and pin count, eliminating this clock saves

interface power while reducing the risk of EMI from high-

speed switching and potential board coupling issues.

The package connections are designed to only require

edge routing, allowing the use of the cost-effective

wafer-level package (WLP) with no requirement for

expensive bump vias. The device is available in a 0.4mm

pitch 16-bump WLP package and is specified over the

extended -40°C to +85°C temperature range.

SMBus is a trademark of Intel Corp.

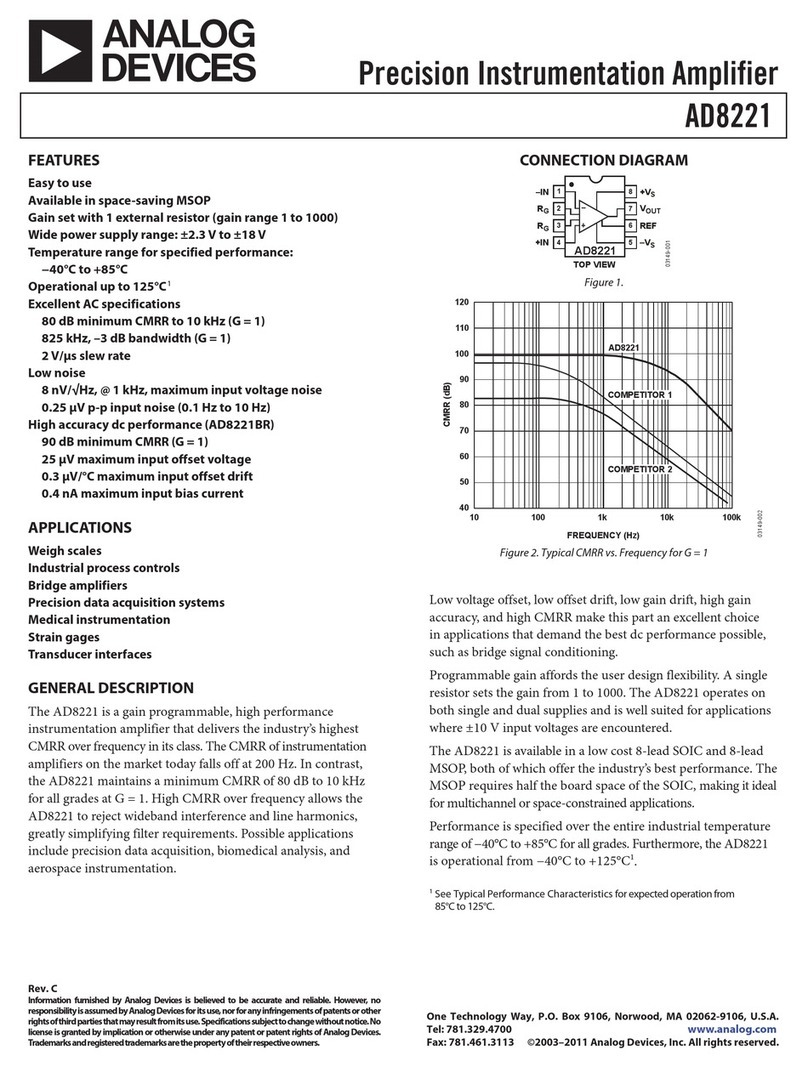

Benefits and Features

•Wide Amplifier Supply Range (2.3V to 10V)

•Supports Both Single-Cell and Two-Cell Cases

•High-Performance Class-D Amplifier

•Up to 111dB Dynamic Range (A-Weighted)

•10μVRMS Output Noise (Single-Cell Mode)

•14.5μVRMS Output Noise (Two-Cell Mode)

•High Output Power (THD+N ≤ 1%)

•1.32W Output Power into 4Ω (VPVDD = 3.7V)

•2.4W Output Power into 4Ω (VPVDD = 5V)

•5.15W Output Power into 4Ω (VPVDD = 7.4V)

•9.1W Output Power into 4Ω (VPVDD = 10V)

•High Amplifier Efficiency (Playback Only Power)

•76% Efficiency at 0.1W into 4Ω (VPVDD = 5V)

•85.5% Efficiency at 1W into 4Ω (VPVDD = 5V)

•90% Efficiency at 1W into 8Ω (VPVDD = 5V)

•Peak THD+N Better than -83dB at 1kHz

•Low Total Quiescent Power

•9.3mW (VPVDD = 3.7V, IV Feedback Disabled)

•13.9mW (VPVDD = 3.7V, IV Feedback Enabled)

•16.1mW (VPVDD = 5V, IV Feedback Enabled)

•22.5mW (VPVDD = 7.4V, IV Feedback Enabled)

•Low < 5µW Software Shutdown Power

•1ms Turn-On Time (fS= 48kHz, Ramp Disabled)

•Five Sample Playback Delay (fS< 50kHz, fIN = 1kHz)

•No External Reference Clock Required

•Playback Sample Rates from 8kHz to 96kHz

•Trimmed Class-D Switching Frequency for EMI Planning

•Extensive Click-and-Pop Reduction Circuitry

•Programmable ALC for Brownout Protection

•Robust Short-Circuit and Thermal Protection

•Available in Space-Saving Package:

•2.93mm2, 16-pin WLP (0.4mm Pitch)

Applications

•AR/VR Wearables

•LRA Haptic Drive

•Smart Watches and IoT Devices

•Gaming Devices

•Notebooks and Tablets

Ordering Information appears at end of data sheet.