UG-1268 EVAL-AD5758 User Guide

Rev. A | Page 2 of 22

TABLE OF CONTENTS

Features .............................................................................................. 1

Evaluation Kit Contents................................................................... 1

Equipment Needed........................................................................... 1

Additional Documents Required ................................................... 1

Software Required ............................................................................ 1

General Description..................................................................... 1

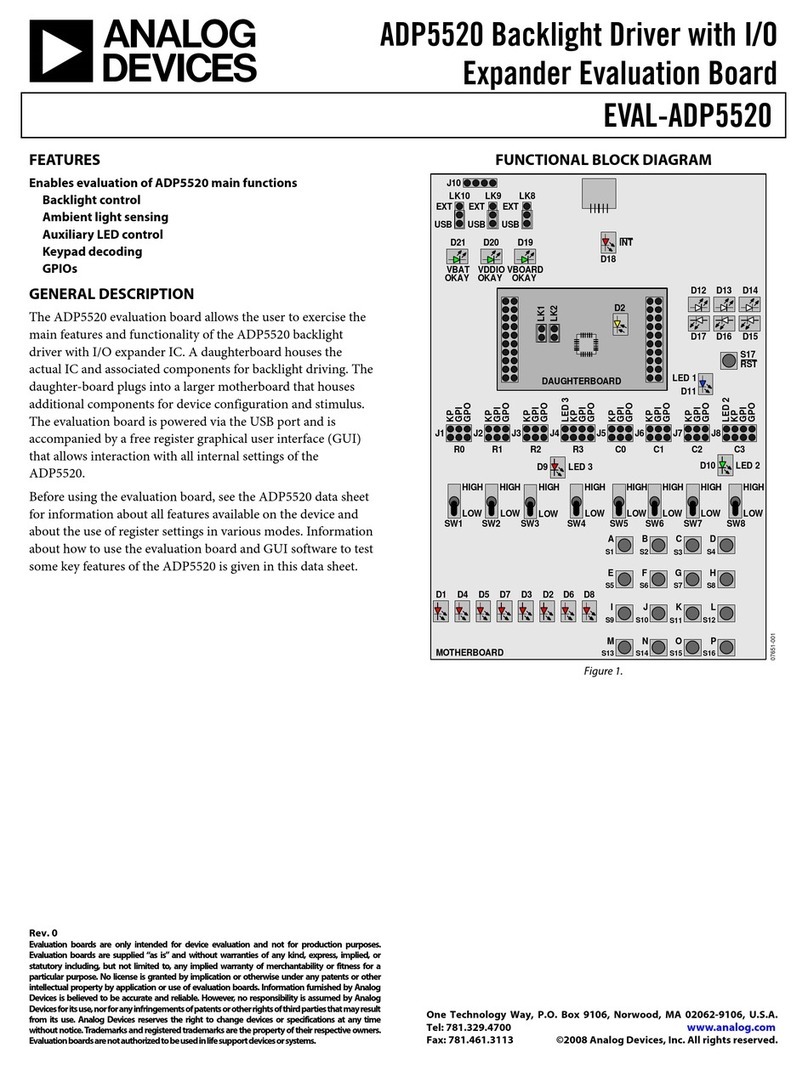

Evaluation Board Photograph......................................................... 1

Revision History ............................................................................... 2

Evaluation Board Hardware............................................................ 3

Power Supplies .............................................................................. 3

Serial Communication................................................................. 3

AD5758 Address Pins.................................................................... 3

Evaluation Software Quick Start Procedures................................ 5

Installing the Analysis|Control| Evaluation (ACE) Software

and AD5758 Plug-Ins ................................................................... 5

Initial Setup ....................................................................................5

AD5758 Block Diagram and Functions..........................................7

Initial Configuration.....................................................................9

DC-to-DC Converter Settings.....................................................9

Setting the DAC Output............................................................ 10

Writing to the ADC Configuration Register .......................... 10

Updating Diagnostic Results .................................................... 10

Example Configuration Sequences.......................................... 11

ACE Tool Views.............................................................................. 13

Macro Tool .................................................................................. 13

Register Debugger Tool ............................................................. 13

Events Tool .................................................................................. 13

Evaluation Board Schematics and Artwork................................ 14

Ordering Information.................................................................... 21

Bill of Materials........................................................................... 21

REVISION HISTORY

3/2019—Rev. 0 to Rev. A

Changes to Feature Section, General Description Section, and

Figure 1 .............................................................................................. 1

Changes to Power Supplies Section, Serial Communication

Section, and Table 1.......................................................................... 3

Changes to Table 2............................................................................ 4

Changes to Figure 2.......................................................................... 5

Changes to Figure 7.......................................................................... 6

Changes to Figure 8 and Table 3..................................................... 7

Changes to Table 4............................................................................ 8

Changes to Figure 10........................................................................ 9

Changes to Setting the DAC Output Section, Figure 11, Writing

to the Configuration Register Section, Figure 12, Figure 13, and

Figure 14 .......................................................................................... 10

Changes to Figure 15...................................................................... 11

Changes to Figure 16...................................................................... 12

Changes to Figu4re 17 ................................................................... 14

Changes to Figure 18...................................................................... 15

Changes to Figure 19...................................................................... 16

Changes to Figure 20...................................................................... 17

Deleted Figure 21 and Figure 22; Renumbered Sequentially ... 18

Added Figure 21; Renumbered Sequentially .............................. 18

Deleted Figure 23 and Figure 24 .................................................. 19

Added Figure 22, Figure 23, and Figure 24................................. 19

Added Figure 25 and Figure 26 .................................................... 20

Changes to Table 5.......................................................................... 21

5/2018—Revision 0: Initial Version