ADMV1013-EVALZ User Guide UG-1461

Rev. B | Page 9 of 19

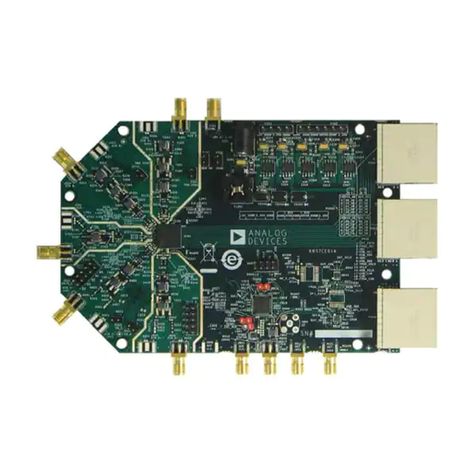

Label Function

F3 Click Bandgap Power Down (Label F3), and then click Apply Changes to set the BG_PD bit (Bit 10, Register 0x03). When

Bandgap Power Down is highlighted, the band gap is powered down. When the Bandgap Power Down button is not

highlighted, the band gap is powered up.

G or H Click VGA Power down (Label G and Label H), then click Apply Changes to set theVGA_PD bit (Bit 15, Register 0x03). When VGA

Power down is highlighted, the VGA is powered on. When the VGA Power down is not highlighted, the VGA is powered down.

I Click Quadrupler On (Label I), then click Apply Changes to set the QUAD_PD bits (Bits[13:11], Register 0x03). When

Quadrupler On is highlighted, these three bits are disabled. When Quadrupler On is not highlighted, these three bits are

enabled and the quadrupler is powered down.

J Click the dropdown list on the band-pass filter to set the LO Bandpass Filter (Label J), and then click Apply Changes to set the

QUAD_FILTERS bits (Bits[3:0], Register 0x09) to choose the appropriate LO input bandwidth. The four bandwidth options

include the following:

LO frequency bandwidth of 8.62 GHz to 10.25 GHz.

LO frequency bandwidth of 6.6 GHz to 9.2 GHz.

LO frequency bandwidth of 5.4 GHz to 8 GHz.

LO frequency bandwidth of 5.4 GHz to 7 GHz.

K Choose the appropriate LO Single Ended/ Differential Mode (Label K), and then click Apply Changes to set the

QUAD_SE_MODE bits (Bits[9:6], Register 0x09). There are three options: differential, single-ended positive side disable, and

single-ended negative side disable.

L Enter a value for the common-mode voltage (VCM) in the Common Mode Voltage (Label L) box, and then click Apply Changes.

The Common Mode Voltage value corresponds to MIXER_VGATE bits (Bits[6:0], Register 0x05). The Common Mode Voltage

box accepts values between 0.0 V and 2.6 V. The MIXER_VGATE decimal value is calculated by the following equations:

0 V to 1.8 V: MIXER_VGATE = 23.89 × VCM + 81

>1.8 V to 2.6 V: MIXER_VGATE = 23.75 × VCM + 1.25

M Click IF Enable (Label M), and then click Apply Changes to set the MIXER_IF_EN bit (Bit 7, Register 0x03). When IF Enable is

highlighted, the bit is enabled. When IF Enable is not highlighted, the bit is disabled.

P Click Mixer Powerdown (Label P), and then click Apply Changes to set the MIXER_PD bit (Bit 14, Register 0x03). When Mixer

Powerdown is highlighted, the MIXER_PD bit is disabled and the mixer is powered down.

Q1 to Q2 Use the sideband nulling blocks as follows:

Use the scroll arrows or enter a value between 0 and 127 in the PHASE ADJUST IFINE box (Label Q1), and then click Apply

Changes to set the LOAMP_PH_ADJ_I_FINE bits (Bits[13:7], Register 0x05).

Use the scroll arrows or enter a value between 0 and 127 in the PHASEA ADJUST QFINE box (Label Q2), and then click Apply

Changes to set the LOAMP_PH_ADJ_Q_FINE bits (Bits[13:7], Register 0x06).

See the Setting VCTRL Voltage for the ADMV1013 section for additional details.

R VCTRL Voltage (Label R). See the Setting VCTRL Voltage for the ADMV1013 section for additional details.

T1 to T8 Use the error mask and readback blocks as follows:

Click Parity Error Mask (Label T1), and then click Apply Changes to set the PARITY_ERROR_MASK bit (Bit 15, Register 0x02).

When Parity Error Mask is highlighted, the PARITY_ERRORS_MASK bit is enabled. When Parity Errors Mask is not highlighted,

the PARITY_ERROR_MASK bit is disabled.

Click Too Few Errors Mask (Label T2), and then click Apply Changes to set the TOO_FEW_ERRORS_MASK bit

(Bit 14, Register 0x02). When Too Few Errors Mask is highlighted, the TOO_FEW_ERRORS_MASK bit is enabled. When Too Few

Errors Mask is not highlighted, the TOO_FEW_ERRORS_MASK bit is disabled.

Click Many Errors Mask (Label T3), and then click Apply Changes to set theTOO_MANY_ERRORS_MASK bit (Bit 13, Register 0x02).

When Many Errors Mask is highlighted, the TOO_MANY_ERRORS_MASK bit is enabled. When Many Errors Mask is not

highlighted, the TOO_MANY_ERRORS_MASK bit is disabled.

Click Address Errors Mask (Label T4), and then click Apply Changes to set the ADDRESS_RANGE_ERROR_MASK bit (Bit 12,

Register 0x02). When Address Errors Mask is highlighted, the ADDRESS_RANGE_ERROR_MASK bit is enabled. When Address

Errors Mask is not highlighted, the ADDRESS_RANGE_ERROR_MASK bit is disabled.

When the PARITY_ERROR_MASK bit (Bit 15, Register 0x02) is set, Parity Error (Label T5) is red when toggling the PARITY_ERROR bit

(Bit 15, Register 0x01).

When the TOO_FEW_ERRORS_MASK bit (Bit 14, Register 0x02) is set, Too Few Errors (Label T6) is red when toggling the

TOO_FEW_ERRORS bit (Bit 14, Register 0x01).

When the TOO_MANY_ERRORS_MASK bit (Bit 13, Register 0x02) is set, Many Errors (Label T7) is red when toggling the

TOO_MANY_ERRORS bit (Bit 13, Register 0x01).

When the ADDRESS_RANGE_ERROR_MASK red bit (Bit 12, Register 0x02) is set, Address Errors (Label T8) lights up red when

toggling the ADDRESS_RANGE_ERROR bit (Bit 12, Register 0x01).