Evaluation Board User Guide EVAL-AD7450A/EVAL-AD7451

Rev. A | Page 9 of 28

LINK CONFIGURATION OPTIONS

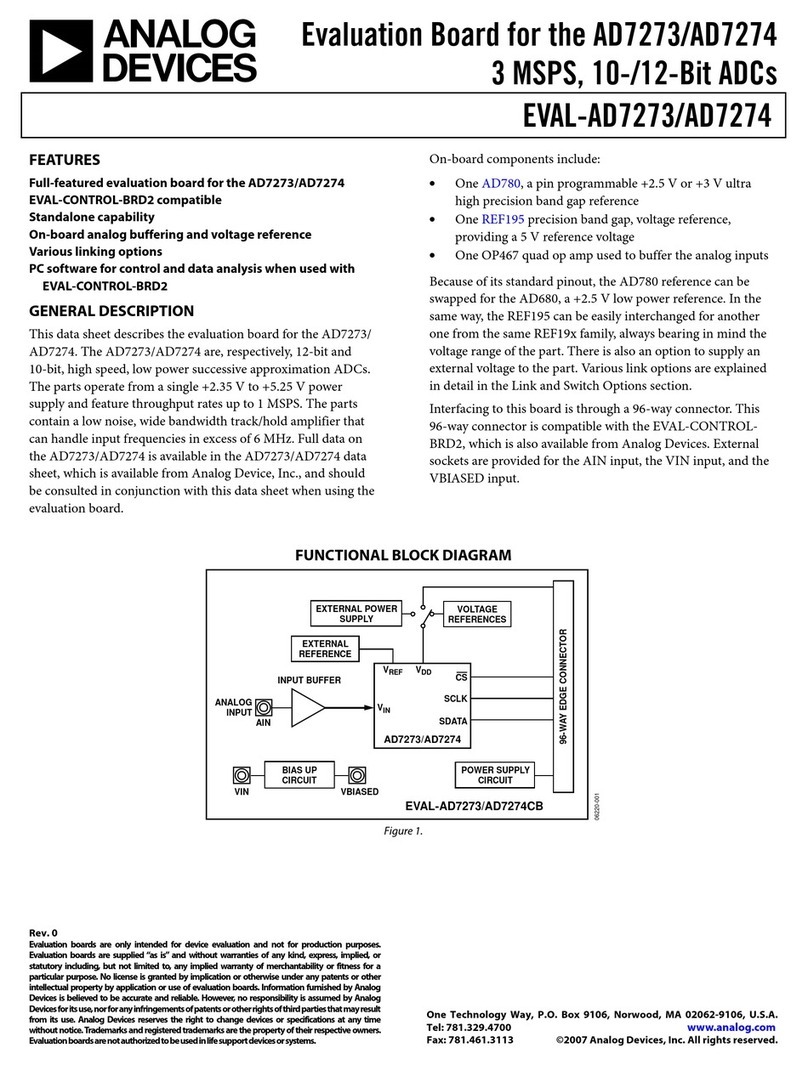

There are 12 link options that must be set for the required

operating setup before using the evaluation board. The

functions of these options are outlined in Table 2, which

shows the position in which all the links are set when the

evaluation board is packaged. Jumper and solder link (LKx)

options must be set correctly to select the appropriate operating

setup before using the evaluation board. The default link posi-

tions are shown in Table 3 and Table 4 and the functions of these

options are outlined in Table 2.

Table 2. Link Options

Link No. Function

LK1 INPUT A destination selection. This selects which buffer INPUT A is connected to.

Position A: INPUT A is connected to single-ended to differential buffer.

Position B: INPUT A is connected to single-ended buffer (U10-A).

Position C: INPUT A is connected to bias up circuit (U7-A/U7-B).

LK2 INPUT A input impedance selection.

Insert: INPUT A input impedance is 51 Ω.

LK3 INPUT B destination selection. This selects which buffer INPUT B is connected to.

Position A: INPUT B is connected to LK5 Position B.

Position B: INPUT B is connected to single-ended buffer (U10-B).

LK4 Input signal selection.

Insert when input signal at INPUT A is bipolar.

Remove when input signal at INPUT A is unipolar.

LK5 This selects the source for the positive terminal of U5-B.

Position A: ½ VREF is supplied to U5-B.

Position B: INPUT B is supplied to U5-B.

Position C: 0 V is supplied to U5-B.

LK6 VIN+ source selection. Select which buffered signal is routed to AD7450A/AD7451 Pin VIN+.

Position A: Signal is sourced from single-ended to differential buffer output (U5-A).

Position B: Signal is sourced from single-ended buffer (U10-A).

Position C: Signal is sourced from bias up circuit (U7-B).

VIN− source selection. Select which buffered signal is routed to AD7450A/AD7451 Pin V

IN−

Position A: Signal is sourced from single-ended to differential buffer output (U5-B).

Position B: Signal is sourced from single-ended buffer (U10-B).

LK8 INPUT B input impedance selection.

Insert: INPUT B input impedance is 51 Ω.

LK9 VREF source selection.

Position A: VREF is sourced from U2 (ADR431 an ultralow noise XFET® voltage reference).

Position B: VREF is sourced externally via SMB connector EXT_VREF.

LK1011Amplifier negative voltage supply selection.

Position A: Amplifier negative voltage supplied from on-board supply.

Position B: Amplifier negative voltage supplied from external source via J100 Terminal 1 labeled VSS.

LK1021Amplifier positive voltage selection.

Position A: Amplifier positive voltage supplied from on board supply.

Position B: Amplifier positive voltage supplied from external source via J100 Terminal 3 labeled VDD.

LK701 VDD supply for AD7450A/AD7451.

Position A: VDD supplied from on board supply (5 V).

Position B: VDD supplied from external source via J703 terminal labeled VCC.

1Both LK101 and LK102 should always be in corresponding positions.