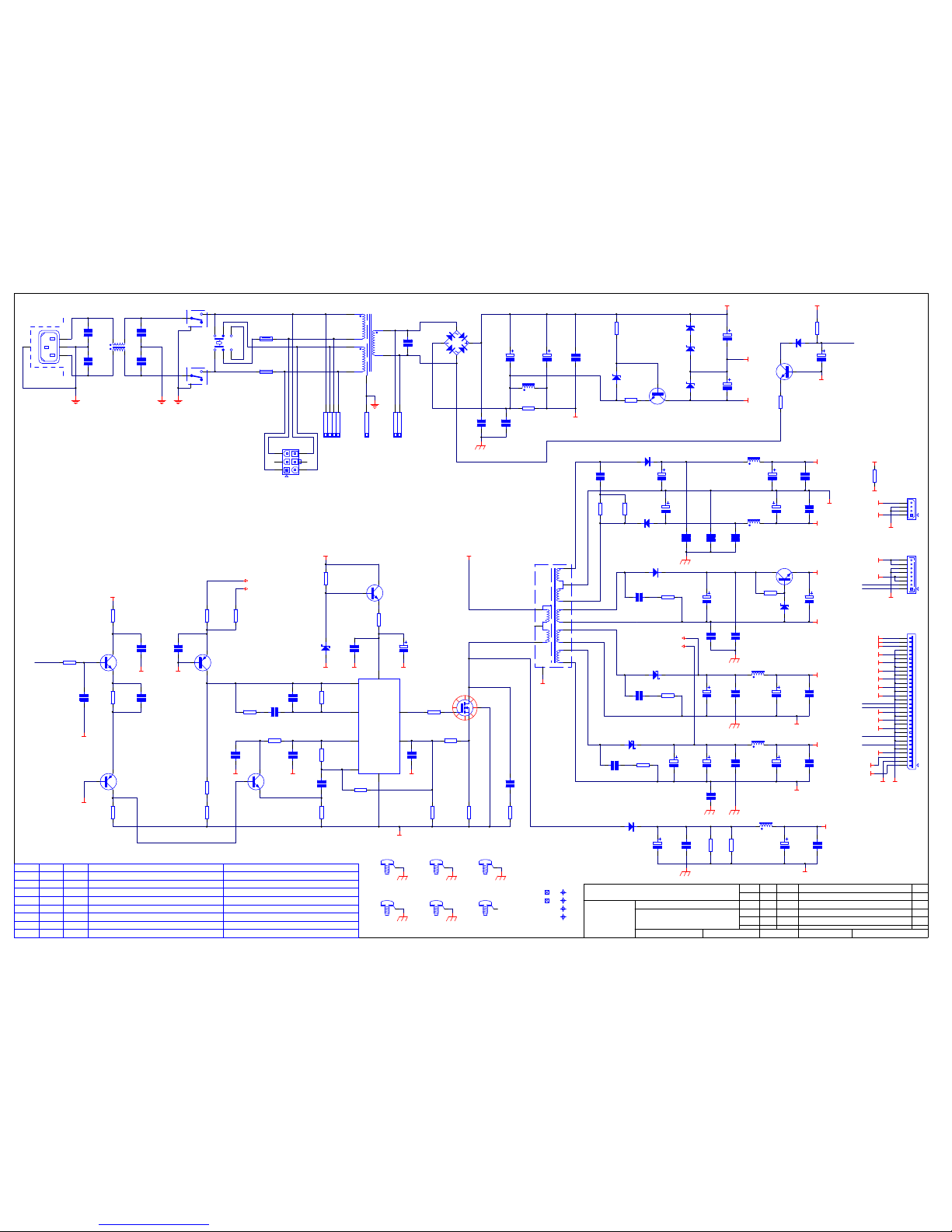

HDMI output stage

Please note: Due to the plug and play nature of the

HDMI/DVI interface, if presented with a reported no

HDMI problem it is worth checking all set-up

parameters of both the DVD player and the

Plasma/Projector in use before performing component

level diagnostics on this product.

HDMI is a system that transmits uncompressed digital

video and digital audio over a high speed encrypted

interface.

IC1102 is an SII9190 HDMI transmitter IC in essence

the chip takes the Digital Video and Audio information

and sends the Data out in HDMI format.

REG1100 is used to generate a clean regulated 3V3

power supply to Pins 18 and 33 of the HDMI chip.

IC1100 –IC1101 are 3 state octal/line drivers these

form a multiplex that switches between the 2 groups of

signals for the video data input stage of the SII9190

the multiplexer is control by the Signal from the Vaddis

V labelled as PROG/INT this will sit at logic 1 for

Progressive scan and logic 0 for interlaced.

In interlaced mode the 8 bit Y/Cb/Cr video data on

VIDP7-0 are passed to input port pins D15 – D8 of the

SII9190.

In Progressive scan mode all 20 bits of the Video

data bus are used and get mapped as follow.

VIDP 19 -12 provide 8 msbits of Y data to pins D15-8

VIDP 11 -10 provide 2Isbits of Y data to pins D2-3

VIDP 9 - 2 provide 8 msbits of Cb/Cr data to pins D23 – 16

VIDP 1 – 0 provide 2 Isbits of Cb/Cr data to pins D7 - 6

Along with the VIDP video data lines we must also see

VSYNC – Vertical sync data

HSYNC – Horizontal sync

CLK27M_VID – 27Mhz video clock.

SPDIF – Digital audio data

MCLK_HDMI – Used to strobe HDMI dig audio

At the output of the HDMI chip we will see the

following signals at SKT100.

TMDS (Transistion Minimised Differential Signalling)

this consists of a clock signal (TXC+/TXC-) and 3 data

signals (TX0+/TX0-, TX1+/TX1- and TX2+/TX2-).

All signals are differential and use current switching

techniques therefore no signals will be observed

unledd the output is correctly terminated. In this

application the clock signal will always be 27MHz and

the data signals will be clock X10 so 270Mbit/s.

DDC Channel this is a 12C interface on DDC_SCL and

DDC_SDA. These signals connect to the VADDIS V

which is the I2C bus master, The DDC channel is used

to read back information from the HDMI sync regarding

it’s Video and Audio capabilities and is also used for

HDCP encryption authentication.

+5V Power, the HDMI interface requires a 5V supply

capable of delivering around 50mA, the supply is

provided by REG 1101 which delivers the required

current and will shut down in the event of a short circuit.

Hotplug. The HDMI `Hot plug’ signal HDPIN is a +5V to

signal the presence of equipment being connected, this

converted to 3v3 logic 1 as IC1100 is not +5V tolerant.

CEC. The CEC (Consumer Electronics Control) signal is

a 1-wire bidirectional control signal. It connects to the

Vaddis via an ESD protection circuit D1102 at the

moment this line is not used at present and is a optional

part of the HDMI specification.

Comms and Final video output stage

The signals from the main board travel up to the Comms

board on connector CON902.

The Video signals simply travel via an A-C coupling net

before exiting the player via the RCA-phono sockets at

locations SKT902 and SKT903.

The RS232 interface is on 9 way “D” type CON900, with

IC900 providing the level translation and static protection

between the RS232 levels and the 3.3V CMOS levels

required by the VADDIS V, CON900 also supplies a +5V

Status level when ever the unit is not in standby this

generated from a buffered version of the AV_ENABLE

signal as used within the SCART output stage (0V in

standby).

We have two remote input bus’s on this board, the first

can be seen to arrive at SK901 on a 3.5mm mono jack

signal received should be a 36Khz modulated RC5

signal, the RC5 data then travels to the front panel and

is fed to IR led that is sited just behind the front panel IR

Sensor, we use the sensor to demodulate the and opto-

isolate the signal due to the fact that the signal is floating

up from ground.

The 3.5mm socket at location SKT900 is used to receive

un-modulated RC5 signals these take the form of a

5V/0V RC5 signal, with 5V representing a mark

(equivalent to a burst of 36Khz carrier on infrared) and

the 0V representing a space (equivalent to no-infra-red

carrier), this input is effectively wire-Ord with the front

panel IR receiver on IRRCV.