[AK4493]

017012230-E-00 2017/12

- 3 -

3. Table of Contents

1. General Description........................................................................................................................ 1

2. Features.......................................................................................................................................... 1

3. Table of Contents............................................................................................................................ 3

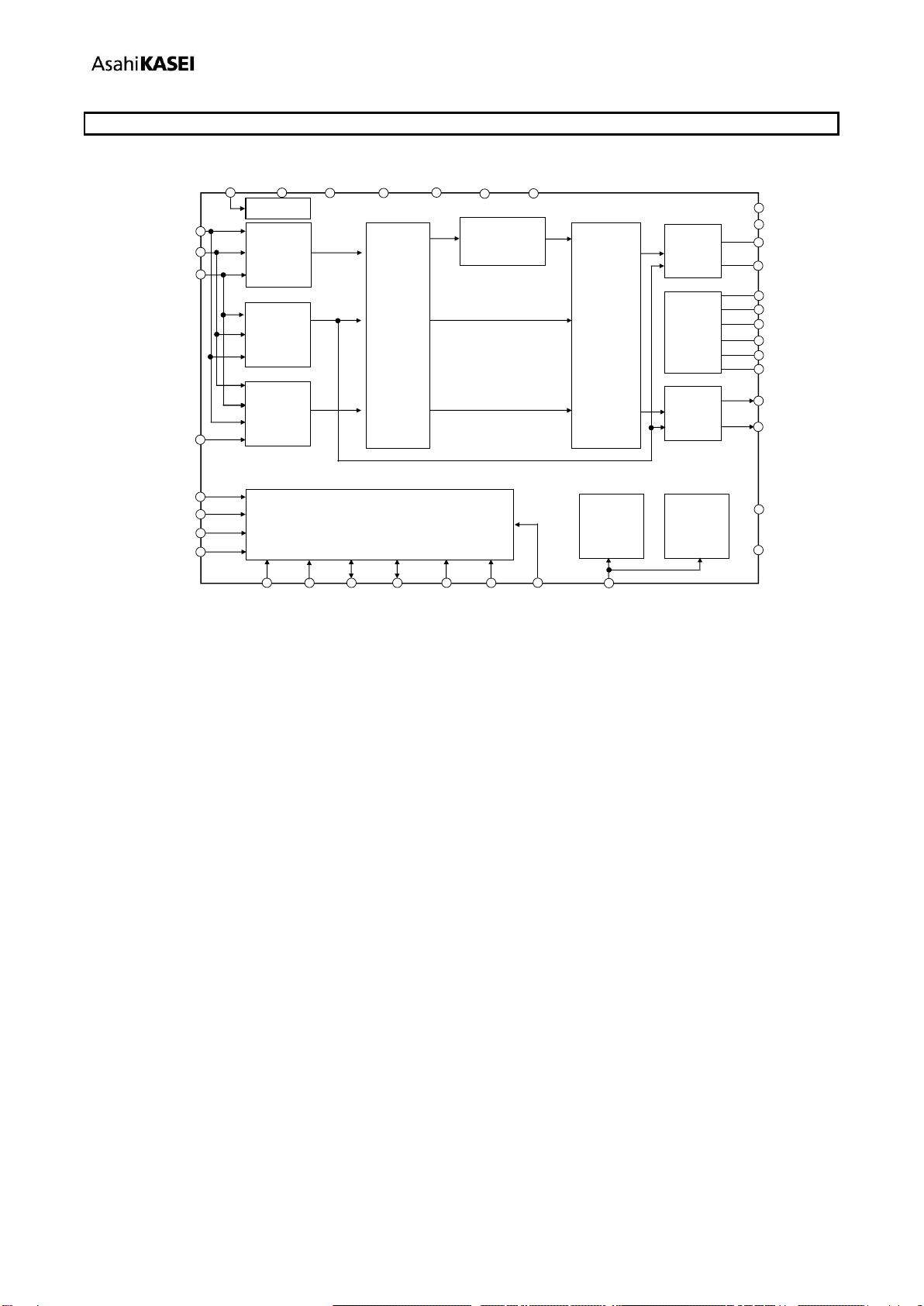

4. Block Diagram................................................................................................................................. 5

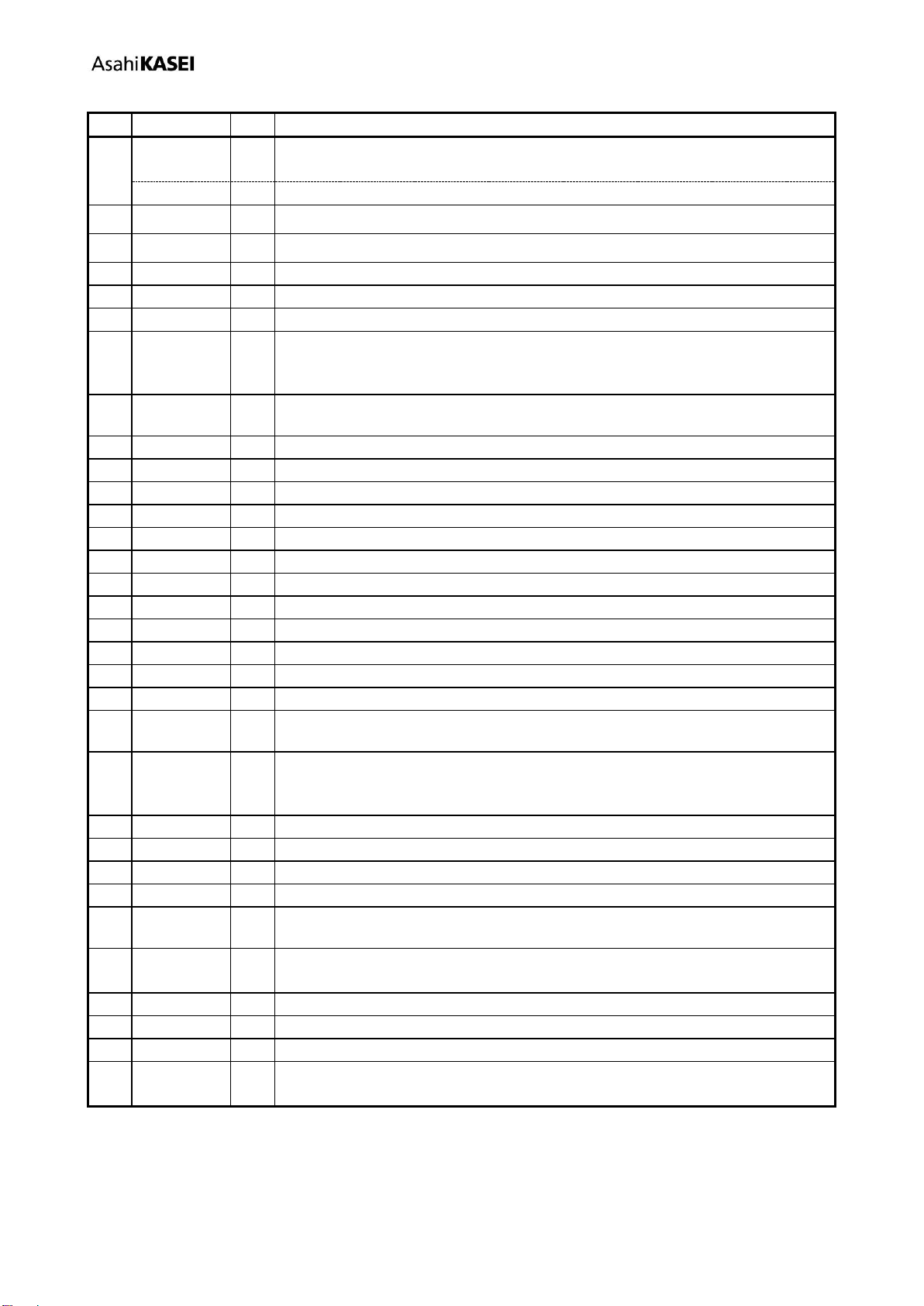

5. Pin Configurations and Functions................................................................................................... 6

■Pin Configurations.............................................................................................................................. 6

■Pin Functions ..................................................................................................................................... 7

■Handling of Unused Pin..................................................................................................................... 9

6. Absolute Maximum Ratings.......................................................................................................... 10

7. Recommended Operating Conditions .......................................................................................... 11

8. Electrical Characteristics .............................................................................................................. 12

■Analog Characteristics..................................................................................................................... 12

■DSD Mode........................................................................................................................................ 14

■Sharp Roll-Off Filter Characteristics................................................................................................ 15

■Slow Roll-Off Filter Characteristics.................................................................................................. 17

■Short Delay Sharp Roll-Off Filter Characteristics............................................................................ 19

■Short Delay Slow Roll-Off Filter Characteristics.............................................................................. 21

■Low Dispersion Short Delay Filter Characteristics.......................................................................... 23

■DSD Filter Characteristics................................................................................................................ 25

■DC Characteristics........................................................................................................................... 25

■Switching Characteristics................................................................................................................. 26

■Timing Diagram................................................................................................................................ 30

9. Functional Descriptions................................................................................................................. 35

■D/A Conversion Mode (PCM Mode, DSD Mode, EXDF Mode) ...................................................... 37

■D/A Conversion Mode Switching Timing ......................................................................................... 38

■System Clock................................................................................................................................... 39

■Audio Interface Format .................................................................................................................... 45

■Digital Filter...................................................................................................................................... 55

■De-emphasis Filter (PCM) ............................................................................................................... 55

■Output Volume (PCM, DSD and EXDF Modes; Register Control Mode only)................................ 56

■Gain Adjustment Function (PCM, DSD and EXDF Modes; Register Control Mode only).............. 57

■Zero Detection (PCM, DSD and EXDF Modes; Register Control Mode only) ................................ 57

■LR Channel Output Signal Select, Phase Inversion Function (PCM, DSD and EXDF Modes)...... 59

■Sound Quality Adjustment Function (PCM, DSD, EXDF; Register Control Mode only)................. 59

■DSD Signal Full-Scale (FS) Detection............................................................................................. 60

■Automatic Mode Switching Function (PCM/EXDF ⇔DSD Mode; Register Control Mode only).... 63

■Soft Mute Operation (PCM, DSD, EXDF)........................................................................................ 71

■LDO.................................................................................................................................................. 72

■Shutdown Switch.............................................................................................................................. 72

■Analog Output Overcurrent Protection............................................................................................. 72

■Power Up/Down Function................................................................................................................ 73

■Power-OFF/Reset Function............................................................................................................. 77

■Synchronize Function (PCM, EXDF)............................................................................................... 80

■Register Control Interface................................................................................................................ 82

■Register Map.................................................................................................................................... 86

■Register Definitions.......................................................................................................................... 88

10. Recommended External Circuits.................................................................................................. 96

11. Package...................................................................................................................................... 101

■Outline Dimensions (48-pin LQFP)................................................................................................101

■Material & Terminal Finish.............................................................................................................101

■Marking...........................................................................................................................................102