i

Table of Contents

Section 1

Overview............................................................................................... 1-1

1.1 Scope........................................................................................................1-1

1.2 Deliverables ..............................................................................................1-1

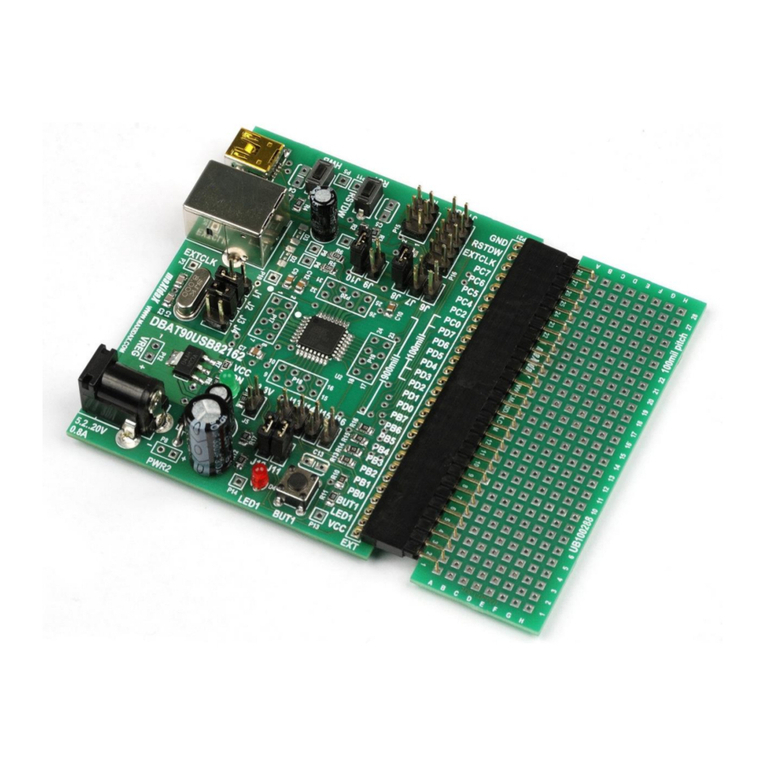

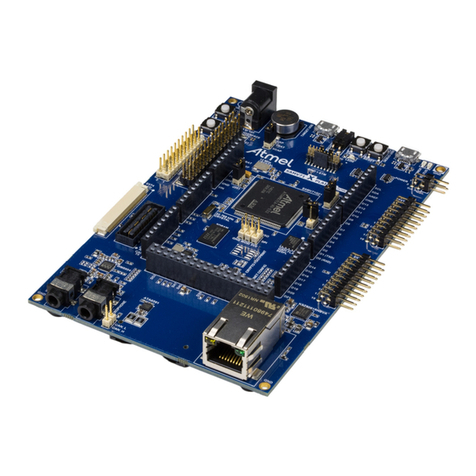

1.3 The AT91EB63 Evaluation Board .............................................................1-1

Section 2

Setting Up the AT91EB63 Evaluation Board ........................................ 2-1

2.1 Electrostatic Warning ................................................................................2-1

2.2 Requirements............................................................................................2-1

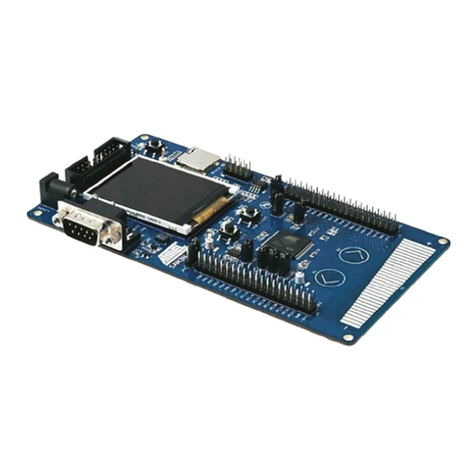

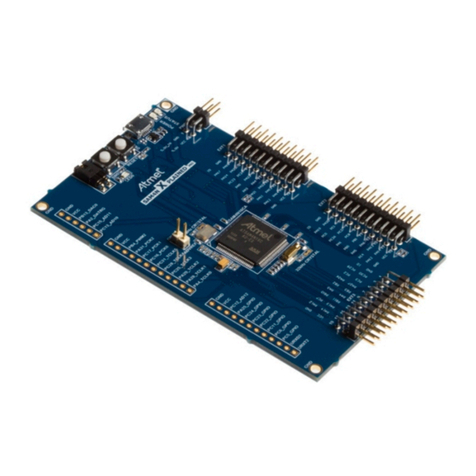

2.3 Layout .......................................................................................................2-1

2.4 Jumper Settings ........................................................................................2-2

2.5 Powering Up the Board.............................................................................2-2

2.6 Measuring Current Consumption on the AT91M63200 ............................2-2

2.7 Testing the AT91EB63 Evaluation Board .................................................2-3

Section 3

The On-board Software ........................................................................ 3-1

3.1 AT91EB63 Evaluation Board ....................................................................3-1

3.2 The Boot Program.....................................................................................3-1

3.3 Programmed Default Memory Mapping ....................................................3-2

3.4 The SRAM Downloader ............................................................................3-2

3.5 The Angel Monitor.....................................................................................3-2

Section 4

Circuit Description................................................................................. 4-1

4.1 AT91M63200 Processor ...........................................................................4-1

4.2 Expansion Connectors and JTAG Interface..............................................4-1

4.2.1 I/O Expansion Connector ...................................................................4-1

4.2.2 EBI Expansion Connector ..................................................................4-1

4.2.3 MPI Expansion Connector..................................................................4-1

4.2.4 JTAG Interface ...................................................................................4-2

4.3 Memories ..................................................................................................4-2

4.4 Power, Crystal Oscillator and Clock Distribution.......................................4-2

4.5 Push Buttons, LEDs, Reset and Serial Interfaces ....................................4-2

4.6 Layout Drawing .........................................................................................4-3

Downloaded from Elcodis.com electronic components distributor