3

Safety Instructions

Generally Guide

1. Please check electric circuits before maintenance and change the damaged or over heated components if

short-circuit has been found.

2. Please check all protective devices have been installed well after maintenance, such as insulation covering

and paper.

3. Please finish following electrical leakage tests after maintenance to avoid electric shock.

Low Voltage Leakage Testing

Take out power cord from an AC outlet and connect a length of wire between the two leads of the plug.

Use Gear R x 10K of the voltmeter to measure the resistance between shorted-out AC plug and exposed

metallic parts like screw cap, control shaft etc. which shall be infinite.

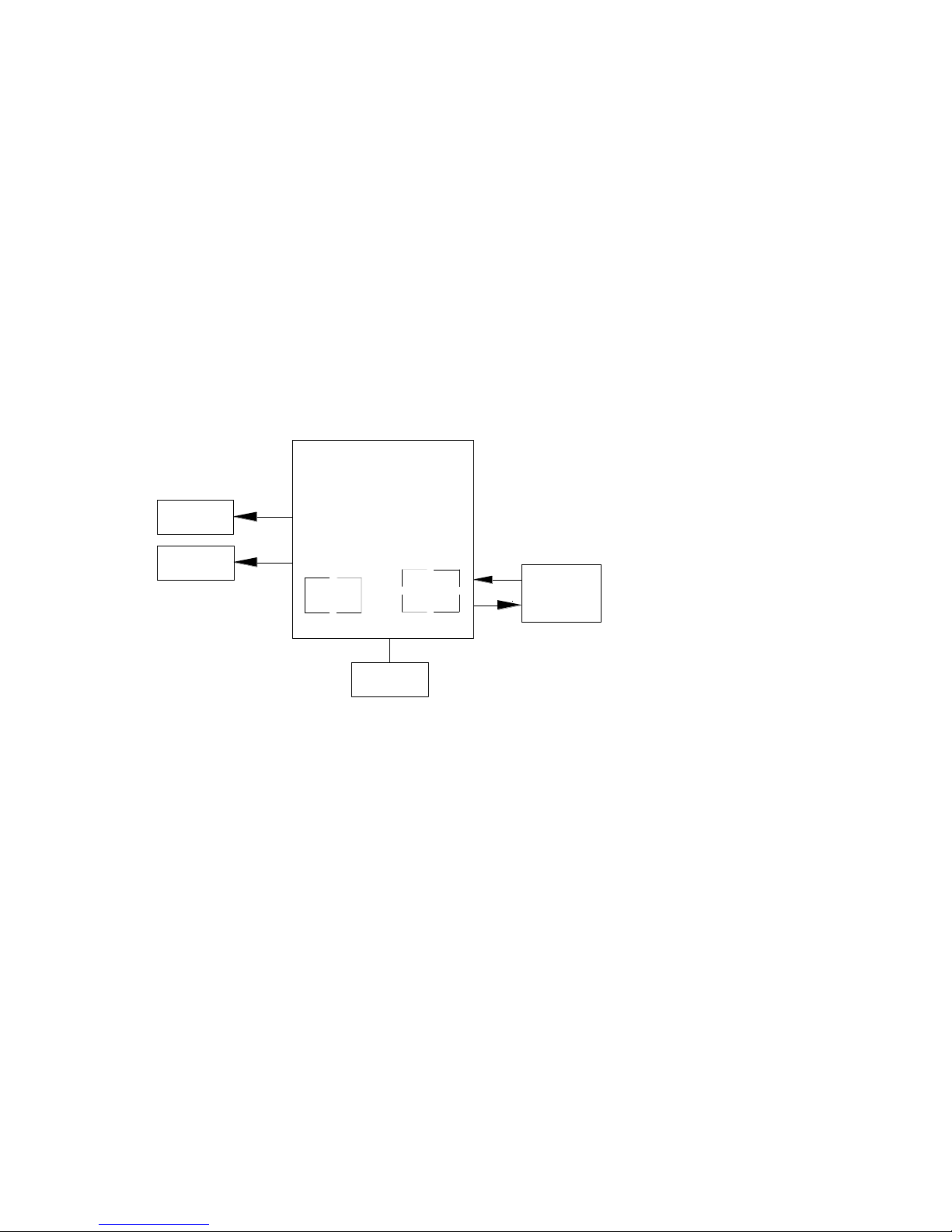

Picture 1

High Voltage Leakage Testing

As shown in Picture 1, connect a resistor of 1.5K, 10W and capacitor of 0.15 uF between exposed metallic

part and well grounded devices (water pipe etc.).

Plug power cord directly into the socket. Do not use insulated transformer to test.

Use 1000 Ohm/V or more sensitive voltmeter to measure AC voltage of the resistor.

Turn over the AC jack and plug into the socket again to iterate the inspection as above.

Inspect the voltage of the resistor between other exposed metallic parts and the earth in the same way.

Any parts’voltage of the resistor should not over 0.75Vrms. A leakage testing machine with voltage over

2,500 V can also be used for this inspection in which case the electric leakage should not be over 0.5mA. When

the leakage exceeds that limit, electric shock may occur. Please check and repair again before hand it over to

users.

4. Protect Electrostatic-Sensitive Devices from Electrostatic Discharge

Some solid states made of semiconductors materials can be easily damaged by commonly static charges,

those components are usually called electrostatic-sensitive devices. Such like integrated circuits, laser diodes

and field effect devices. The following tips will help you to reduce the impacts on those components while

electrostatic discharging.

Please release static which build-up on human body before handling electrostatic-sensitive devices by using

grounded tools. The antistatic strap which can be found in the market will be a good choice.