Bouffalo Lab BL702 User manual

Contents

1 System and memory overview ................................ 22

1.1 Introduction ...................................... 22

1.2 Main features ..................................... 22

1.3 Function description .................................. 22

2 Reset and clock ...................................... 26

2.1 Introduction ...................................... 26

2.2 Reset source ..................................... 26

2.3 Clock source ..................................... 27

3 GLB ............................................ 29

3.1 Introduction ...................................... 29

3.2 Function description .................................. 29

3.2.1 Clock management ............................... 29

3.2.2 Reset management ............................... 29

3.2.3 Bus management ................................ 31

3.2.4 Memory management .............................. 31

3.2.5 GPIO overview ................................. 31

3.2.6 GPIO main features ............................... 31

3.2.7 GPIO function description ............................ 32

3.2.8 GPIO function setting .............................. 33

3.2.9 GPIO output settings .............................. 37

3.2.10 GPIO input settings ............................... 37

3.2.11 GPIO optional function settings ......................... 37

3.2.12 GPIO interrupt settings ............................. 38

3.3 Register description .................................. 38

3.3.1 clk_cfg0 ..................................... 40

3.3.2 clk_cfg1 ..................................... 41

BL702/704/706 Reference Manual 2/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

3.3.3 clk_cfg2 ..................................... 42

3.3.4 clk_cfg3 ..................................... 43

3.3.5 swrst_cfg0 ................................... 43

3.3.6 swrst_cfg1 ................................... 44

3.3.7 swrst_cfg2 ................................... 45

3.3.8 cgen_cfg0 ................................... 46

3.3.9 cgen_cfg1 ................................... 46

3.3.10 bmx_cfg1 .................................... 47

3.3.11 bmx_cfg2 .................................... 48

3.3.12 bmx_err_addr .................................. 48

3.3.13 seam_misc ................................... 49

3.3.14 CPU_CLK_CFG ................................. 49

3.3.15 GPADC_32M_SRC_CTRL ............................ 50

3.3.16 DIG32K_WAKEUP_CTRL ............................ 50

3.3.17 UART_SIG_SEL_0 ............................... 51

3.3.18 GPIO_CFGCTL0 ................................ 53

3.3.19 GPIO_CFGCTL1 ................................ 54

3.3.20 GPIO_CFGCTL2 ................................ 55

3.3.21 GPIO_CFGCTL3 ................................ 56

3.3.22 GPIO_CFGCTL4 ................................ 57

3.3.23 GPIO_CFGCTL5 ................................ 58

3.3.24 GPIO_CFGCTL6 ................................ 59

3.3.25 GPIO_CFGCTL7 ................................ 60

3.3.26 GPIO_CFGCTL8 ................................ 61

3.3.27 GPIO_CFGCTL9 ................................ 62

3.3.28 GPIO_CFGCTL10 ................................ 63

3.3.29 GPIO_CFGCTL11 ................................ 64

3.3.30 GPIO_CFGCTL12 ................................ 65

3.3.31 GPIO_CFGCTL13 ................................ 66

3.3.32 GPIO_CFGCTL14 ................................ 67

3.3.33 GPIO_CFGCTL15 ................................ 68

3.3.34 GPIO_CFGCTL16 ................................ 69

3.3.35 GPIO_CFGCTL17 ................................ 69

3.3.36 GPIO_CFGCTL18 ................................ 70

3.3.37 GPIO_CFGCTL30 ................................ 71

3.3.38 GPIO_CFGCTL32 ................................ 72

3.3.39 GPIO_CFGCTL34 ................................ 74

3.3.40 GPIO_CFGCTL35 ................................ 76

3.3.41 GPIO_INT_MASK1 ............................... 77

BL702/704/706 Reference Manual 3/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

3.3.42 GPIO_INT_STAT1 ................................ 77

3.3.43 GPIO_INT_CLR1 ................................ 77

3.3.44 GPIO_INT_MODE_SET1 ............................ 78

3.3.45 GPIO_INT_MODE_SET2 ............................ 78

3.3.46 GPIO_INT_MODE_SET3 ............................ 79

3.3.47 GPIO_INT_MODE_SET4 ............................ 80

3.3.48 GPIO_INT2_MASK1 .............................. 81

3.3.49 GPIO_INT2_STAT1 ............................... 82

3.3.50 GPIO_INT2_CLR1 ............................... 82

3.3.51 GPIO_INT2_MODE_SET1 ............................ 82

3.3.52 GPIO_INT2_MODE_SET2 ............................ 83

3.3.53 GPIO_INT2_MODE_SET3 ............................ 84

3.3.54 GPIO_INT2_MODE_SET4 ............................ 85

3.3.55 led_driver .................................... 86

3.3.56 usb_xcvr .................................... 87

3.3.57 usb_xcvr_config ................................. 88

4 ADC ............................................ 90

4.1 ADC introduction ................................... 90

4.2 ADC main features .................................. 90

4.3 ADC functional description ............................... 91

4.3.1 ADC pins and internal signals .......................... 92

4.3.2 ADC channel .................................. 92

4.3.3 ADC clock ................................... 93

4.3.4 ADC conversion mode .............................. 94

4.3.5 ADC consequence ............................... 95

4.3.6 ADC interrupt .................................. 96

4.3.7 ADC FIFO ................................... 96

4.3.8 ADC configuration process ........................... 97

4.3.9 VBAT measurement ............................... 98

4.3.10 TSEN measurement ............................... 98

4.4 Register description .................................. 99

4.4.1 gpadc_config .................................. 99

4.4.2 gpadc_dma_rdata ................................ 100

4.4.3 gpadc_reg_cmd ................................. 101

4.4.4 gpadc_reg_config1 ............................... 103

4.4.5 gpadc_reg_config2 ............................... 105

4.4.6 gpadc_reg_scn_pos1 .............................. 107

4.4.7 gpadc_reg_scn_pos2 .............................. 107

4.4.8 gpadc_reg_scn_neg1 .............................. 108

BL702/704/706 Reference Manual 4/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

4.4.9 gpadc_reg_scn_neg2 .............................. 108

4.4.10 gpadc_reg_status ................................ 109

4.4.11 gpadc_reg_isr .................................. 109

4.4.12 gpadc_reg_raw_result .............................. 110

4.4.13 gpadc_reg_define ................................ 110

5 DAC ............................................ 111

5.1 DAC introduction ................................... 111

5.2 DAC main feature ................................... 111

5.3 DAC function description ................................ 111

5.4 Register description .................................. 113

5.4.1 gpdac_config .................................. 114

5.4.2 gpdac_dma_config ............................... 115

5.4.3 gpdac_dma_wdata ............................... 115

5.4.4 gpdac_ctrl ................................... 116

5.4.5 gpdac_actrl ................................... 116

5.4.6 gpdac_bctrl ................................... 117

5.4.7 gpdac_data ................................... 118

6 DMA ............................................ 119

6.1 DMA Introduction ............. ...................... 119

6.2 DMA main features .................................. 119

6.3 DMA functional description ............................... 120

6.3.1 Working principle ................................ 120

6.3.2 DMA channel configuration ........................... 122

6.3.3 Peripheral support ................................ 122

6.3.4 Linked List Mode ................................ 123

6.3.5 DMA interrupt .................................. 124

6.4 Transmission mode .................................. 125

6.4.1 Memory to memory ............................... 125

6.4.2 Memory to peripheral .............................. 125

6.4.3 Peripheral to memory .............................. 126

6.4.4 Peripheral to peripheral ............................. 126

6.5 Register description .................................. 127

6.5.1 DMA_IntStatus ................................. 129

6.5.2 DMA_IntTCStatus ................................ 129

6.5.3 DMA_IntTCClear ................................ 129

6.5.4 DMA_IntErrorStatus ............................... 130

6.5.5 DMA_IntErrClr ................................. 130

6.5.6 DMA_RawIntTCStatus .............................. 130

6.5.7 DMA_RawIntErrorStatus ............................. 131

BL702/704/706 Reference Manual 5/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

6.5.8 DMA_EnbldChns ................................ 131

6.5.9 DMA_SoftBReq ................................. 132

6.5.10 DMA_SoftSReq ................................. 132

6.5.11 DMA_SoftLBReq ................................ 132

6.5.12 DMA_SoftLSReq ................................ 133

6.5.13 DMA_Config .................................. 133

6.5.14 DMA_Sync ................................... 133

6.5.15 DMA_C0SrcAddr ................................ 134

6.5.16 DMA_C0DstAddr ................................ 134

6.5.17 DMA_C0LLI ................................... 134

6.5.18 DMA_C0Control ................................. 135

6.5.19 DMA_C0Config ................................. 136

6.5.20 DMA_C1SrcAddr ................................ 137

6.5.21 DMA_C1DstAddr ................................ 137

6.5.22 DMA_C1LLI ................................... 137

6.5.23 DMA_C1Control ................................. 138

6.5.24 DMA_C1Config ................................. 139

6.5.25 DMA_C2SrcAddr ................................ 140

6.5.26 DMA_C2DstAddr ................................ 140

6.5.27 DMA_C2LLI ................................... 140

6.5.28 DMA_C2Control ................................. 141

6.5.29 DMA_C2Config ................................. 142

6.5.30 DMA_C3SrcAddr ................................ 143

6.5.31 DMA_C3DstAddr ................................ 143

6.5.32 DMA_C3LLI ................................... 143

6.5.33 DMA_C3Control ................................. 144

6.5.34 DMA_C3Config ................................. 145

6.5.35 DMA_C4SrcAddr ................................ 146

6.5.36 DMA_C4DstAddr ................................ 146

6.5.37 DMA_C4LLI ................................... 146

6.5.38 DMA_C4Control ................................. 147

6.5.39 DMA_C4Config ................................. 148

6.5.40 DMA_C5SrcAddr ................................ 149

6.5.41 DMA_C5DstAddr ................................ 149

6.5.42 DMA_C5LLI ................................... 149

6.5.43 DMA_C5Control ................................. 150

6.5.44 DMA_C5Config ................................. 151

6.5.45 DMA_C6SrcAddr ................................ 152

6.5.46 DMA_C6DstAddr ................................ 152

BL702/704/706 Reference Manual 6/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

6.5.47 DMA_C6LLI ................................... 152

6.5.48 DMA_C6Control ................................. 153

6.5.49 DMA_C6Config ................................. 154

6.5.50 DMA_C7SrcAddr ................................ 155

6.5.51 DMA_C7DstAddr ................................ 155

6.5.52 DMA_C7LLI ................................... 155

6.5.53 DMA_C7Control ................................. 156

6.5.54 DMA_C7Config ................................. 157

7 L1C ............................................ 158

7.1 L1C introduction .................................... 158

7.2 L1C main features ................................... 159

7.3 L1C function description ................................ 159

7.3.1 Mutual conversion between TCM and Cache RAM resources ........... 159

7.3.2 Cache ..................................... 159

7.4 Register description .................................. 160

7.4.1 l1c_config .................................... 161

7.4.2 hit_cnt_lsb ................................... 161

7.4.3 hit_cnt_msb ................................... 161

7.4.4 miss_cnt .................................... 162

8 IR ............................................. 163

8.1 IR introduction ..................................... 163

8.2 IR main features .................................... 163

8.3 IR function description ................................. 163

8.3.1 Fixed receiving protocol ............................. 163

8.3.2 Pulse width reception .............................. 165

8.3.3 Normal sending mode .............................. 165

8.3.4 Pulse width transmission ............................ 165

8.3.5 Carrier modulation ................................ 166

8.3.6 IR interrupt ................................... 166

8.4 Register description .................................. 166

8.4.1 irtx_config .................................... 167

8.4.2 irtx_int_sts ................................... 168

8.4.3 irtx_data_word0 ................................. 169

8.4.4 irtx_data_word1 ................................. 169

8.4.5 irtx_pulse_width ................................. 169

8.4.6 irtx_pw ..................................... 170

8.4.7 irtx_swm_pw_0 ................................. 170

8.4.8 irtx_swm_pw_1 ................................. 171

8.4.9 irtx_swm_pw_2 ................................. 171

BL702/704/706 Reference Manual 7/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

8.4.10 irtx_swm_pw_3 ................................. 172

8.4.11 irtx_swm_pw_4 ................................. 172

8.4.12 irtx_swm_pw_5 ................................. 172

8.4.13 irtx_swm_pw_6 ................................. 173

8.4.14 irtx_swm_pw_7 ................................. 173

8.4.15 irrx_config ................................... 174

8.4.16 irrx_int_sts ................................... 174

8.4.17 irrx_pw_config ................................. 175

8.4.18 irrx_data_count ................................. 175

8.4.19 irrx_data_word0 ................................. 176

8.4.20 irrx_data_word1 ................................. 176

8.4.21 irrx_swm_fifo_config_0 ............................. 176

8.4.22 irrx_swm_fifo_rdata ............................... 177

9 SPI ............................................. 178

9.1 SPI introduction .................................... 178

9.2 SPI main features ................................... 178

9.3 SPI function description ................................ 179

9.3.1 Clock control .................................. 179

9.3.2 Master continuous transmission mode ...................... 179

9.3.3 Acceptance filtering function ........................... 180

9.3.4 Receive error correction ............................. 180

9.3.5 Slave mode timeout mechanism ......................... 180

9.3.6 I/O transfer mode ................................ 180

9.3.7 DMA transfer mode ............................... 181

9.3.8 SPI interrupt .................................. 181

9.4 Register description .................................. 181

9.4.1 spi_config .................................... 182

9.4.2 spi_int_sts ................................... 183

9.4.3 spi_bus_busy .................................. 184

9.4.4 spi_prd_0 .................................... 185

9.4.5 spi_prd_1 .................................... 185

9.4.6 spi_rxd_ignr ................................... 186

9.4.7 spi_sto_value .................................. 186

9.4.8 spi_fifo_config_0 ................................ 186

9.4.9 spi_fifo_config_1 ................................ 187

9.4.10 spi_fifo_wdata .................................. 188

9.4.11 spi_fifo_rdata .................................. 188

10 UART ........................................... 189

10.1 UART introduction ................................... 189

BL702/704/706 Reference Manual 8/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

10.2 UART main features .................................. 189

10.3 UART function description ............................... 190

10.3.1 Data format description ............................. 190

10.3.2 Clock source .................................. 190

10.3.3 Baud rate setting ................................ 191

10.3.4 Transmitter ................................... 192

10.3.5 Receiver .................................... 192

10.3.6 Automatic baud rate detection .......................... 193

10.3.7 Hardware flow control .............................. 194

10.3.8 LIN transmission mode ............................. 194

10.3.9 DMA transfer mode ............................... 195

10.3.10 UART interrupt ................................. 195

10.4 Register description .................................. 196

10.4.1 utx_config .................................... 196

10.4.2 urx_config ................................... 197

10.4.3 uart_bit_prd ................................... 198

10.4.4 data_config ................................... 199

10.4.5 utx_ir_position ................................. 199

10.4.6 urx_ir_position ................................. 199

10.4.7 urx_rto_timer .................................. 200

10.4.8 uart_sw_mode ................................. 200

10.4.9 uart_int_sts ................................... 201

10.4.10 uart_int_mask .................................. 201

10.4.11 uart_int_clear .................................. 202

10.4.12 uart_int_en ................................... 203

10.4.13 uart_status ................................... 203

10.4.14 sts_urx_abr_prd ................................. 204

10.4.15 uart_fifo_config_0 ................................ 204

10.4.16 uart_fifo_config_1 ................................ 205

10.4.17 uart_fifo_wdata ................................. 205

10.4.18 uart_fifo_rdata ................................. 206

11 I2C ............................................. 207

11.1 I2C introduction .................................... 207

11.2 I2C main features ................................... 207

11.3 I2C function description ................................ 207

11.3.1 Start and stop conditions ............................ 208

11.3.2 Data transmission format ............................ 208

11.3.3 Arbitration .................................... 209

11.4 I2C clock setting .................................... 210

BL702/704/706 Reference Manual 9/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

11.5 I2C configuration process ............................... 210

11.5.1 Configuration item ................................ 210

11.5.2 Read and write flags ............................... 211

11.5.3 Slave address .................................. 211

11.5.4 Slave register address .............................. 211

11.5.5 Slave device address length ........................... 211

11.5.6 Data ...................................... 211

11.5.7 Data length ................................... 211

11.5.8 Enable signal .................................. 212

11.6 FIFO management .................................. 212

11.7 Using DMA ...................................... 213

11.7.1 DMA transmission process ........................... 213

11.7.2 DMA receiving process ............................. 214

11.8 I2C interrupt ...................................... 214

11.9 Register description .................................. 214

11.9.1 i2c_config .................................... 215

11.9.2 i2c_int_sts ................................... 216

11.9.3 i2c_sub_addr .................................. 217

11.9.4 i2c_bus_busy .................................. 218

11.9.5 i2c_prd_start .................................. 218

11.9.6 i2c_prd_stop .................................. 219

11.9.7 i2c_prd_data .................................. 219

11.9.8 i2c_fifo_config_0 ................................ 220

11.9.9 i2c_fifo_config_1 ................................ 220

11.9.10 i2c_fifo_wdata .................................. 221

11.9.11 i2c_fifo_rdata .................................. 221

12 PWM ............................................ 222

12.1 PWM introduction ................................... 222

12.2 PWM main features .................................. 222

12.3 PWM function description ............................... 222

12.3.1 Clock and divider ................................ 222

12.3.2 Pulse generation principle ............................ 223

12.3.3 PWM interrupt .................................. 224

12.4 Register description .................................. 224

12.4.1 pwm_int_config ................................. 226

12.4.2 pwm0_clkdiv .................................. 226

12.4.3 pwm0_thre1 ................................... 226

12.4.4 pwm0_thre2 ................................... 227

12.4.5 pwm0_period .................................. 227

BL702/704/706 Reference Manual 10/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

12.4.6 pwm0_config .................................. 228

12.4.7 pwm0_interrupt ................................. 228

12.4.8 pwm1_clkdiv .................................. 229

12.4.9 pwm1_thre1 ................................... 229

12.4.10 pwm1_thre2 ................................... 229

12.4.11 pwm1_period .................................. 230

12.4.12 pwm1_config .................................. 230

12.4.13 pwm1_interrupt ................................. 231

12.4.14 pwm2_clkdiv .................................. 231

12.4.15 pwm2_thre1 ................................... 232

12.4.16 pwm2_thre2 ................................... 232

12.4.17 pwm2_period .................................. 232

12.4.18 pwm2_config .................................. 233

12.4.19 pwm2_interrupt ................................. 233

12.4.20 pwm3_clkdiv .................................. 234

12.4.21 pwm3_thre1 ................................... 234

12.4.22 pwm3_thre2 ................................... 235

12.4.23 pwm3_period .................................. 235

12.4.24 pwm3_config .................................. 235

12.4.25 pwm3_interrupt ................................. 236

12.4.26 pwm4_clkdiv .................................. 236

12.4.27 pwm4_thre1 ................................... 237

12.4.28 pwm4_thre2 ................................... 237

12.4.29 pwm4_period .................................. 238

12.4.30 pwm4_config .................................. 238

12.4.31 pwm4_interrupt ................................. 239

13 TIMER ........................................... 240

13.1 TIMER introduction .................................. 240

13.2 TIMER main features ................................. 241

13.3 TIMER function description .............................. 241

13.3.1 8-bit divider ................................... 241

13.3.2 General timer operating mode .......................... 242

13.3.3 Watchdog timer operating mode ......................... 243

13.3.4 Alarm setting .................................. 243

13.3.5 Watchdog alarm ................................. 244

13.4 Register description .................................. 244

13.4.1 TCCR ..................................... 246

13.4.2 TMR2_0 .................................... 247

13.4.3 TMR2_1 .................................... 247

BL702/704/706 Reference Manual 11/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

13.4.4 TMR2_2 .................................... 247

13.4.5 TMR3_0 .................................... 248

13.4.6 TMR3_1 .................................... 248

13.4.7 TMR3_2 .................................... 248

13.4.8 TCR2 ...................................... 249

13.4.9 TCR3 ...................................... 249

13.4.10 TMSR2 ..................................... 249

13.4.11 TMSR3 ..................................... 250

13.4.12 TIER2 ..................................... 250

13.4.13 TIER3 ..................................... 251

13.4.14 TPLVR2 .................................... 251

13.4.15 TPLVR3 .................................... 252

13.4.16 TPLCR2 .................................... 252

13.4.17 TPLCR3 .................................... 252

13.4.18 WMER ..................................... 253

13.4.19 WMR ...................................... 253

13.4.20 WVR ...................................... 254

13.4.21 WSR ...................................... 254

13.4.22 TICR2 ..................................... 255

13.4.23 TICR3 ..................................... 255

13.4.24 WICR ...................................... 256

13.4.25 TCER ...................................... 256

13.4.26 TCMR ..................................... 256

13.4.27 TILR2 ...................................... 257

13.4.28 TILR3 ...................................... 258

13.4.29 WCR ...................................... 258

13.4.30 WFAR ..................................... 259

13.4.31 WSAR ..................................... 259

13.4.32 TCVWR2 .................................... 259

13.4.33 TCVWR3 .................................... 260

13.4.34 TCVSYN2 ................................... 260

13.4.35 TCVSYN3 ................................... 260

13.4.36 TCDR ..................................... 261

14 QDEC ........................................... 262

14.1 QDEC introduction ................................... 262

14.2 QDEC main features .................................. 262

14.3 QDEC function description ............................... 263

14.4 Register description .................................. 264

14.4.1 qdec0_ctrl0 ................................... 265

BL702/704/706 Reference Manual 12/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

14.4.2 qdec0_ctrl1 ................................... 266

14.4.3 qdec0_value .................................. 267

14.4.4 qdec0_int_en .................................. 267

14.4.5 qdec0_int_sts .................................. 268

14.4.6 qdec0_int_clr .................................. 268

14.4.7 qdec1_ctrl0 ................................... 269

14.4.8 qdec1_ctrl1 ................................... 270

14.4.9 qdec1_value .................................. 270

14.4.10 qdec1_int_en .................................. 271

14.4.11 qdec1_int_sts .................................. 271

14.4.12 qdec1_int_clr .................................. 272

14.4.13 qdec2_ctrl0 ................................... 272

14.4.14 qdec2_ctrl1 ................................... 273

14.4.15 qdec2_value .................................. 274

14.4.16 qdec2_int_en .................................. 274

14.4.17 qdec2_int_sts .................................. 275

14.4.18 qdec2_int_clr .................................. 275

15 KeyScan .......................................... 277

15.1 KYS introduction ................................... 277

15.2 KYS main features ................................... 277

15.3 KYS function description ................................ 277

15.3.1 Configurable number of rows and columns .................... 277

15.3.2 GPIO selection ................................. 277

15.3.3 Key value .................................... 278

15.3.4 Interrupt .................................... 278

15.4 Register description .................................. 278

15.4.1 ks_ctrl ..................................... 278

15.4.2 ks_int_en .................................... 279

15.4.3 ks_int_sts .................................... 279

15.4.4 keycode_clr ................................... 280

15.4.5 keycode_value ................................. 280

16 I2S ............................................. 281

16.1 I2S introduction .................................... 281

16.2 I2S main features ................................... 281

16.3 I2S function description ................................ 281

16.4 Register description .................................. 282

16.4.1 i2s_config .................................... 282

16.4.2 i2s_int_sts ................................... 284

16.4.3 i2s_bclk_config ................................. 285

BL702/704/706 Reference Manual 13/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

16.4.4 i2s_fifo_config_0 ................................ 285

16.4.5 i2s_fifo_config_1 ................................ 286

16.4.6 i2s_fifo_wdata .................................. 287

16.4.7 i2s_fifo_rdata .................................. 287

16.4.8 i2s_io_config .................................. 287

17 Emac ........................................... 289

17.1 Emac introduction ................................... 289

17.2 Emac main features .................................. 289

17.3 Emac function description ............................... 290

17.4 Emac clock ...................................... 292

17.5 Send and receive buffer descriptor (BD, Buffer Descriptor) ................ 292

17.6 PHY interaction ......................... ........... 292

17.7 Programming process ................................. 293

17.7.1 PHY initialization ................................ 293

17.7.2 Send data frame ................................ 294

17.7.3 Receive data frame ............................... 294

17.8 Register description .................................. 295

17.8.1 MODE ..................................... 296

17.8.2 INT_SOURCE ................................. 297

17.8.3 INT_MASK ................................... 299

17.8.4 IPGT ...................................... 300

17.8.5 PACKETLEN .................................. 300

17.8.6 COLLCONFIG ................................. 301

17.8.7 TX_BD_NUM .................................. 301

17.8.8 MIIMODE .................................... 302

17.8.9 MIICOMMAND ................................. 303

17.8.10 MIIADDRESS .................................. 303

17.8.11 MIITX_DATA .................................. 304

17.8.12 MIIRX_DATA .................................. 304

17.8.13 MIISTATUS ................................... 304

17.8.14 MAC_ADDR0 .................................. 305

17.8.15 MAC_ADDR1 .................................. 305

17.8.16 HASH0_ADDR ................................. 306

17.8.17 HASH1_ADDR ................................. 306

17.8.18 TXCTRL .................................... 306

18 USB ............................................ 308

18.1 USB introduction ................................... 308

18.2 USB main features .................................. 308

BL702/704/706 Reference Manual 14/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

18.3 USB function description ................................ 308

18.3.1 USB steps ................................... 308

18.3.2 Part of the register configuration and function description ............. 309

18.3.3 USB enumeration phase interrupt processing flow ................ 311

18.3.4 Register operation flow of each transfer transaction ................ 311

18.4 Register description .................................. 315

18.4.1 usb_config ................................... 317

18.4.2 usb_lpm_config ................................. 318

18.4.3 usb_resume_config ............................... 319

18.4.4 usb_frame_no .................................. 319

18.4.5 usb_error .................................... 320

18.4.6 usb_int_en ................................... 320

18.4.7 usb_int_sts ................................... 322

18.4.8 usb_int_mask .................................. 323

18.4.9 usb_int_clear .................................. 324

18.4.10 ep1_config ................................... 326

18.4.11 ep2_config ................................... 327

18.4.12 ep3_config ................................... 328

18.4.13 ep4_config ................................... 329

18.4.14 ep5_config ................................... 330

18.4.15 ep6_config ................................... 331

18.4.16 ep7_config ................................... 332

18.4.17 ep0_fifo_config ................................. 333

18.4.18 ep0_fifo_status ................................. 333

18.4.19 ep0_tx_fifo_wdata ................................ 334

18.4.20 ep0_rx_fifo_rdata ................................ 334

18.4.21 ep1_fifo_config ................................. 335

18.4.22 ep1_fifo_status ................................. 335

18.4.23 ep1_tx_fifo_wdata ................................ 336

18.4.24 ep1_rx_fifo_rdata ................................ 336

18.4.25 ep2_fifo_config ................................. 337

18.4.26 ep2_fifo_status ................................. 337

18.4.27 ep2_tx_fifo_wdata ................................ 338

18.4.28 ep2_rx_fifo_rdata ................................ 338

18.4.29 ep3_fifo_config ................................. 339

18.4.30 ep3_fifo_status ................................. 339

18.4.31 ep3_tx_fifo_wdata ................................ 340

18.4.32 ep3_rx_fifo_rdata ................................ 340

18.4.33 ep4_fifo_config ................................. 341

BL702/704/706 Reference Manual 15/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

18.4.34 ep4_fifo_status ................................. 341

18.4.35 ep4_tx_fifo_wdata ................................ 342

18.4.36 ep4_rx_fifo_rdata ................................ 342

18.4.37 ep5_fifo_config ................................. 343

18.4.38 ep5_fifo_status ................................. 343

18.4.39 ep5_tx_fifo_wdata ................................ 344

18.4.40 ep5_rx_fifo_rdata ................................ 344

18.4.41 ep6_fifo_config ................................. 345

18.4.42 ep6_fifo_status ................................. 345

18.4.43 ep6_tx_fifo_wdata ................................ 346

18.4.44 ep6_rx_fifo_rdata ................................ 346

18.4.45 ep7_fifo_config ................................. 347

18.4.46 ep7_fifo_status ................................. 347

18.4.47 ep7_tx_fifo_wdata ................................ 348

18.4.48 ep7_rx_fifo_rdata ................................ 348

19 LowPower ......................................... 349

19.1 Introduction ...................................... 349

19.2 Main features ..................................... 350

19.3 Function description .................................. 350

19.3.1 Power domain .................................. 350

19.3.2 Wakeup source ................................. 352

19.3.3 Power mode .................................. 352

19.4 Register description .................................. 353

19.4.1 HBN_CTL .................................... 354

19.4.2 HBN_TIME_L .................................. 355

19.4.3 HBN_TIME_H .................................. 355

19.4.4 RTC_TIME_L .................................. 356

19.4.5 RTC_TIME_H .................................. 356

19.4.6 HBN_IRQ_MODE ................................ 357

19.4.7 HBN_IRQ_STAT ................................ 358

19.4.8 HBN_IRQ_CLR ................................. 358

19.4.9 HBN_PIR_CFG ................................. 359

19.4.10 HBN_PIR_VTH ................................. 359

19.4.11 HBN_PIR_INTERVAL .............................. 360

19.4.12 HBN_MISC ................................... 360

19.4.13 HBN_GLB ................................... 361

19.4.14 HBN_SRAM .................................. 362

19.5 Register description .................................. 363

19.5.1 PDS_CTL .................................... 363

BL702/704/706 Reference Manual 16/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

19.5.2 PDS_TIME1 .................................. 365

19.5.3 PDS_INT .................................... 366

19.5.4 PDS_CTL2 ................................... 367

19.5.5 PDS_CTL3 ................................... 368

19.5.6 PDS_CTL4 ................................... 369

19.5.7 pds_stat .................................... 371

19.5.8 pds_ram1 .................................... 372

19.5.9 pds_gpio_set_pu_pd .............................. 372

19.5.10 pds_gpio_int .................................. 374

20 Revision history ....................................... 375

BL702/704/706 Reference Manual 17/ 375 @2021 Bouffalo Lab

guest@bouffalolab

List of Figures

2.1 Resetsource ................................................. 27

2.2 Clockarchitecture .............................................. 28

3.1 BasicblockdiagramofGPIO ........................................ 32

4.1 ADCblockdiagram.............................................. 91

4.2 ADCClock .................................................. 93

5.1 DACbasicblockdiagram .......................................... 112

6.1 DMAarchitecture............................................... 121

6.2 LLIarchitecture................................................ 124

7.1 L1carchitecture ............................................... 158

7.2 Cachearchitecture.............................................. 160

8.1 neclogical................................................... 164

8.2 nec....................................................... 164

8.3 rc5logical................................................... 164

8.4 rc5....................................................... 165

9.1 SPIclock ................................................... 179

9.2 SPIIgnorewaveform............................................. 180

10.1UARTdata .................................................. 190

10.2UARTclock.................................................. 191

10.3UARTsamplingwaveform.......................................... 192

10.4 UART fixed character mode waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

10.5UARTflowcontrol .............................................. 194

11.1I2Cstop/startcondition ........................................... 208

BL702/704/706 Reference Manual 18/ 375 @2021 Bouffalo Lab

guest@bouffalolab

BL702/704/706 Reference Manual

11.2I2Cdatatransmissionformat ........................................ 208

11.3Mastertxandslaverx ............................................ 209

11.4Masterrxandslavetx ............................................ 209

11.5TxandRxtogether.............................................. 210

12.1PWMwaveform................................................ 223

13.1Timerblockdiagram ............................................. 240

13.2Watchdogtimerblockdiagram ....................................... 241

13.3TimerPreload................................................. 242

13.4Watchdogtiming ............................................... 243

13.5Watchdogalarmmechanism ........................................ 244

14.1QDECfunctionalblockdiagram....................................... 264

17.1EMACarchitecture.............................................. 291

18.1USBinterrupttriggermode ......................................... 310

18.2USBcommunicationmethod ........................................ 313

19.1Lowpowermode............................................... 349

BL702/704/706 Reference Manual 19/ 375 @2021 Bouffalo Lab

guest@bouffalolab

List of Tables

1.1 Busconnection................................................ 23

1.2 MemoryMap ................................................. 23

1.2 MemoryMap ................................................. 24

1.3 Interruptsource................................................ 24

1.3 Interruptsource................................................ 25

3.1 Softwareresetfunctiontable ........................................ 30

3.2 GPIOfunctiontable1 ............................................ 33

3.2 GPIOfunctiontable1 ............................................ 34

3.3 GPIOfunctiontable2 ............................................ 35

3.3 GPIOfunctiontable2 ............................................ 36

3.4 GPIOfunctiontable3 ............................................ 36

4.1 ADCinternalsignals............................................. 92

4.2 ADCexternalpins .............................................. 92

4.3 ADCconversionresultformat........................................ 95

5.1 Internalreferencevoltage .......................................... 113

7.1 WayDisablesettings ............................................. 159

11.1Pinlists .................................................... 207

12.1DutyCycleParameters ........................................... 224

16.1I2Spinlist................................................... 281

17.1Transmissionsignal ............................................. 292

17.1Transmissionsignal ............................................. 293

18.1Registerconfiguration1 ........................................... 314

BL702/704/706 Reference Manual 20/ 375 @2021 Bouffalo Lab

guest@bouffalolab

This manual suits for next models

2

Table of contents

Popular Microcontroller manuals by other brands

ST

ST STM32F0DISCOVERY user manual

I2SE

I2SE Powerline Bundle for Internet of Things quick start guide

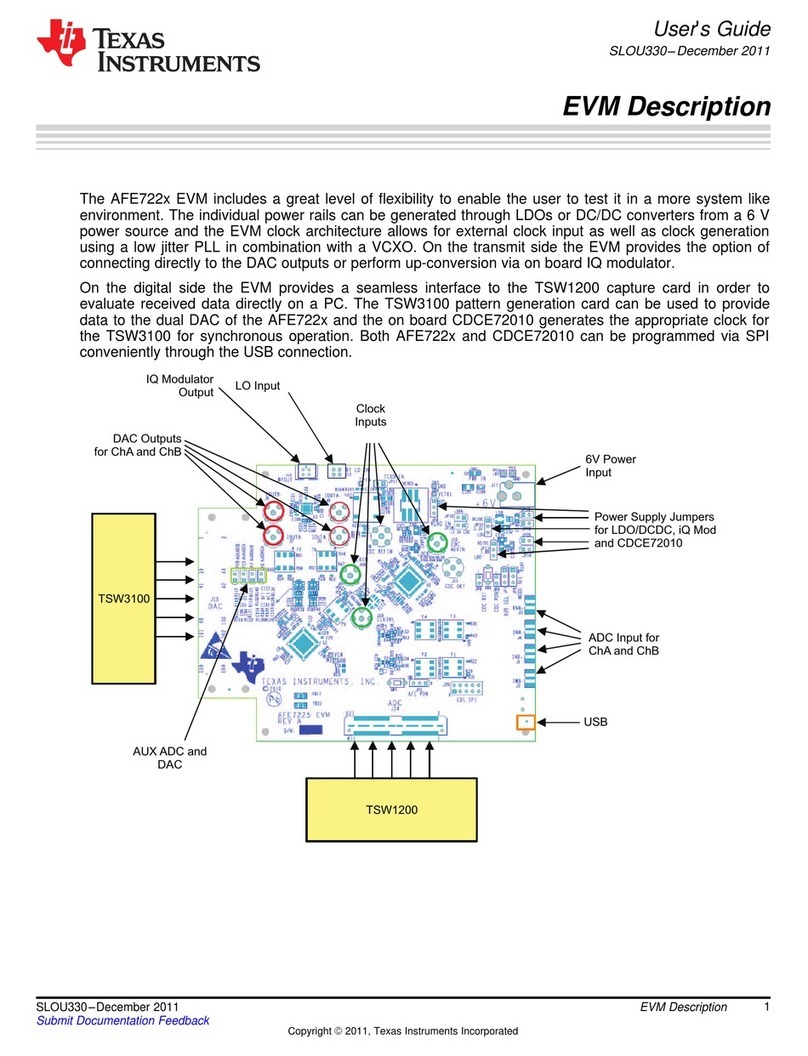

Texas Instruments

Texas Instruments AFE722 Series user guide

TENX TECHNOLOGY

TENX TECHNOLOGY 82314BW user manual

Infineon

Infineon XMC4000 series user guide

ZiLOG

ZiLOG Z8 Encore! XP F1680 28-Pin Series user manual

Silicon Laboratories

Silicon Laboratories C8051F36 Series user guide

Maxim Integrated

Maxim Integrated MAX32600 user guide

Espressif Systems

Espressif Systems ESP32 Series manual

Espressif

Espressif ESP32-C6-DevKitC-1 user guide

Huawei

Huawei ViewPoint 8650C Series user guide

Option Audio

Option Audio GTM60 series user guide