Cirrus Logic CS49300 Guide

1

Copyright

Cirrus Logic, Inc. 2003

(All Rights Reserved)

http://www.cirrus.com

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

Preliminary Product Information

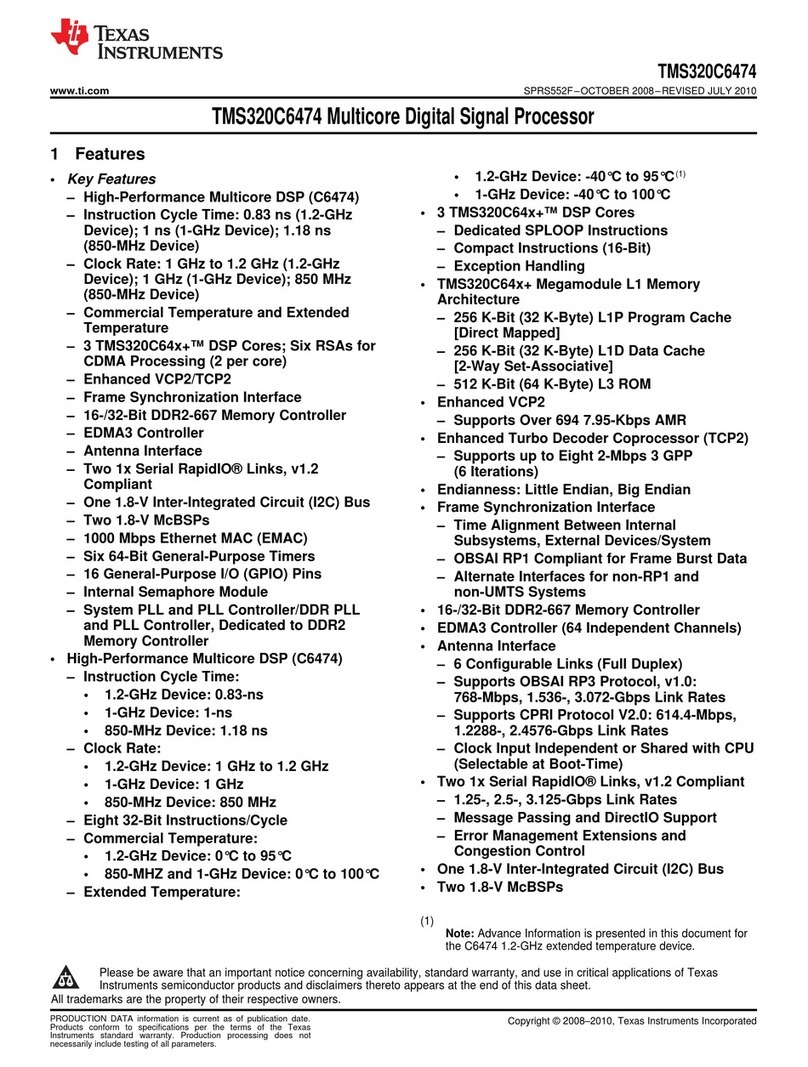

Features

Supports 4 digital S/PDIF

(IEC60958/IEC61937) inputs

8 Discrete analog inputs usingthe CS42528

+ 3 external CS5351 ADCs for 8 analog

channels of input at 48 kHz and 96 kHz

2 Channel upsampling supported

8 Discrete analog outputs from the CS42528

2 Digital S/PDIF (IEC60958/IEC61937)

outputs using the CS42528 Mux and

XMT958 transmitter on the CS49300

On board SRAM for AAC 5.1 discrete

channel decoding

In system programmable Flash, capable of

holding 16 DSP programs

Description

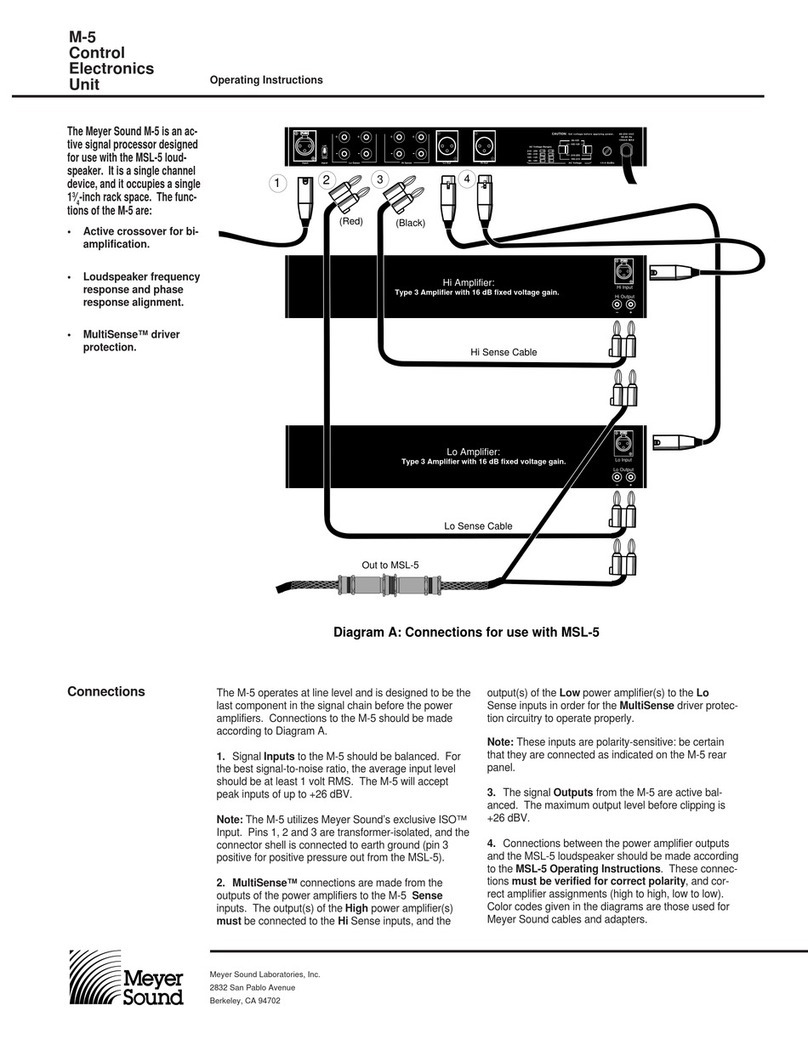

The CRD42528 is a reference design for the CS49300

DSP family and the CS42528 CODEC. It supports up to

8 channels of analog input at 48 and 96 kHz, or

2 channels of analog input at 192 kHz. One of four

digital S/PDIF inputs may be selected. Additionally, up

to 2 channels of digital S/PDIF output and 8 channels of

analog output at up to 192 kHz are supported. The on

board SRAM is included to allow for AAC 5.1 discrete

channel decoding, and on-board flash memory is

included to allow in-system programming of up to

16 DSP images. The DSP supports the following

algorithms, including (but not limited to) AAC, Dolby

Digital (AC-3), Dolby Digital EX, DTS, DTS-ES, DTS

Neo:6, Cirrus Original Surround (including COS 6.1),

SRS CircleSurround, SRS TruSurround, Pro Logic II,

MPEG Multichannel (including EX), and HDCD.

The control interface to the CRD42528 is the UDSP

System Platform. All control and data I/O is connected

to headers, which allows the CRD42528 to be used

easily in a end system or as a reference design. A larger

block diagram is shown on the next page.

ORDERING INFORMATION

CRD42528 Reference Design

CDI

AUDATA0

SAI

CX_SDIN1

AIN

RXP0 AOUT1

CS42528

IEC60958

8 x

ANALOG

4 x

SPDIF CS493XX-IBA

(or CS492XX)

CS5351

DAI

Ext ADC

In

External

SRAM/Flash

EMAD

RXP1

RXP2

RXP3

AIN SDOUT

CS5351

AIN SDOUT

CS5351

AIN SDOUT

CX_SDIN2

CX_SDIN3

CX_SDIN4

AUDATA1

AUDATA2

AUDATA3

L

R

Ls

Rs

C

Sub

SBL

SBR

L

R

Ls

Rs

C

Sub

SBL / Lt

SBR / Rt

AOUT2

AOUT3

AOUT4

AOUT5

AOUT6

AOUT7

AOUT8

CRD42528

Reference Design for the CS49300 and CS42528

MAY’ 03

DS586RD2

2

CDI

AUDATA0

SAI

CX_SDIN1

AIN

RXP0 AOUT1

CS42528

IEC60958

8 x

ANALOG

4 x

SPDIF

CS493XX-IBA

(or CS492XX)

CS5351

DAI

Ext ADC

In

External

SRAM/Flash

EMAD

RXP1

RXP2

RXP3

AIN SDOUT

CS5351

AIN SDOUT

CS5351

AIN SDOUT

CX_SDIN2

CX_SDIN3

CX_SDIN4

AUDATA1

AUDATA2

AUDATA3

L

R

Ls

Rs

C

Sub

SBL

SBR

L

R

Ls

Rs

C

Sub

SBL / Lt

SBR / Rt

AOUT2

AOUT3

AOUT4

AOUT5

AOUT6

AOUT7

AOUT8

Figure 1. Block Diagram of the CRD42528

3

TABLE OF CONTENTS

1. QUICK START................................................................................................. 5

2. DESIGN DESCRIPTION.................................................................................7

2.1 Clock and Data Connections.............................................................................................. 7

2.1.1 Analog Input Mode................................................................................................. 7

2.1.2 Digital Input Mode.................................................................................................. 7

2.2 Control................................................................................................................................ 7

2.3 Assembly Options for Ease of Manufacture....................................................................... 8

2.3.1 Analog Input Options ............................................................................................. 8

2.3.2 Analog Output Options........................................................................................... 8

2.3.3 Memory Options..................................................................................................... 9

2.4 Revision A Errata................................................................................................................ 9

APPENDIX A: Installation of Board Control Software...................................................12

APPENDIX B: CRD42528.INI........................................................................................13

APPENDIX C: Board Control Software ..........................................................................14

APPENDIX D: Schematics ..............................................................................................16

APPENDIX E: Layout Plots (Ground Plane Vias are Flooded).......................................29

APPENDIX F: Bill of Materials - CRD42528 .................................................................32

APPENDIX G: UDSP Schematics ...................................................................................37

APPENDIX H: Bill of Materials - UDSP.........................................................................46

LIST OF FIGURES

Figure 1. Block Diagram of the CRD42528..................................................................................... 2

Figure 2. Mute Control Rev A.......................................................................................................... 9

Figure 3. Mute Control - Corrected ................................................................................................. 9

Figure 4. Data and Clock Connections for 8 Channel Analog Input and Output........................... 10

Contacting Cirrus Logic Support

For all product questions and inquiries contacta Cirrus Logic Sales Representative.

To find one nearest you go to www.cirrus.com

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject

to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obt ain the latest version of relevant

information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale

supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability. No responsibility is assumed by

Cirrus for the use of this information, including use of this informationas the basis for manufacture or sale of any items, or for infringement of patents or other rights

of third parties. This document isthe property of Cirrus and by furnishing this information, Cirrus grants nolicense, express or implied under any patents, mask work

rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and

gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integratedcircuits or other products of Cirrus. This

consent does not extend to other copying such as copying for general distribution, advertising or promotionalpurposes, or forcreating any work for resale.

An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material

and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan. An export license and /or quota needs to be obtained

from the competent authorities of the Chinese Government if any of the products or technologies described in this material issubject to the PRC Foreign Trade Law

and is to be exported or taken out of the PRC.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROP-

ERTY OR ENVIRONMENTALDAMAGE ("CRITICALAPPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE

IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, LIFE SUPPORT PRODUCTS OR OTHER

CRITICAL APPLICATIONS (INCLUDING MEDICAL DEVICES, AIRCRAFT SYSTEMS OR COMPONENTS AND PERSONAL OR AUTOMOTIVE SAFETY OR SE-

CURITY DEVICES). INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIR-

RUS DISCLAIMS AND MAKES NO WARRANTY,EXPRESS,STATUTORY OR IMPLIED,INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITYAND

FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUS-

TOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS INCRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FUL-

LY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING

ATTORNEYS'FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product namesin this document may be trademarks

or service marks of their respective owners.

I

2

C is a registered trademark of Philips Semiconductor. Purchase of I

2

C Components of Cirrus Logic, Inc., or one of its sublicensed Associated Companies conveys

a license under the Philips I

2

C Patent Rights to use those components in a standard I

2

C system.

4

Figure 5. Clock and Data Connections for S/PDIF (IEC61937 / IEC60958) Input ........................11

Figure 6. Control and Data I/O......................................................................................................16

Figure 7. DSP................................................................................................................................17

Figure 8. External Memory............................................................................................................18

Figure 9. CoDec............................................................................................................................19

Figure 10. External A/D Converters..............................................................................................20

Figure 11. L/R Input Filters............................................................................................................21

Figure 12. Ls/Rs Input Filters ........................................................................................................22

Figure 13. C/Sub Input Filters .......................................................................................................23

Figure 14. SBL/SBR Input Filters..................................................................................................24

Figure 15. L/R Output Filters.........................................................................................................25

Figure 16. Ls/Rs Output Filters .....................................................................................................26

Figure 17. C/Sub Output Filters..................................................................................................... 27

Figure 18. SBL/SBR Output Filters ...............................................................................................28

Figure 19. Top Layer.....................................................................................................................29

Figure 20. Bottom Layer................................................................................................................30

Figure 21. Assembly Drawing.......................................................................................................31

Figure 22. UDSP - Top..................................................................................................................37

Figure 23. UDSP - Digital Audio Port............................................................................................38

Figure 24. UDSP - Headphone Amplifier ......................................................................................39

Figure 25. UDSP - Microcontroller ................................................................................................40

Figure 26. UDSP - Power..............................................................................................................41

Figure 27. UDSP - Parellel Port Interface .....................................................................................42

Figure 28. UDSP - RS232 Interface..............................................................................................43

Figure 29. UDSP - RS422 Interface..............................................................................................44

Figure 30. UDSP - S/PDIF I/O.......................................................................................................45

LIST OF TABLES

Table 1. Communication Mode Options..........................................................................................8

Table 2. Analog Input Assembly Options........................................................................................8

Table 3. Analog Output Assembly Options .....................................................................................8

5

1. QUICK START

A PC with an ECP parallel port, a stereo analog

audio source, and powered speakers are required to

use the CRD42528 in the mode specified in this

Quick Start.

1) Install the drivers supplied with the board on

the PC. Refer to “UDSP Schematics” on

page 37 for details on installing the drivers.

2) Connect the supplied parallel port cable to J46

on the UDSP MainBoard (marked P PORT)

and to the computer’s ECP parallel port.

3) Connect the analog output from an audio

source to AIO7-8 (Left and Right Inputs) The

input channels are mapped as follows:

- AIO8 - Left

- AIO7 - Right

- AIO6 - Left Surround

- AIO5 - Right Surround

- AIO4 - Center

- AIO3 - Subwoofer / Low Frequency Effects

(LFE)

- AIO2 - Surround Back Left

- AIO1 - Surround Back Right

4) Connect powered speakers to AIO15-16. The

output channels are mapped as follows (more

speakers can be connected to the line level

outputs as required by each application):

- AIO16 - Left

- AIO15 - Right

- AIO14 - Left Surround

- AIO13 - Right Surround

- AIO12 - Center

- AIO11 - Subwoofer or Low Frequency Ef-

fects (LFE)

- AIO10 - Surround Back Left or Lt

- AIO9 - Surround Back Right or Rt

5) Connect the supplied power supply to the

power connector on the board and to an

appropriate power outlet.

6) Verify that LEDs D1, D7, D9, and D11 on the

UDSP board are lit. LED D2 will flash to

indicate that the PLD on the UDSP is

functional.

7) Open a DOS window and navigate to the

C:\CS49300\CRD42528\Configs directory.

8) Type in “setpld -r 99” on the DOS prompt.

(This reads the PLD version register and

verifies that the PC can communicate with the

board). If the driver generates the error message

“!!! Board does not appear to be connected !!!”,

then your parallel port address may not be

0x378 or your port is not ECP capable. If your

parallel port address is not 0x378, depress the

reset switch S3 and type in “setpld -r 99 -p3bc”

or “setpld -r 99 -p278” to communicate using a

different parallel port address.

9) Verify that LED D1 (marked ERR) has turned

OFF, indicating that the driver has successfully

communicated with the board.

10)If the above steps give an error, refer to “UDSP

Schematics” on page 37 and verify that the

drivers and PC have been set up as described

(and that the parallel port address is correct / set

to ECP mode).

11)If the above steps give the expected results,

type

in “analog_in_96kHz”, “analog_in_96kHz -

p3bc”, or

“analog_in_96kHz -p278”

(depending on your parallel port address) at the

DOS prompt. This batch file will configure the

PLD, boot theDSP, and configure the CS42528

for 8 channel analog processing at 96 kHz.

12)The audio data on the Left and Right Input

connectors (AIO7-8) should now be heard on

the output.

13)The batch files use various filesto configure the

software, board, and the DSP code. Each batch

6

file has been commented. Various batch files

for the commonly used applications have been

supplied with the software. These batch files

can be run from the DOS prompt like the

“analog_in_96kHz.bat” file. Please note that

while only license-free code is supplied with

the CRD42528, a complete list of algorithms

supported by the CRD42528 (including Dolby

Digital EX and DTS-ES) is available from your

local Cirrus Logic, Inc. Field Applications En-

gineer.

Caution:Use caution while editing and making

changes to these files (editing a copy will always

insure an easily accessible backup). It is strongly

recommended that jumpers and switches on the

UDSP MainBoard be left in their default positions.

7

2. DESIGN DESCRIPTION

2.1 Clock and Data Connections

There are 2 main modes of operation of the

CRD42528, Analog Input Mode and Digital Input

Mode. In Analog Input Mode, up to 8 channels of

analog input can be processed by the DSP. In Dig-

ital Input Mode, S/PDIF (IEC61937/IEC60958)

data is sent to the DSP for decoding or processing.

In both cases, the output from the DSP is sent back

to the CS42528 to generate analog output.

2.1.1 Analog Input Mode

A detailed diagram of the clock and data connec-

tions for analog input mode can be found in

Figure 4, “Data and Clock Connections for 8 Chan-

nel Analog Input and Output,” on page 10. When

Analog Input Mode is used, the CRD42528 will

process up to 8 channels of analog input. The ana-

log source is the analog I/O connectors on the

UDSP MainBoard, which are routed directly to the

CRD42528. The Left (L) and Right (R) analog in-

puts are connected, via input filters, to the

CS42528’s analog input pins. When 6 channel (re-

ferred to as 5.1 channel) input is desired, two exter-

nal CS5351 Analog to Digital Converters are used.

These external ADCs receive the RMCK output

from the CS42528. In this mode, RMCK will pass

through the 12.288 MHz oscillator connected to

OMCK. The external ADC serial ports are driven

from the CS42528’s CX port clocks. The Left Sur-

round (Ls), Right Surround (Rs), Center (C), and

Subwoofer (Sub) inputs to the CRD42528 are con-

nected to the external CS5351’s analog inputs, and

the digital outputs from the two external CS5351s

is then connected to the CS42528’s ADCIN1/2

pins. The CS42528 will incorporate all of the data

from the external ADCs and it’s own analog input

data onto a single line and send it to the DSP via the

CS42528’s SAI port. In this way, the DSP gets the

L, R, Ls, Rs, C, and Sub channels into it’s CDI port.

For 7 or 8 channel (6.1 or 7.1 channel) operation,

another external CS5351 is used to convert the Sur-

round Back Left (SBL) and Surround Back Right

(SBR) analog inputs. Please note that many appli-

cations use a single mono surround channel, re-

ferred to as Surround Back (SB). The digital output

from the CS5351 is sent directly to the DSP’s DAI

port.

Once the DSP has processed the incoming digital

inputs, data is returned to the CS42528 to be con-

verted back to analog. The data, coming from the

DSP’s DAO port, is clocked by the CS42528’s CX

port clocks.

2.1.2 Digital Input Mode

A detailed diagram of the clock and data connec-

tions for analog input mode can be found in

Figure 5, “Clock and Data Connections for S/PDIF

(IEC61937 / IEC60958) Input,” on page 11. To

process incoming S/PDIF (IEC61937/IEC60958)

data streams, digital inputis wired directly from the

UDSP’s optical receivers to the CS42528. The

CS42528 will then lock tothe incoming stream and

convert it to an I2S data stream, which is then sent

to the DSP from the CS42528’s SAI port. This data

is input on the DSP’s CDI port. The DSP will pro-

cess this stream (i.e., decode the compressed

stream or process the PCM data), and then send up

to 8 channels of I2S data to the CS42528 on it’s

DAO port. This PCM data is input on the

CS42528’s CX port. The CS42528 then converts

the audio data back to analog.

2.2 Control

Control of the CRD42528 is done via the UDSP

headers (J2 and J3) in either SPI or I2C mode. Dif-

ferent resistors must be populated or not populated

according to the desired communication mode.

These options can be found in Table 1.

For I2C mode, please note that the DSP defaults to

address checking disabled. This can only be

changed after a firmware image has been loaded

onto the DSP (either via host boot or autoboot).

Please see the CS49300 datasheet for more details

on I2C address checking.

8

Table 1. Communication Mode Options

2.3 Assembly Options for Ease of

Manufacture

There are variety of options available on a build of

the CRD42528 that allow for different input and

output options, as well as performance differentia-

tion. This allows the same board to be used in both

low-end and high-end applications. Please note that

systemswith lowerperformance may requireexter-

nal analog Bass Management circuitry to comply

with Dolby specifications.

2.3.1 Analog Input Options

The CRD42528 supports 2, 6, or 8 channels of an-

alog input. A list of components that needs to be

populated for each configuration is shown in

Table 2.

Table 2. Analog Input Assembly Options

2.3.2 Analog Output Options

The CRD42528 supports 2, 6, or 8 channels of an-

alog output. A list of components that needs to be

populated for each configuration is shown in

Table 3.

Table 3. Analog Output Assembly Options

Mode Populate Do Not

Populate

SPI R98, R99,

R10, R12,

R16, R143

R13, R14,

R18, R100,

R144,R168,

R166

I2CR13, R14,

R18, R100,

R144,R168,

R166

R98, R99,

R10, R12,

R16, R143

Number of

Analog Input

Channels Populate Do Not

Populate

2 (L, R) R148, R149,

R150 U18, U33, U2,

Ls, Rs, C, Sub,

SBL and SBR

Input Filters

6 (L, R, Ls, Rs,

C, Sub) R150, U18, U33,

Ls, Rs, C, Sub,

SBL and SBR

Input Filters

R148, R149, U2,

SBL and SBR

Input Filters

8 (L, R, Ls, Rs,

C, Sub, SBL/Lz,

SBR/Rz)

U18, U33, U2,

Ls, Rs, C, Sub,

SBL and SBR

Input Filters

R148, R149,

R150

Number of

AnalogOutput

Channels Populate Do Not

Populate

2 (L/Lt, R/Rt) U27 = CS42516

or CS42526,

L/R Output

Filters

Ls/Rs, C/Sub,

SBL/SBROutput

Filters

6 (L, R, Ls, Rs,

C, Sub) U27 = CS42516

or CS42526,

L/R, Ls/Rs,

C/Sub Output

Filters

SBL/SBROutput

Filters

8 (L, R, Ls, Rs,

C, Sub, SBL/Lz,

SBR/Rz)

U27 = CS42518

or CS42528,

L/R, Ls/Rs,

C/Sub,

SBL/SBR

Output Filters

9

2.3.3 Memory Options

There are many available applications that can run

on the CS49300 family DSP. DSP applications re-

quire a 32k-byte page in an external ROM, Flash,

or other non-volatile storage. Some applications,

called Internal Boot Assisted (IBA) codes, consist

of a few hundred bytes of download firmware.

When using IBA codes ONLY, the external Flash

or ROM may be omitted from the design IF AND

ONLY IF the IBA codes are stored in the host mi-

crocontroller’s available non-volatile memory. In

these applications, U24 and C132 may be omitted.

For a full AAC 5.1 discrete channels of output, ex-

ternal SRAM must be used. For all other applica-

tions, the SRAM U16 and support component

C133 may be omitted. Other options exist for AAC

multichannel, including a stereo downmixed AAC

output following by Dolby ProLogic II processor,

which generates 5.1 channels of output.

For a full list of codes (including IBA codes) and

their requirements, please contact your local Cirrus

Field Applications Engineer.

2.4 Revision A Errata

The revision A CRD42528 requires the following

modification to the mute circuitry. The mute signal

as shown in Figure 2 should be modified as shown

in Figure 3.

Figure 2. Mute Control Rev A

Figure 3. Mute Control - Corrected

10

SBL / SBR Analog In

Ls / Rs / C / Sub Analog In

L / R Analog In

ADC Data

6 Channels

CX Data

8 Channels

CX Clocks(CS42528) / DAI Clocks(CS49300) at

64 Fs SCLK, LRCLK=Fs

2 Channels

SAI Data(CS42528) / CDI Data(CS49300)

SAI Clocks(CS42528) / CDI Clocks(CS49300) at

128 Fs SCLK, LRCLK=Fs

CS5351

ADCIN

4 Channels

CS5351 CX Clocks (at 64 Fs

SCLK, LRCLK=Fs) and data

ADC Data

CX Clocks (at 64 Fs

SCLK, LRCLK=Fs) and data

DAO

CS49300

CDI

DAI

CS42528

CX Port

SAI Port

AIN

AOUT

L / R / Ls / Rs / C / Sub / SBL / SBR Analog Out

Analog Input /

Output Digital Data Digital Serial Clocks

(SCLK and LRCLK)

Figure 4. Data and Clock Connections for 8 Channel Analog Input and Output

11

S/PDIF (IEC61937 / IEC60958)

2 Channels

or

Compressed

CX Data

8 Channels

CX Clocks(CS42528) / DAI Clocks(CS49300) at

64 Fs SCLK, LRCLK=Fs

SAI Data(CS42528) / CDI Data(CS49300)

SAI Clocks(CS42528) / CDI Clocks(CS49300) at

128 Fs SCLK, LRCLK=Fs

RXP

DAO

CS49300

CDI

CS42528

CX Port

SAI Port

AOUT L / R / Ls / Rs / C / Sub / SBL / SBR Analog Out

Analog Input /

Output Digital Data Digital Serial Clocks

(SCLK and LRCLK)

Figure 5. Clock and Data Connections for S/PDIF (IEC61937 / IEC60958) Input

12

APPENDIX A: INSTALLATION OF BOARD CONTROL SOFTWARE

The UDSP PC driver utility set comes in two

versions. The Direct Hardware version will

communicate directly with the PC’s parallel port to

control the UDSP board. The DLPortIO version

uses the DLPortIO driver to access the parallel port

on hardware protected operating systems.

In general, direct hardware capable operating

systems (such as Microsoft®Windows 95®,

Windows 98®, and Windows ME®) allow any

program to directly control any of the PC’s

peripherals. With the UDSP board, this allows for

faster interface speeds (up to 4 times faster).

For protected operating systems (such as

Microsoft®Windows NT®, Windows 2000®, and

Windows XP®), the UDSP driver set requires the

use of the DLPortIO driver. This utility allows the

UDSP drivers to access the parallel port safely.

The UDSP driver set requires bidirectional

communication with the UDSP board, and hence a

bidirectional capable parallel port is needed. An

ECP-type port is required. Please note that an SPP-

type port will not work with the UDSP board. The

type and location (I/O address) of the parallel port

installed can be found in the Windows Control

Panel (please see Windows Help for more

information on these settings). The UDSP drivers

assume by default that the parallel port address is

0x378. Other ports may be used with the -pXXX

option, where XXX is 3bc or 278.

Installation on Microsoft®Windows 95®,

98®, ME®and other direct hardware capa-

ble Windows®versions

1. Run “Setup.exe” from the CRD42528 CD that

was shipped with the kit.

The UDSP drivers have now been successfully

installed. The CRD42528 kit is now ready for use.

Several demonstration batch files (*.bat) are

available in the CRD42528\Configs directory.

Please see the “Quick Start” on page 5 for

information on the use of these batch files.

Installation on Microsoft®Windows NT®,

Windows 2000®, and Windows XP® and

other protected Windows®versions

1.Run “Setup.exe” from the CRD42528 CD that

was shipped with the kit.

2.Run “Port95nt.exe” from c:\udsp directory to

install the DLPortIO driver to access the parallel

port.

The UDSP drivers have now been successfully

installed. The CRD42528 kit is now ready for use.

Several demonstration batch files (*.bat) are

available in the CRD42528\Configs directory.

Please see “Quick Start” on page5 for information

on the use of these batch files.

13

APPENDIX B: CRD42528.INI

# Horizontal Fields:

# [part] [I2Caddr] [SPIaddr] [SPI CSn]

# [reset(bit to drop in PLD addr 0x01)]

# [INTREQ_NUM] [Print Format]

#[Parallel word length] [Parallel CSn]

#[Read_Type]

#

# Vertical Fields:

#board - first non-comment, non-blank line

#parts - other lines

# note: reset can only take on values 01,02

#

# Default is CS4930 interface

#

# INTREQ_NUM is the bit position within the INT register in the PLD

#

# Read_Type can be DSP or normal

#

# Word Length is in bytes

#

CRD42528

DSP 02 00 00 01 02 03 01 00 DSP

42528 9e 9e 02 02 ff 01 00 00 normal

default 02 00 00 01 02 03 01 00 DSP

14

APPENDIX C: BOARD CONTROL SOFTWARE

There is a suite of programs used to control the

UDSP from a PC DOS command line.

These software tools are designed to so that they

can be scripted using the MS-DOS batch language.

They will work with any of the 3 standard parallel

port addresses (0x378, 0x3bc, 0x278). The default

address for all of the programs is 0x378 (typically

LPT1). The port address can be changed by using

the '-p' option. Each time a program is executed, the

address that was used can be shown on the screen

using the ‘-v’ option. If a program seem

s to fail,

verification of the parallel port address should

always be the first step in troubleshooting.

All of these programs are designed to access the

daughter card connected to the UDSP board using

SPI or I2C®serial communication. The

communication mode can be chosen from the

command line with the '-m' option. The mode

chosen must correspond to the communication

mode used by the devices on the daughter card. If

the device on the board is set up for one

communication mode,and thedriversare used with

another, results will be unpredictable. All devices

on the daughter card are configured for SPI serial

communication mode by default, and that is also

the default mode for the software.

The usage of each program will vary, depending on

the type of UDSP daughter card that is installed.

The URST, URD, and UCMD programs get a valid

list of devices for the installed daughter card from

the file specified by the “uINI_path” DOS

environment variable. This file will list all of the

devices available to the UDSP parallel port drivers,

along with each device’s I2C address, SPI address,

chip select number, and reset number (for reset

capable devices). It also specifies how messages

from the device should be read. For DSP-style

reads, the driver will read until the INTREQ line

goes high. For non-DSP devices, the read operation

will read out 1 byte. Please note that most non-DSP

devices require an aborted write operation to

properly set the MAP pointer before reading.

The device list file, called CRD42528.INI, must

follow a very specific format. An example of this

can be found “CRD42528.INI” on page 13. This

file should not be changed.

A list of available drivers and their usage is found

below:

UCMD.exe - Send commands or configuration files to a target device.

Usage: ucmd <[ABCDEF..] or [-fX]> [-dZZZZ..] [-mY] [-pWWW] [-v]

-d = device

ZZZZ.. = device designator, eg dspab, dspc, 8415a, etc.

-m = communication mode

Y = mode designator (i=I2C, s=SPI*, m=MOT, n=INT)

ABCDEF.. = hex data (1-100 bytes)

-f = send configuration file

X = .cfg file containing configuration parameters

-p = parallel port address

WWW = address in hex (278, 378* or 3bc)

-v = enable verbose mode

* = default value

Example: ucmd 000001 -d4341 -p3bc

Notes: A configuration file is a list of commands, contained in an ASCII text file. This file

can be any length, and should list the commands in hex, with an even number of characters per

line. Comments can be made in the file by putting a # at the beginning of the line. The entire

line will be interpreted as a comment. Please see the accompanying *.cfg files for examples of

a configuration file.

15

URD.exe - Program used to read back responses from a target device. If a DSP-type device

is selected and the INTREQ pin is not low when URD.exe is executed, the program will wait

until INTREQ drops. Press the ‘Enter’ key to exit the read wait loop.

Usage: urd [-dZZZZ..] [-mY] [-pXXX] [-v] [-h]

-d = device

ZZZZ = device designator, eg dspab, dspc, 8415a, etc.

-m = communication mode

Y = mode designator (i=I2C, s=SPI*, m=MOT, n=INT)

-p = parallel port address

XXX = address in hex (278, 378* or 3bc)

-v = enable verbose mode

-h = this message

* = default value

EXAMPLE: urd -d4940c -p378

Notes: If the associated INTREQ pin is not low when URD is executed, the program will wait

until INTREQ drops for DSP devices ONLY. Press the ‘Enter’ key to exit the program in this case.

URST.exe - Program used to perform hard reset or soft reset on the target device.

Usage: urst [-dZZZZ..] [-mY] [-s] [-pXXX] [-v] [-h]

-d = device

ZZZZ = device designator, eg dspab, dspc, 8415a

-m = communication mode

Y = mode designator (i = I2C, s = SPI*, n = INTEL, m = MOTOROLA)

-s = Soft Reset

-p = parallel port address

XXX = address in hex (278, 378* or 3bc)

-v = enable verbose mode

-h = this message

* = default value

SetPLD.exe - Program used to read and write PLD registers.

Usage: setpld -r/-w RR [DD]

Where -r is to read from register RR, -w is to write data DD into register RR. RR and DD

are in hex.

16

APPENDIX D: SCHEMATICS

Figure 6. Control and Data I/O

17

Figure 7. DSP

18

Figure 8. External Memory

19

Figure 9. CoDec

20

Figure 10. External A/D Converters

This manual suits for next models

1

Table of contents

Popular Signal Processor manuals by other brands

Minghe Instruments

Minghe Instruments MHS-5200A Series operating manual

RoentDek

RoentDek CFD8c manual

Bass Habit

Bass Habit ELITE E28DSP user manual

Mosconi

Mosconi GLADEN ONE owner's manual

Meyer Sound

Meyer Sound Control Electronics Unit M-5 operating instructions

BSS Audio

BSS Audio Prosys PS-8810 user manual