8

8

DN-X1500

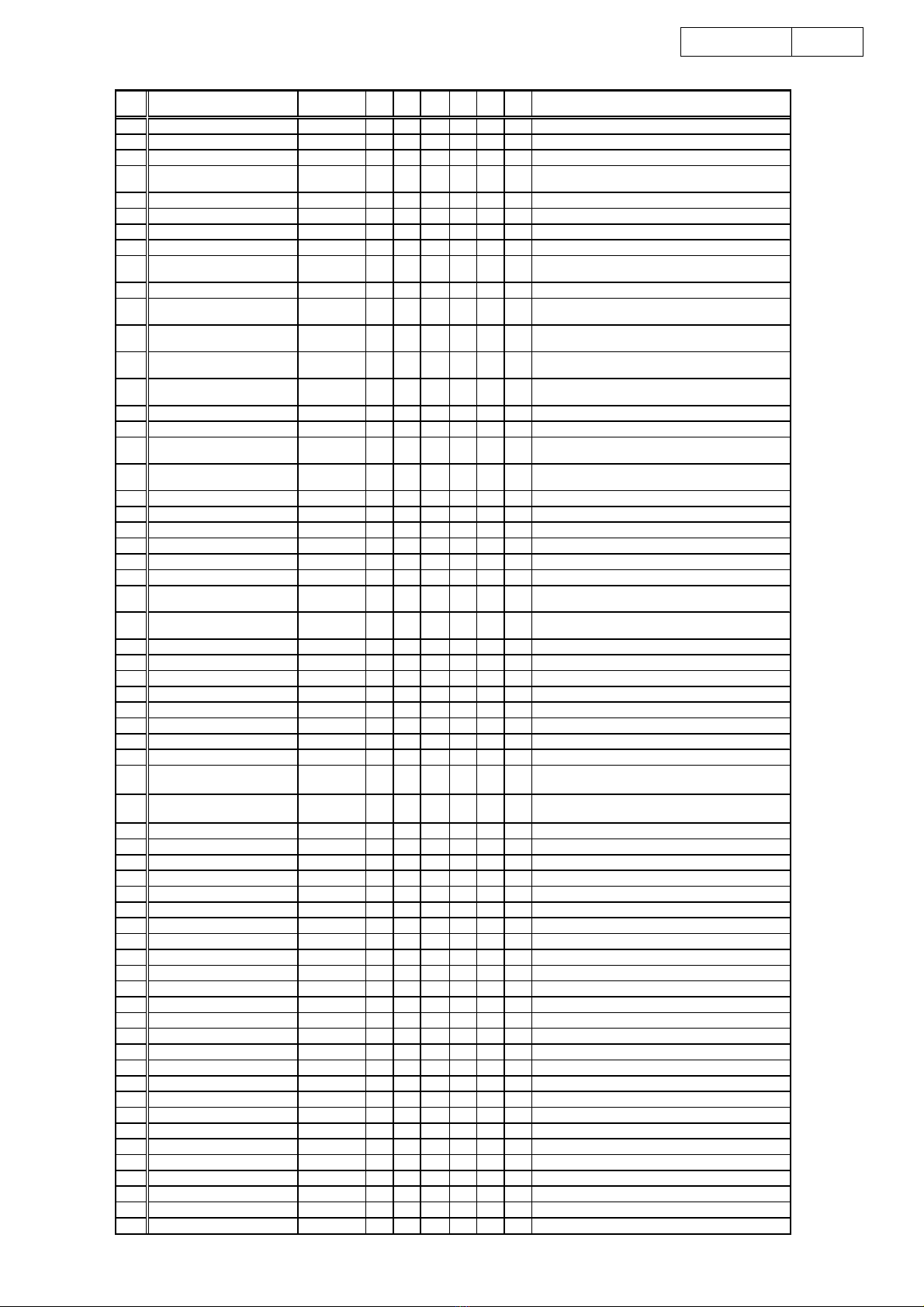

No. Pin Name Symbol I/O DET

Int

PU Ext Res Ini Function

39 P40,A16 A16 A/O - ON - Hi-z - Address bus

40 P41,A17 A17 A/O - ON - Hi-z - Address bus

41 P42,A18 A18 A/O - ON - Hi-z - Address bus

42 P43,(TM2IO),A19 A19 A/O - - Pu H -

Address bus

Need pull up to extension for DSP boot control

43 Vss Vss - - - - - - GND(0V)

44 P44,(TM3IO),A20 _CDDEC_L

O - ON - Hi-z H Latch to codec1 'L': available

45 P45,(TM4IO),A21 _CDDEC_L

O - ON - Hi-z H Latch to codec2 'L': available

46 P46,(TM5IO),A22 _DAC_CS O - ON - Hi-z H DAC chip select 'L': available

47 P47,_CS0S,(TM6IO),A23 _DIT_CS O - - Pd L H

DIT chip select

'L': available (be pull down in DSP)

48 P70,_CS1S,(TM7IO),SBI3 DIT_DIN I - ON - Hi-z H DIT data input

49 P71,_CS2S,(TM8IO),SBO3 CLOCK_A O - - Pd L L

CODEC(AD1838A)/DAC(PCM1791A)/DIT(AK4103)

data output clock signal

50 P72,_CS3S,(TM9IO),SBT3 DATA_A O - ON - Hi-z L

CODEC(AD1838A)/DAC(PCM1791A)/DIT(AK4103)

data signal

51 P80,TM10IOA,WDOUT PLGIN_L I - - Pu H H

Lch SEND/RETURN connection status

'H': connect

52 P81,TM10IOB,STOP PLGIN_R I - - Pu H H

Rch SEND/RETURN connection status

'H': connect

53 USBMODE USBMODE - - - - - - USB mode selectable terminal, connect to GND

54 Vdd Vdd - - - - - - Power supply(+3.3V)

55 D+ D+ - - - Pu - -

Connect USB terminal D+. 24

resistance is

connected in series.

56 D- D- - - - - - -

Connect USB terminal D-. 24

resistance is

connected in series.

57 Vss Vss - - - - - - GND(0V)

58 P82,SBI2 RxD I - - Pu H - 75000bps Need to convert level

59 P83,SBO2,TM11IOA TxD O - - Pu H H 75000bps Need to convert level

60 P84,SBT2,TM11IOB _MONO I - ON - Hi-z - MONO/STEREO SW 'L': MONO

61 Vss Vss - - - - - - GND(0V)

62 P90,AN0,TM12IOA ATT I Ad - - - - Adjust VR for Master output (BAL/UNBAL)

63 P91,AN1,TM12IOB _STB_CLR O - - Pd L L

TC94A32/TC9162 ALL STB set to L

'L': L set , CODEC reset

64 P92,AN2,TM13IOA CLOCK_B O - - Pd L L

Electric VR(TC94A32)/SelectorTC9162 data output

clock signal

65 P93,AN3,TM13IOB DATA_B O - ON - Hi-z L Electric VR(TC94A32)/SelectorTC9162 data signal

66 Vdd Vdd - - - - - - Power supply(+3.3V)

67 PA0,SBI1,AN4 _FPLAY1 O - - Pu H H Ch1 Fader PLAY output 20msec 'L' pulse

68 PA1,SBO1,AN5,SDA1 _FCUE1 O - - Pu H H Ch1 Fader CUE output 20msec 'L' pulse

69 PA2,SBT1,AN6,SCL1 _FPLAY2 O - - Pu H H Ch2 Fader PLAY output 20msec 'L' pulse

70 PA3,SBI0,AN7 _FCUE2 O - - Pu H H Ch2 Fader CUE output 20msec 'L' pulse

71 PA4,SBO0,SDA0 _FPLAY3 O - - Pu H H Ch3 Fader PLAY output 20msec 'L' pulse

72 PA5,SBT0,SCL0 _FCUE3 O - - Pu H H Ch3 Fader CUE output 20msec 'L' pulse

73 TEST1 SBD4 I - - Pu - -

Pull up 4.7kΩ〜10kΩConnection output for

onboard write of internal form.

74 TEST2 SBT4 I - - Pu - -

Pull up 4.7kΩ〜10kΩConnection output for

onboard write of internal form.

75 _NMI _NMI I Lv - - H H

76 PB0,_IRQ0 _DSP_BPM I Ed ON - - Trigger terminal for BPM counter by DSP

77 PB1,_IRQ1 DSP_COM O - - Pu H - System <-> DSP REQ2 signal

78 PB2,_IRQ2 RESERVE4 I - - Pu H - Signal for test

79 PB3,_IRQ3 MUTE O - - Pu H H Analog/Digital mute 'H': Mute ON

80 PB4,_IRQ4 _FPLAY4 O - - Pu H H Ch4 Fader PLAY output 20msec 'L' pulse

81 PB5,_IRQ5 _FCUE4 O - - Pu H H Ch4 Fader CUE output 20msec 'L' pulse

82 _RST _RESET I Lv - - L - Reset signal 'L': Reset

83 Vdd Vdd - - - - - - Power supply(+3.3V)

84 P00,D00 D00 D/O - ON - Hi-Z - Data bus

85 P01,D01 D01 D/O - ON - Hi-Z - Data bus

86 P02,D02 D02 D/O - ON - Hi-Z - Data bus

87 P03,D03 D03 D/O - ON - Hi-Z - Data bus

88 P04,D04 D04 D/O - ON - Hi-Z - Data bus

89 P05,D05 D05 D/O - ON - Hi-Z - Data bus

90 P06,D06 D06 D/O - ON - Hi-Z - Data bus

91 P07,D07 D07 D/O - ON - Hi-Z - Data bus

92 Vss Vss - - - - - - GND(0V)

93 P010,D08,(TM2IO) D08 D/O - ON - Hi-Z - Data bus

94 P011,D09,(TM3IO) D09 D/O - ON - Hi-Z - Data bus

95 P012,D10,(TM4IO) D10 D/O - ON - Hi-Z - Data bus

96 P013,D11,(TM5IO) D11 D/O - ON - Hi-Z - Data bus

97 P014,D12,(TM6IO) D12 D/O - ON - Hi-Z - Data bus

98 P015,D13,(TM7IO) D13 D/O - ON - Hi-Z - Data bus

99 P016,D14,(TM8IO) D14 D/O - ON - Hi-Z - Data bus

100 P017,D15,(TM9IO) D15 D/O - ON - Hi-Z - Data bus