Enova Technology X-Wall MX+ User manual

Enova Technology Confidential Page 1 of 5

X-Wall MX+ Dev Board Quick Guide Rev 1.1 10102015

X-Wall MX+ Dev Board Quick Guide Rev 1.1

Ordering SKU:

MX+_DEV_R1

Product Description:

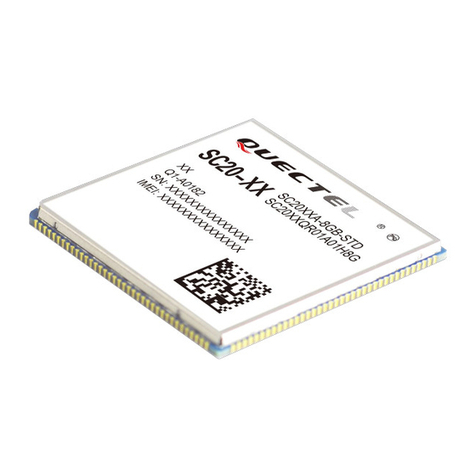

SATA-to-SATA real-time crypto module development board with selectable AES

ECB/CBC/CBC with Tweak/XTS 2 6-bit encryption strength at SATA Generations 3 (6

Gb/second,) generation 2 (3 Gb/second,) and generation 1 (1. Gb/second) speed.

Revision History

Rev No.

Description

Author

Rev. Date

0.1 Draft release Butz Huang

Dr.

C.Y Chiu

03/0 /201

1.0

General Editing

R. Wann

0

9

/10/201

1.1

General Editing; Add words

of cautions

; Add SKU

R. Wann

10/10/201

Asia Pacific North America

Enova Technology Corporation Enova Technology

1

st

Floor, #11, Research & Development 2

nd

Rd. 1918 Junction Avenue

Science-based Industrial Park, Hsin-Chu City San Jose, California 9 131, USA

Taiwan 30076, Republic of China P +1 10 82 7900

P +886 3 77 2767 F +886 3 77 2770 http://www.enovatech.com

www.enovatech.net; info@enovatech.net; www.enovatech.com;

inf[email protected]om

Enova Technology Confidential Page 2 of 5

X-Wall MX+ Dev Board Quick Guide Rev 1.1 10102015

Overview

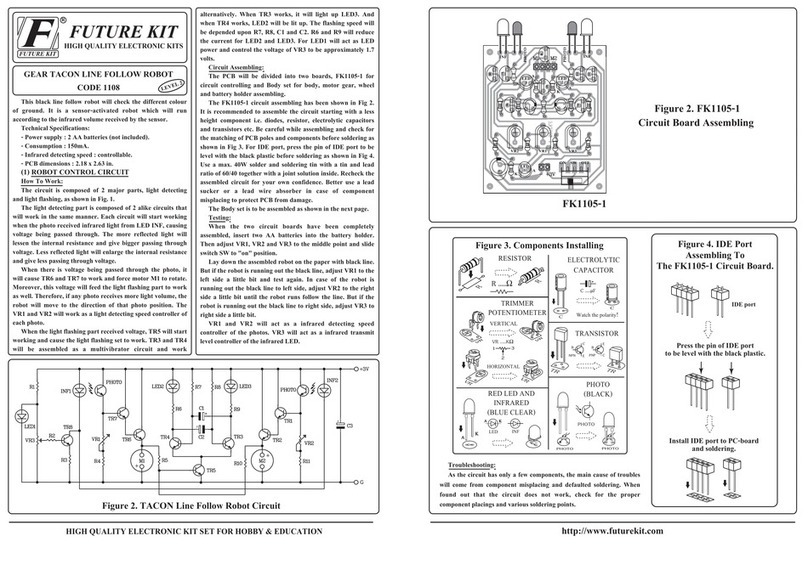

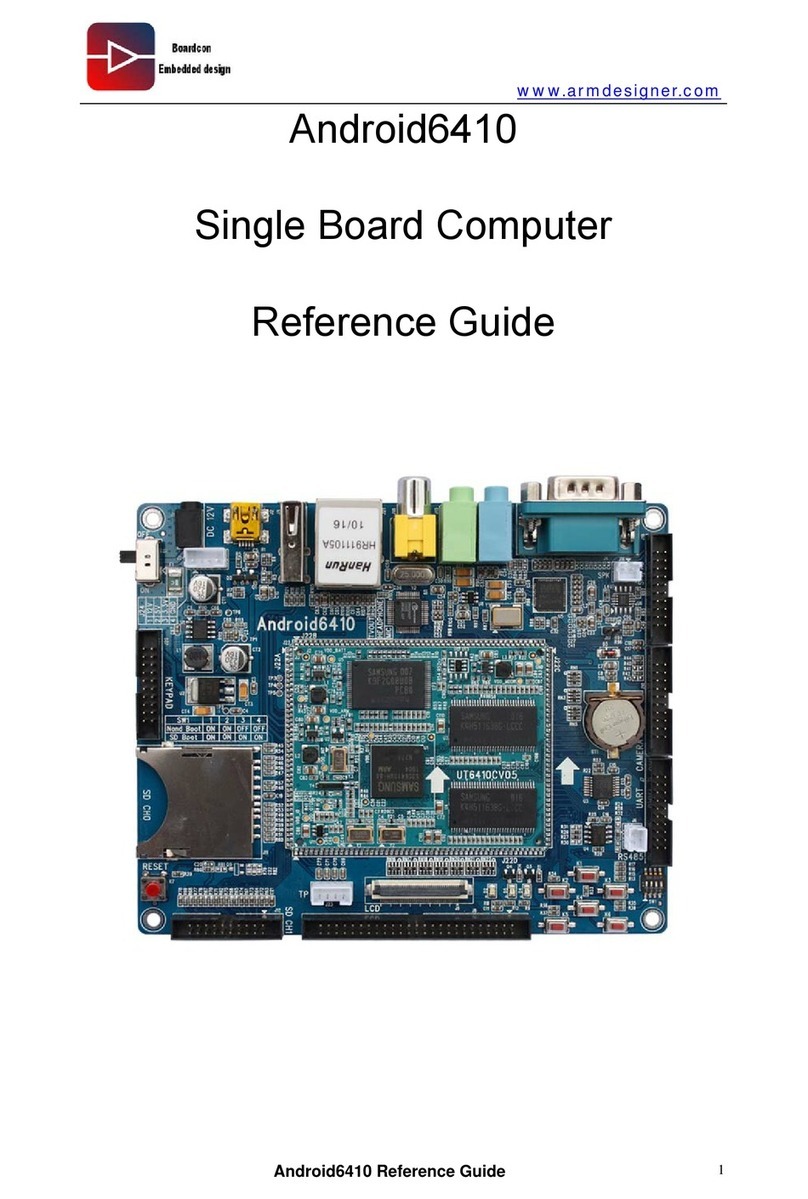

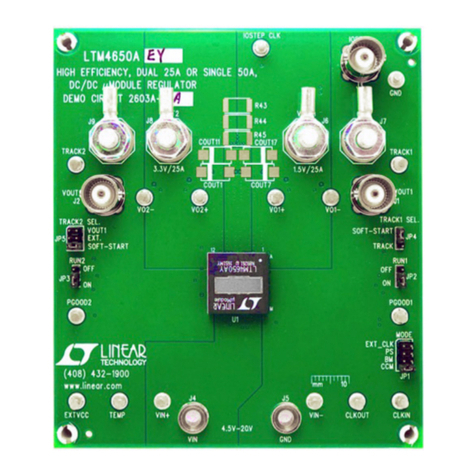

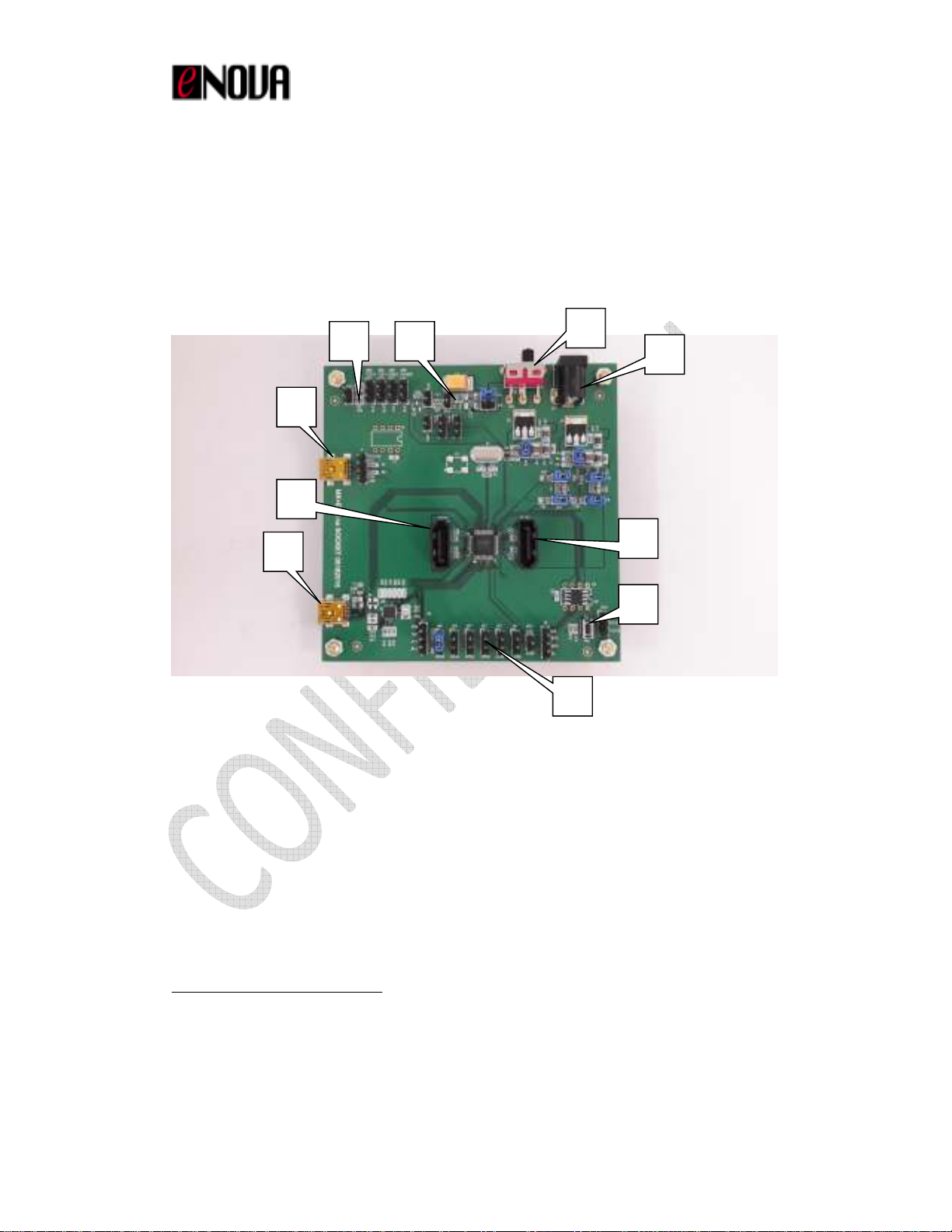

The X-Wall MX+ Development Boa d has been catego ized into seve al functional

blocks f om A to J with each ep esenting diffe ent o combined functions. Detailed

desc iptions ove va ious functional blocks a e p ovided in Table one below. It’s

impo tant that you ead th ough the table desc iptions p io to any ope ation of you

MX+ Development Boa d.

This X-Wall MX+ development boa d facilitates enginee ing design effo t integ ating

the X-Wall MX+ SATA eal-time c yptog aphic module capable of pe fo ming up to

6Gb/sec c yptog aphic output in AES CBC/CBC with Tweaks/XTS/ECB mode of

ope ation with 256-bit st ength. The p ima y objective of using the X-Wall MX+ is to

enc ypt (Full Disk Enc yption, o SED) enti e connected SATA sto age d ive ega dless

of its geomet y.

In addition to the Full Disk Enc yption (FDE) function, with the addition of TCG OPAL

2.0

1

and IEEE1667 fi mwa e, the MX+ solution can conve t any standa d SATA disk

1

TCG OPAL2.0 is a sophisticated multi-tier authentication protocol capable of defining specific user’s

READ/WRITE access privilege over a specified range of a logical drive. Note that a logical drive may

contain up to a total of 8 user ranges, in addition to the Global range, with each range taking up

specified LBA starting and ending address.

A

B

C

D

E

F

G

H

J

K

Enova Technology Confidential Page 3 of 5

X-Wall MX+ Dev Board Quick Guide Rev 1.1 10102015

d ive to meet Mic osoft Ha dwa e Enc ypted D ive specification to allow fast and

economic deployment of any SATA d ive. The addition of TCG OPAL2.0 and IEEE1667

fi mwa e is optional. Please consult with you sales ep esentative fo licensing

info mation.

Mo e, in addition to the Full Disk Enc yption (FDE) function, with the addition of TCG

OPAL2.0 fi mwa e, the MX+ solution can conve t any standa d SATA disk d ive to

meet with TCG OPAL2.0 d ive specification. The addition of the TCG OPAL2.0

fi mwa e is optional. Please consult with you sales ep esentative fo licensing

info mation.

Fu the mo e, the new MX+ has equipped with othe essential FIPS ce tified

ha dwa e c ypto modules and softwa e se vices including:

√

RSA 2048 bits PKI – ha dwa e c ypto module fo P ivate/Public key pai gene ation,

sign and ve ify;

√

DRBG RNG – ha dwa e c ypto module fo seeding mate ial and andom numbe

gene ation;

√

HMAC – ha dwa e c ypto module fo Hashed Message Authentication Code;

√

SHA256 – ha dwa e c ypto module fo ha dwa e hash;

√

AES CBC CBC with Tweaks XTS ECB block ciphers – ha dwa e c ypto module with

selectable AES mode of ope ation fo eal-time block ciphe ing;

√

TCG OPAL 2.0 – softwa e se vice fo secu e authentication th ough OPAL; and

√

IEEE1667 – softwa e se vice fo authentication in host attached t ansient sto age

device.

Like its p edecesso MX, the new MX+ p ovides two inte faces, which a e mutually

exclusive fo accessing, to pe fo m authentication: 1.) built-in two wi es se ial

inte face in eithe Maste o Slave mode; and 2.) SATA API command sets and

lib a ies

2

via SATA host adapte . Fo those designs that have onboa d mic o

cont olle o FPGA with I2C capability can choose MX+ built-in 2-wi e se ial inte face.

Alte natively, fo those designs that have cont ol ove thei system ke nel and/o

BIOS may opt fo the MX+ SATA API command set and lib a ies as an integ al solution.

2

SDK for developers is available in both Windows and Linux. A valid Software License Agreement is

required.

Enova Technology Confidential Page 4 of 5

X-Wall MX+ Dev Board Quick Guide Rev 1.1 10102015

Communications using both inte faces may be enc ypted using one o mo e of

available built-in ha dwa e c yptog aphic modules o softwa e se vices as an option.

Noted howeve , the default of this development boa d uses clea text

communication.

Table 1 – Description for various partitions

Partition Description

A V DC Jack. Connect to power adaptor with center pin 2mm and output V/1A (min).

B Power switch.

C SATA#2 Connector – Connect to SATA Host using premium quality SATA cable.

D SATA#1 Connector – Connect to SATA storage device using premium quality SATA cable.

E Mini-USB Connector – Connect to Enova standard I2C key fob that supplies AES Secret Key.

F Mini-USB connector for UART output – Connect to a PC USB port through an on-board

USB-to-UART controller SiliconLab CP2104.

G V power LED indicator

H RESET button

I Jumper Setting Group 1 (Reserved for manufacturer. DO NOT TOUCH.)

J Jumper Setting Group 2 (See detailed description below)

K Error indicator (D2). Data transfer indicator (D3).

All jumpers may be set to 1 or 0 by shorting to Vcc or ground.

Table 2 - Jumper Setting Group 1

NAME Default Description

JP18 PHYMOD 0 Reserved for Manufacturer. DO NOT

TOUCH.

JP19 TEST0 0

JP20 TEST1 0

JP21 DEBUG 0

Table 3 - Jumper Setting Group 2

NAME Default Description

JP1 GPIO0 0 Reserved

JP2 GPIO1 0 Reserved

JP3 GPIO2 0 Reserved

JP4 GPIO3 0 Reserved

Enova Technology Confidential Page 5 of 5

X-Wall MX+ Dev Board Quick Guide Rev 1.1 10102015

JP GPIO4 0 Reserved

JP6 GPIO 0 Close/Set to Vcc: MX+boots from

external SPI flash.

Open/Set to Ground (default): MX+

boots from internal ROM.

Words of Cautions

To avoid unpredicted operational behavior and to enhance user’s experience of the MX+ development

board, please observe the following critical requirements:

1. Use a reliable external power supply with Volts and 3 Amps at least;

2. Use premium SATA cables for a stable 6Gbps connection;

3. Do not apply the power to your host and storage drive; and

4. Ensure the following power on sequences are followed exactly:

4a. properly attach the power supply unit and use SW1 to power on the development board;

4b. Press and hold PB1 for at least a period of 3 seconds the release it; and

4c. Power on your host and storage drive

For occasion that the storage drive connected after the MX+ development board isn’t properly

recognized after you had performed above steps 1 through 4, power down your host and storage drive

then repeat the steps 1-4. Alternatively, contact your sales representatives to arrange for technical

support.

Quick installation with Enova I2C key fob

3

1. Connect power adaptor;

2. Connect SATA#2 connector to your motherboard SATA host adapter;

3. Connect SATA#1 connector to your SATA storage device (SSD and/or Hard Drive);

4. Insert Enova I2C key fob to the connector E;

. Power on the power switch B;

6. Manually reset MX+ by pushing reset button H;

7. Power on your system. The SATA disk drive should be recognized under OS.

3

Note that key format of the X-Wall MX+ differs from that of the X-Wall MX. The old key format is not

compatible with the new X-Wall MX+. Consult Enova sales at info@enovatech.com for the utility

program that generates new MX+ key format and writes the key directly to the connected key fob.

Table of contents