Installation of ROM Socket

* Do not apply force to the actuator cover after ic inserted.

* Do not apply force to actuator cover when it is opening over 120

degree, Otherwise, the actuator cover may be broken.

* The yellow dot (Pin1) on the ROM must be installed at pin1 position of

the socket (white arrow area).

* Make sure the white dot on the ROM is installed outwards of the

socket.

* For further details of how to install ROM, please refer to ASRI website.

Warning: If the installation does not follow as the picture, then it

may cause severe damage to chipset & MB.

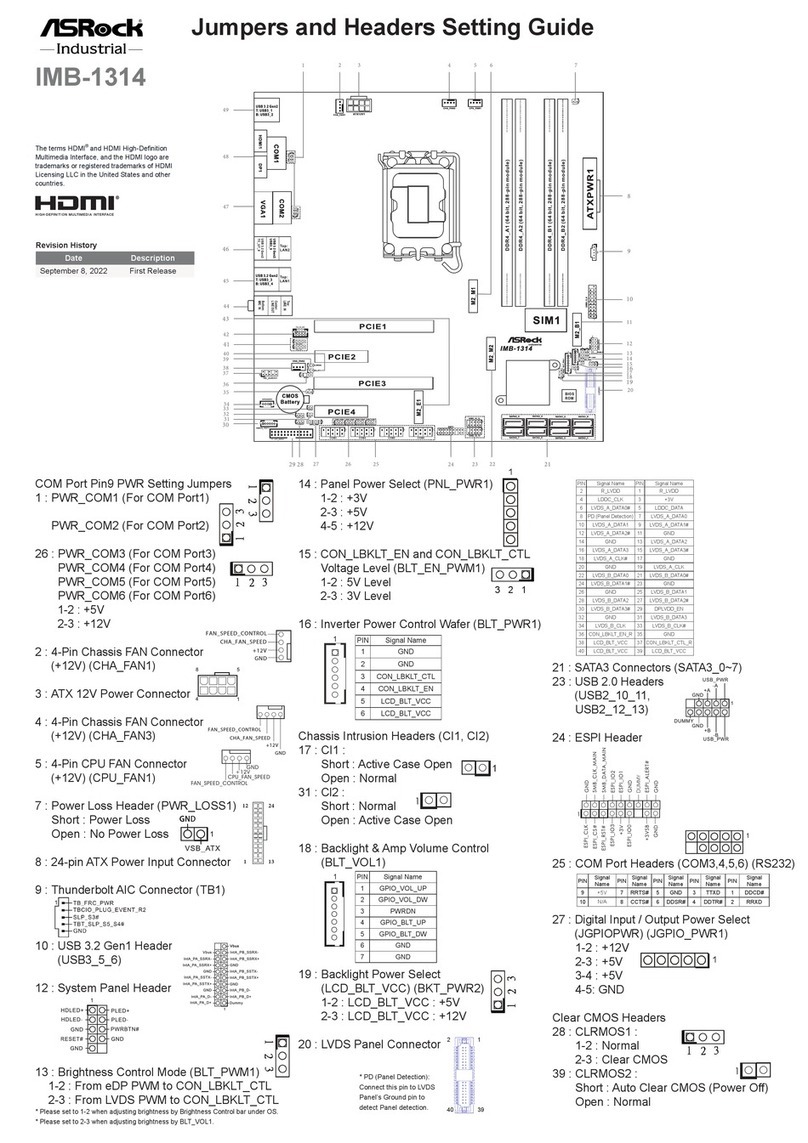

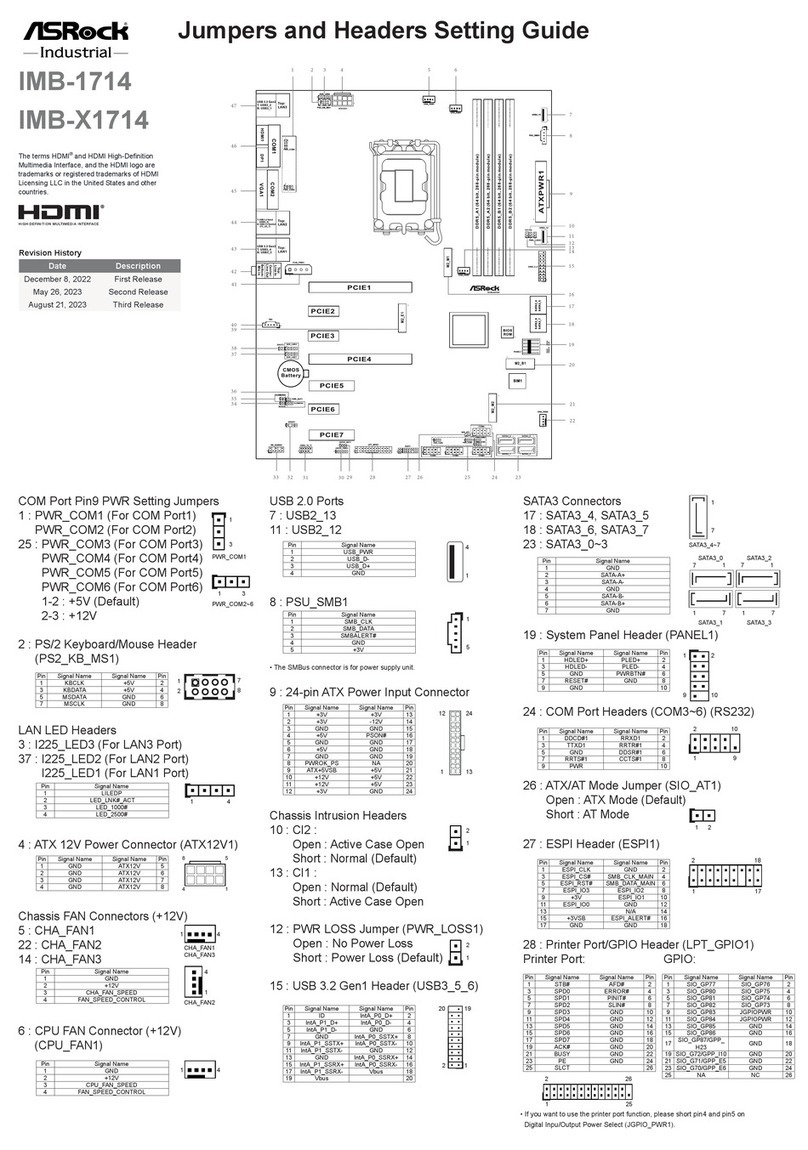

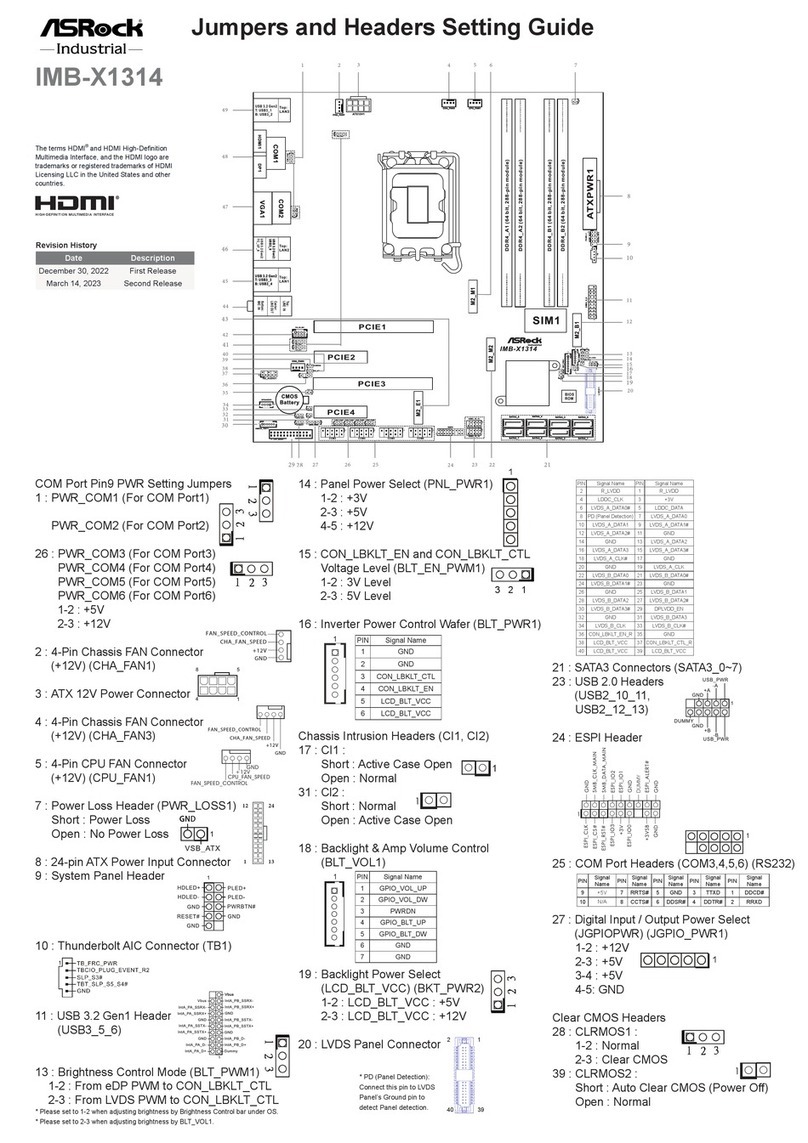

16 : Panel Power Select

(LCD_VCC) (PNL_PWR1)

1-2: LCD_VCC: +3V

2-3: LCD_VCC: +5V

4-5: LCD_VCC: +12V

17 : Clear CMOS Header (CLRMOS1)

1-2: Auto Clear CMOS

2-3: Clear CMOS

18 : COM Port Headers

(COM1~6)

19

:

System Panel Header

20 : SMB_TEST1

21 : COM Port PWR Setting Jumpers

PWR_COM1~6 (For COM Port1~6)

1-2: +5V

2-3: +12V

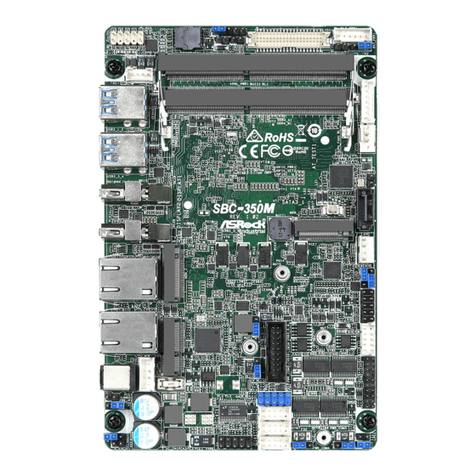

Industrial

IMB-1235

Mic In

1

HD_AUDIO1

Line Out

DC_4PIN1

SATA3_1 SATA3_0

SPDIF1

1

SATA_PWR1

1

HDLED RESET

PLE D PWR BTN

PANEL1

1

DDR4_B1

DDR4_A1

BAT1

1

CPU_FAN1

DC_JACK1

HDMI1

HDMI2

USB3_3

1

BLT_VOL1

1

BKT_PWR1

LVDS1

1

COM4

1

JGPIO_PWR1

JGPIO1

1

SMB_TEST1

USB 2.0

T: USB2_3

B: USB2_4

M2_B1

DACC1

1

ESPI1

RoHS

M2_E1

M2_M1

BLT_PWM1

1

BIOS

ROM

SIM1 BUZZ1

1

COM5

1

COM6

1

COM1

1

COM2

1

COM3

1

111

PWR_COM4 PWR_COM5 PWR_COM6

111

PWR_COM1 PWR_COM2 PWR_COM3

1

JGPIO_SET1

PSON#_1

11

1

1

SIO_AT1

CI1

1

BUZZ2

CI2

1

CLRMOS1

1

PNL_PWR1

1

EDP_BLT_PWR1

1

BLT_PWR1

1

LAN1

LAN2

USB 3.2 Gen2

T: USB3_1

B: USB3_2

Thunderbolt

Type-C

(TC_T1)

Thunderbolt

Type-C

(TC_T0)

SPEAKER1

1

12

11 (*Backside: EDP1)

10

18

3

245679

15

13

14

17

16

18

21

22

2728

29

31

34 33 32 30 24

26 25 23

19

44

41

40

43

42

39

36

35

38

37

20

46

45

BLT_PWM2

1

1

1

3 2 1

PIN Signal

Name PIN Signal

Name PIN Signal

Name PIN Signal

Name PIN Signal

Name

1DDCD# 3TTXD 5GND 7RRTS# 9PWR

2RRXD 4DDTR# 6DDSR# 8CCTS#

2

1

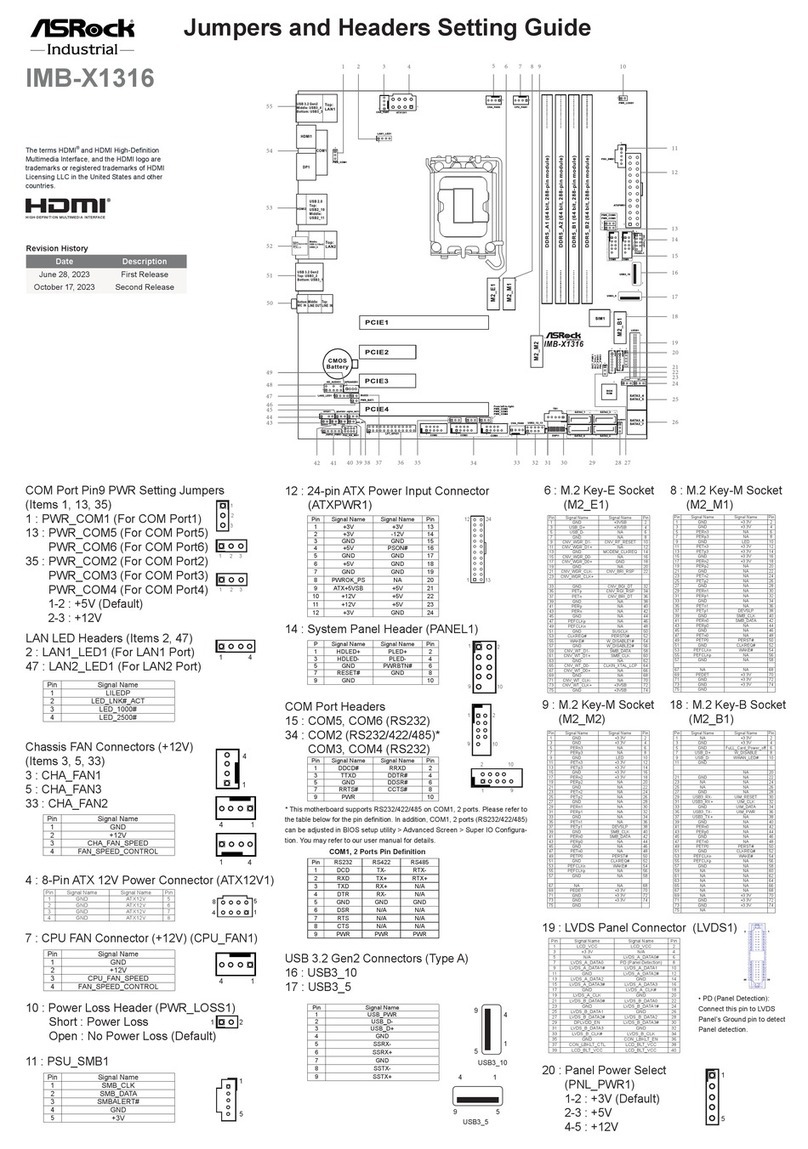

* This motherboard supports RS232/422/485 on COM1, 2 ports.

Please refer to table below for the pin denition. In addition, COM1, 2

ports (RS232/422/485) can be adjusted in BIOS setup utility >

Advanced Screen > Super IO Conguration. You may refer to our

user manual for details.

PIN RS232 RS422 RS485

1 DCD TX- RTX-

2 RXD RX+ N/A

3 TXD TX+ RTX+

4 DTR RX- N/A

5 GND GND GND

6 DSR N/A N/A

7RTS N/A N/A

8 CTS N/A N/A

9 PWR PWR PWR

COM1, 2 Port Pin Denition

PIN Signal Name

1 GPIO

2 SMB_CLK_MAIN

3 SMB_DATA_MAIN

4 GND

5Time SYNC

* Auto clear CMOS when system boot improperly.

22 :

Digital Input / Output

Default Value

Setting (JGPIO_SET1)

1-2: Pull-High

2-3: Pull-Low

23 : Digital Input/Output Pin

Header (JGPIO1)

24 :

Digital Input / Output Power Select

(JGPIO_PWR1)

1-2:

+12V

2-3:

+5V

25 : DACC1

Open: No ACC

Short: ACC

26 : PSON#_1

27 :

ATX/AT Mode Jumper (SIO_AT1)

Open: ATX Mode

Short: AT Mode

28 : Chassis Intrusion Headers (CI1, CI2)

CI1:

Open: Normal

Short

: Active Case Open

CI2:

Open: Active Case Open

Short

: Normal

29 : ESPI Header (ESPI1)

3 2 1

1

2

9

10

PIN Signal Name PIN Signal

Name PIN Signal

Name PIN Signal

Name PIN Signal

Name

9 JGPIOPWR_R 7 SIO_

GP74 5SIO_

GP73 3SIO_

GP72 1SIO_

GP71

10 GND 8 GPP_

E13 6 GPP_E2 4 GPP_E1 2 GPP_D4

3 2 1

1

1

1

30 : Buzzer (BUZZ2)

31 : Buzzer (BUZZ1)

32 : SIM Socket (SIM1)

33 : Battery Connector

34 :

Front Panel Audio Header

35 :

3W Audio AMP Output Wafer (SPEAKER1)

36 :

SPDIF Header

37 : Audio Jack: Pink - Mic In

38 : Audio Jack: Green - Line Out

39 :

USB2.0

Ports (USB2_3_4)

40 : RJ45 LAN Port (LAN2)

41 : RJ45 LAN Port (LAN1)

42 :

USB3.2 Gen2

Ports (USB3_1_2)

43 : Top: HDMI Port (HDMI1)

Bottom: HDMI Port (HDMI2)

44 : Thunderbolt Type-C Port (TC_T0)

45 : Thunderbolt Type-C Port (TC_T1)

46 : DC Jack (DC_JACK1)

1

PIN Signal

Name

4 OUTRN

3 OUTRP

2 OUTLP

1 OUTLN

* Connect to PCIE_ISOLATION_1 header on VGA-PWR card.

PIN Signal

Name PIN Signal

Name

2 GND 1 PSON#

1

1

PIN Signal

Name PIN Signal

Name

1 +5V 2 BUZZ_

LOW

PIN RS232

20 GND

19 ESPI_ALERT#

18 Internal Use

17 Internal Use

16 +3VSB

15 GND

14 ESPI_IO3

13 ESPI_IO2

12 ESPI_IO1

11 ESPI_IO0

10 SMB_DATA

9 SMB_CLK

8 GND

7 +3V

6 GND

5 ESPI_RESET#

4 ESPI_CS#

3 GND

2 ESPI_CLK

1 GND

J_SENSE

OUT2_L

MIC_RET

PRESENCE

GND

OUT2_R

MIC2_R

OUT_RET