GATEWORKS Venice GW720 User manual

Venice Single Board Computer Operating Manual

TABLE OF CONTENTS

TABLE OF CONTENTS 2

INTRODUCTION 4

Product Description 4

Standard Features 4

Ordering Options – Standard Configuration* 5

Ordering Options – Accessories 5

Feature Locations 6

Functional Blocks 8

ARMv8 Processor 9

DDR4 SDRAM 9

System Flash 9

Mini-PCIe Sockets 9

USB Support 9

PCIe Socket Reset & WiFi Disable 10

Micro-SD and Nano SIM Expansion 10

GbE Ethernet 10

USB Ports 11

Peripheral Expansion 11

Digital I/O 11

Serial I/O 11

Analog Input 11

System Reset 11

I2C Two Wire Interface 11

SPI Serial Peripheral Interface 12

Gateworks System Controller 12

Real Time Clock with Battery Backup 12

System Temperature and Voltage Monitor 12

Configuration EEPROM 13

Fan Speed Control 13

Additional System Level Functions 13

Battery Backup 13

3-Axis Accelerometer/Magnetometer 14

Optional GPS Receiver 14

JTAG Programming Port 15

MIPI DSI & MIPI CSI 15

Status LEDs 15

Power Architecture 16

Barrel Jack Power 16

802.3at Active Power over Ethernet 16

Passive Power over Ethernet 16

Switching DC/DC Regulators 17

CONNECTORS 18

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

2 of 32

Venice Single Board Computer Operating Manual

Micro-SD Flash and Cellular Nano SIM Expansion Socket (J1) 18

Battery Coin Cell Socket (J2) 18

Serial Peripheral Interface (SPI) Expansion (J3) 18

MIPI CSI and DSI Header (J4) 19

Peripheral Expansion (J5) 19

SOM Header (J6 & J9) 20

Test Header (J7) 20

Mini-PCIe (J8 & J10) 21

Software Programmable RS232/422/485 Serial Port (J11) 21

5V Fan Speed Control (J12) 22

External Tamper Switch (J13) 22

Optional GPS MMCX or u.FL Antenna (J14) 23

Optional Input Power (J15) 23

Input Power Barrel Jack (J16) 23

Gigabit Ethernet Ports and Passive PoE Input Power (J17) 23

Optional USB Type-A Socket (J18) 24

USB OTG Port (J19) 24

Optional Pushbutton Switch Connector (J20) 24

JTAG Programming and Serial Console (SOM J4) 25

SOFTWARE 26

Getting Started 26

Gateworks System Controller 26

JTAG Programming 26

Manufacturer's Website Links / Support Mailing List 27

SPECIFICATIONS 28

Electrical 28

Environmental 28

Mechanical 28

CUSTOMER SUPPORT 31

Product Revision History 31

Technical Assistance 31

Warranty 31

Return for Repair 31

Life Support Policy 32

Copyright & Trademarks 32

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

3 of 32

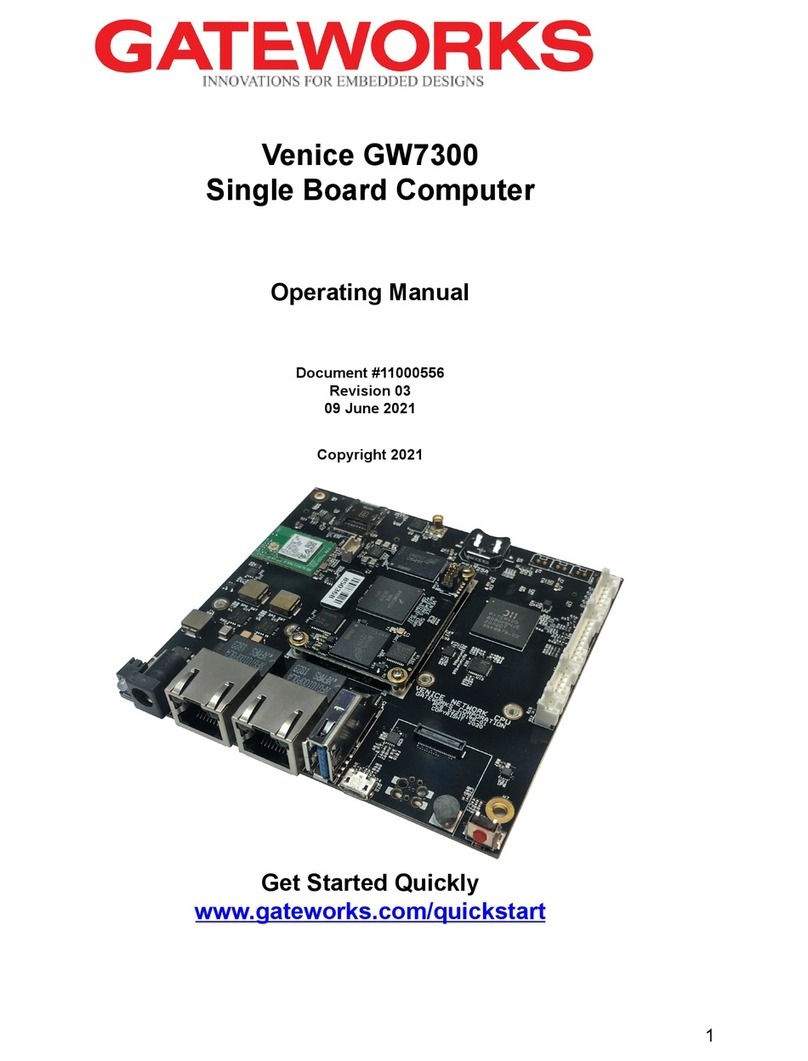

Venice Single Board Computer Operating Manual

1. INTRODUCTION

1.1. Product Description

The GW7200-00 is a member of the Gateworks 7th generation Venice family of single

board computers targeted for small embedded applications such as IoT Gateways,

Machine Learning, Unmanned Aerial Vehicles (UAV) equipment, digital signage, and

robotics. The GW7200-00 features the 64-bit NXP™ i.MX8M Mini Quad Core ARM®

Cortex™-A53 SoC processor operating at 1.6GHz, 1GBytes of LPDDR4 DRAM, and

8GBytes of eMMC System Flash. Two Mini-PCIe expansion sockets can be used for

802.11ax/ac/b/g/n WiFi radios, 5G/4G/3G/CATM1 cellular modems and other PCI

Express peripherals. Peripheral headers support Digital I/O, Analog Input, RS232/485

and TTL Serial, I2C and SPI. A combined MIPI-DSI/CSI header with I2S audio offers

video input/output. A dual configuration connector supports both MicroSD & Nano SIM

simultaneously. A 3-Axis accelerometer is standard. An optional GPS is available. The

Gateworks System Controller provides embedded features such as real time clock,

voltage and temperature monitor, serial EEPROM, programmable pushbutton switch,

and advanced power management with programmable board shut-down and wake-up

for remote sensor applications. A wide-range DC input power supply provides up to

16W of power to the Mini-PCIe sockets for supporting the latest high-power radios.

Power is applied through a dedicated barrel jack or an Ethernet port in an active

802.3af/at or passive Power over Ethernet (PoE) architecture. Ubuntu Linux BSP is

supported.

1.2. Standard Features

● NXP™ 64-bit i.MX8M Mini 1.6GHz Quad Core ARM

● 1GByte LPDDR4-2133 SDRAM Memory

● 8GBytes eMMC Flash System Memory

● Two High-Power Gen 2 Mini-PCIe Sockets with USB 2.0 and Nano SIM

● MicroSD & Nano SIM slots

● Two GbE Ethernet Ports supporting 802.3at/af and Passive PoE

● Digital I/O & Analog Expansion

● RS232/RS485 and TTL Serial Expansion

● I2C & SPI Expansion

● USB 2.0 OTG Port

● MIPI-DSI and MIPI-CSI Port

● Serial Audio In/Out

● Digital 3-axis Accelerometer/Magnetometer

● Optional u-blox GPS Receiver with MMCX Antenna Connector

● Real Time Clock with Battery Backup

● Voltage and Temperature Monitor

● Serial Configuration EEPROM

● Programmable Watchdog Timer

● 8 to 60VDC Input Voltage Range

● Power Through Barrel Jack Connector or 802.3af/at Active or Passive PoE

● 6W@25°C Typical Operating Power

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

4 of 32

Venice Single Board Computer Operating Manual

● 16W Available for Mini-PCIe Sockets

● Reverse Voltage Protection

● -40°C to +85°C Operating Temperature

● Ubuntu Linux Board Support Package

● 1 Year Warranty

1.3. Ordering Options – Standard Configuration*

Order Code

ARMv8

processor

SDRAM

Flash

Operating

Temp

Peripherals

GW7200-00

Quad Core @

1.6GHz

1GByte

8GBytes

-40℃ to

+85℃

Standard

GW7200-01

Quad Core @

1.6GHz

4GByte

64GBytes

-40℃ to

+85℃

Standard

GW7201-00

Quad Core @

1.6GHz

1GByte

8GBytes

-40℃ to

+85℃

+GPS

GW7201-01

Quad Core @

1.6GHz

4GByte

64GBytes

-40℃ to

+85℃

+GPS

* Contact factory for different configurations of CPU, DRAM, Flash, and support

peripherals

1.4. Ordering Options – Accessories

Order Code

Description

GW11033

USB JTAG Programmer 10-pin Kit (Contains GW16099)

GW10054

Gigabit PoE Injector

GW10030

24V Supply

GW11048

Development Kit, Includes GW7200 SBC

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

5 of 32

Venice Single Board Computer Operating Manual

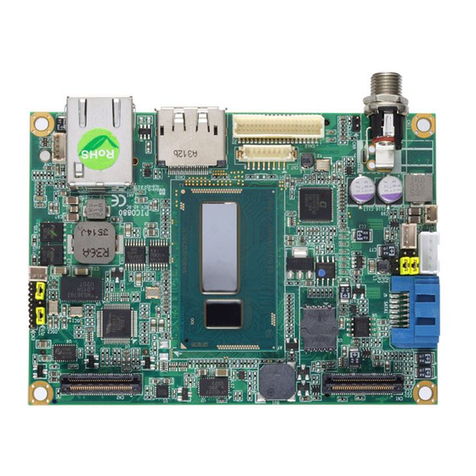

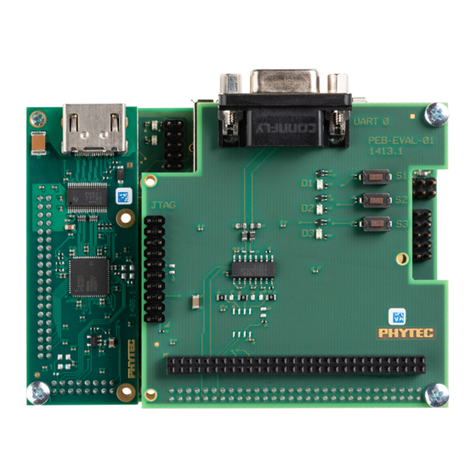

1.5. Feature Locations

Top Side Features

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

6 of 32

Venice Single Board Computer Operating Manual

Bottom Side Features

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

7 of 32

Venice Single Board Computer Operating Manual

1.6. Functional Blocks

The functional block diagram is shown below followed by a detailed description of each

major functional block.

Functional Block Diagram

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

8 of 32

Venice Single Board Computer Operating Manual

ARMv8 Processor

The 64-bit NXP™ i.MX8M Mini Quad Core ARM® Cortex™-A53 SoC processor

includes many peripherals for supporting secure network and multimedia processing

and connectivity in small embedded applications.

● Quad Cortex-A53 processing cores

● Core operating frequency of 1.6GHz

● DDR4 SDRAM supports up to 2133MTps data rate

● Interfaces include Gigabit Ethernet, PCIe Gen2, and USB 2.0

● Peripheral interfaces include eMMC, SPI, I2C, UART, and GPIO

● Integrated acceleration for security

● Integrated 2D & 3D GPU (1x shader, OpenGL®ES 2.0)

● MIPI Display DSI & Camera CSI

● 1080p60 Encoder and Decoder

● IEEE1588 precision stamp protocol support

DDR4 SDRAM

The SDRAM resides in one LPDDR4 device soldered directly to the board. This

architecture supports DDR4 memory capacities from 1GByte to 4GBytes. The 32-bit

DDR4 interface operates at up to 1500MHz for supporting fast data transfer rates. The

factory default includes 1GByte of LPDDR4.

System Flash

The System Flash supports eMMC memory capacities from 4GBytes to 64GBytes. The

8-bit data bus interface supports double data transfer rates. The default boot device is

the eMMC Flash. The factory default is 8GBytes.

Mini-PCIe Sockets

Mini-PCIe is a small form factor PCI card that uses the same signal protocol, electrical

specifications, and configuration definitions as conventional PCI Express. The board

includes Gen 2 capable Mini-PCIe sockets with the following enhancements to the PCI

Express standard.

● The 3.3V power for the socket is increased from a maximum of 3.3W to 8W for

accommodating higher power radios. The 8W limit is due to the 0.5A limit of the

individual socket pins.

● The PCIe reset for the socket is unique and under software control.

● Certain sockets support both PCIe and USB 2.0 signaling

USB Support

● Slot J10 Supports PCIe, USB 2.0, SIM

● Slot J8 can support PCIe and USB 2.0.

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

9 of 32

Venice Single Board Computer Operating Manual

PCIe Socket Reset & WiFi Disable

The Mini-PCIe sockets support individual software programmable resets and shared

WiFi disable signals. The reset signal is controlled through the processor PCIe

interface and the WiFi disable signal is controlled through the Gateworks System

Controller.

Micro-SD and Nano SIM Expansion

A combined Micro-SD and Nano SIM socket extends the functionality of the SBC.

The Micro-SD extends the local Flash storage capacity. The socket accepts small 11mm

by 15mm removable cards with storage capacities from 64Mbytes to 32Gbytes. The

4-bit data interface supports transfer rates up to 25Mbytes per second. This readily

available storage device is commonly used in cellular phones, GPS devices, portable

media players, and digital cameras.

The Micro-SD socket communicates with the processor using the SD[2] Secure Digital

interface and supports a card detect signal SD2_CD signal. Software drivers are

available for SD format cards.

The Nano SIM (4FF) socket accepts 12.3 mm by 8.8 mm cellular SIM cards. The SIM

signals are routed to a single Mini-PCIe socket, J10, for cellular modem usage.

GbE Ethernet

The SBC supports Gigabit Ethernet. The Ethernet ports operate in a 10BASE-T,

100BASE-TX or 1000BASE-T configuration and include auto MDI/MDIX for

automatically switching data receive and data transmit pairs. Additional features include

full-duplex operation as well as support for auto- negotiation. The data interfaces

include direct-touch ESD protection that exceeds IEC61000-4-2-ESD. The Ethernet

MAC addresses are programmed into the Gateworks System Controller Configuration

EEPROM during automated factory testing.

The IEEE802.3 compliant Ethernet MAC Media Access Controllers are located in the

processor. The Gigabit Ethernet Port MAC communicates to an external PHY physical

layer device through an RGMII interface. The external PHY is reset under software

control using a processor digital I/O signal.

The RJ45 connector for the Gigabit Ethernet Port includes integrated status lights. The

green light is on for link and blinking for activity. The yellow status light indicates speed.

The yellow light is off for both 10Mbps and 100Mbps, and on for 1000Mbps.

The SBC input power can be provided through the Gigabit Ethernet Port jack in a

Passive Power over Ethernet or 802.3at active Power over Ethernet architecture. This is

discussed in greater detail at the end of this section. The RJ45 connectors can be

replaced with an 8-pin dual-row 2mm header such as the JST B08B-PUDSS as an

ordering option.

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

10 of 32

Venice Single Board Computer Operating Manual

USB Ports

The processor includes two USB ports. The default processor supports USB 2.0. Future

SOMs may support USB 3.0. One port is connected to a OTG Type-B connector and

the other to a USB Hub, which is routed to Mini-PCIe sockets. Mini-PCIe sockets also

receive USB signalling. The USB ports support low-speed 1.5Mbps transfers, full-speed

12Mbps transfers, and high- speed 480Mbps transfers. The SBC is configured as a

Downstream Facing Port capable of sourcing 5V at 1.5A. The output power is enabled

through a CPU GPIO signal (GPIO[1]:DIO[12]) and the current fault monitoring is

monitored through another CPU GPIO signal (GPIO[1]:DIO[13]).

Peripheral Expansion

The SBC includes a peripheral expansion connector that supports digital I/O, serial I/O,

analog input, system reset, I2C and power.

Digital I/O

There are several general purpose digital I/O signals supported with CPU GPIO

digital I/O signals. The 3.3V digital I/O signals support 10mA drive current, 10mA

sink current, and signal conditioning in the form of a series 332 ohm resistor.

Serial I/O

The serial interface is available through several UARTs as defined in the

connector section in this document. Several UARTs are routed through a

programmable transceiver supporting RS232 and RS485 (half duplex and full

duplex). Another UART is routed to the optional GPS and a header for TTL

levels.

Analog Input

There are two analog inputs that are available through the Gateworks System

Controller. The 0 to 5V analog input is divided by two.

System Reset

The system reset signal is connected to the Gateworks System Controller

pushbutton input and supports all of the associated features. This includes

generating an interrupt, system reset, and powering the SBC on and off.

I2C Two Wire Interface

An I2C interface is offered.The 3.3V two wire interface supports standard

SCL/SDA protocols up to 400KHz with 7-bit and 10-bit addressing in both master

and slave operation. The two wire interface is supported with the processor port

and includes pull up resistors on both signals.

More information can be found at the following links:

●http://trac.gateworks.com/wiki/I2C

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

11 of 32

Venice Single Board Computer Operating Manual

SPI Serial Peripheral Interface

An SPI serial peripheral interface is available through a connector. The interface

includes 121 ohm series resistors for short circuit protection, operates up to

50MHz, and supports both interrupt and polled transactions.

More information can be found at the following links:

●http://trac.gateworks.com/wiki/SPI

Gateworks System Controller

The GSC Gateworks System Controller is a custom battery-backed micro-controller

designed by Gateworks to implement many of the embedded features found on the

board. This includes features such as real time clock with battery backup, system

temperature and voltage monitor, configuration EEPROM, and digital I/O. Software

information can be found at http://trac.gateworks.com/wiki/gsc

Real Time Clock with Battery Backup

The real time clock is provided by the Gateworks System Controller. The

Gateworks System Controller emulates an industry standard Dallas

Semiconductor DS1672 to support the real time clock. This includes a 32-bit

counter that counts seconds for determining time of day, week, month, and year.

The I2C address for the real time clock is 0x68h. The real time clock is battery

backed to retain time information when power is removed from the board. The

battery is a 12.5mm BR1225 coin cell installed in a surface mount socket.

System Temperature and Voltage Monitor

The system temperature and voltage monitor is provided by the Gateworks

System Controller. The Gateworks System Controller does not emulate a specific

device to support the temperature and voltage monitoring functions. The I2C

address for the temperature and voltage monitor is 0x29h. The temperature and

voltage parameters monitored by the Gateworks System Controller are listed in

the table below. The GSC mapping includes the value referenced by the software

driver written for the Gateworks System Controller. Software information is

available on the following Gateworks Wiki page:

http://trac.gateworks.com/wiki/gsc

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

12 of 32

Venice Single Board Computer Operating Manual

Analog

Input

Input Divider

R1/(R1+R2)

Description

0

10K/20K

Board Level Operating Temperature

1

22.1K/23.1K

Board Level Input Operating Voltage

2

10K/32.1K

ADC1

3

10K/20K

ADC2

4

None

1.1V MX8M Mini DRAM

6

None

1.2V Core Mipi

7

None

1.0V RGMII Phy

8

10K/20K

2.5V RGMII Phy

9

10K/20K

3.3V Primary Supply

12

None

0.95V CPU

13

None

1.8V LPDDR4

14

None

Reserved

15

None

Reserved

Gateworks System Controller Monitored Temperature and Voltages

Configuration EEPROM

The configuration EEPROM is provided by the Gateworks System Controller. The

Gateworks System Controller emulates an Atmel 24C04. The EEPROM is

divided into a general purpose section available to the application and a section

reserved by Gateworks for storing various system configuration parameters. The

I2C address for the configuration EEPROM is 0x50h.

Fan Speed Control

The fan speed function controls the rotational speed of a fan though the J8

connector. Fan speed control increases fan service life and decreases system

acoustic airflow noise. The Gateworks System Controller supports up to six

temperature set points. The fan speed is set to off until operating temperature

reaches the first set point. When the operating temperature reaches the first set

point, the fan speed is set to 50%. The fan speed then increases 10% as the

operating temperature climbs through each additional set point. The fan

connector also supports a tachometer feedback signal through the Gateworks

System Controller to ensure the rotational integrity of the fan.

Additional System Level Functions

The Gateworks System Controller also supports encryption key and software

programmable hardware shut-down and wake-up for the highest possible power

conservation.

Battery Backup

The Gateworks System Controller must be powered at all times if support

features such as continuous real time clock, and programmable hardware sleep

and wake-up are required. This power is supplied by a coin cell battery when the

SBC is powered down. The Gateworks System Controller seamlessly switches

from the coin cell battery to input power when the SBC is powered on to extend

coin cell battery life. The coin cell socket includes both a reverse charge

protection resistor and a current blocking diode to provide two levels of protection

required for some agency approvals.

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

13 of 32

Venice Single Board Computer Operating Manual

3-Axis Accelerometer/Magnetometer

The 3-Axis sensor device combines a 8-bit linear accelerometer. The device includes a

+/-2g, +/-4g, +/-8g and +/-16g dynamically selectable acceleration full scale range.

Acceleration event functions include free fall and motion detection. The accelerometer

communicates to the CPU on the I2C[2] bus at address 0x19. The accelerometer is a

STMicroelectronics LIS2DE12TR.

More information can be found at the following links:

●https://www.st.com/en/mems-and-sensors/lis2de12.html

●http://trac.gateworks.com/wiki/accelerometer

Optional GPS Receiver

The optional u-blox ZOE-M8 GPS Receiver is a 72 channel Global Navigation Satellite

System (GNSS) device for delivering position, velocity, and time information. The GPS

Receiver includes a dual frequency RF front end for concurrent reception of up to three

GNSS systems. This includes GPS/ZQSS, GLONASS, Galileo, and BeiDou.

The device is typically configured for 9600 NMEA protocol depending on the GPS

firmware revision. Communication to the CPU is through the UART1 serial port

interface. A pulse-per-second signal is also supported through the CPU

GPIO[1]:DIO[15] digital I/O signal. The PPS signal can be factory optionally routed to a

Mini-PCIe socket. A MMCX or a U.FL connector connects to an externally mounted

active antenna. The antenna includes a series current limit resistor to protect against a

shorted antenna.

More information can be found at the following links:

●https://www.u-blox.com/en/product/zoe-m8-series

●http://trac.gateworks.com/wiki/gps

Key Parameter

Specification

PPS Time Accuracy RMS

30nS

PPS Time Accuracy 99%

60nS

Dynamic Operational Limit

<4G

Altitude Operation Limit

50,000m

Velocity Operational Limit

500m/s

Velocity Accuracy (50% @ 30ms)

0.05m/s

Heading Accuracy (50% @ 30ms)

0.3 degrees

GPS Receiver Key Parameters

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

14 of 32

Venice Single Board Computer Operating Manual

GNSS Parameter

GPS &

Glonass

GPS

Glonass

BeiDou

Galileo

Horizontal Position Accuracy

2.5m

2.5m

4m

3m

TBD

Navigation Update Rate

ROM

Flash

10Hz

5Hz

18Hz

10Hz

18Hz

10Hz

18Hz

10Hz

18Hz

10Hz

First Fix Time

Cold Start

Hot Start

Aided Start

26s

1s

2s

29s

1s

2s

30s

1s

2s

34s

1s

3s

45s

1s

7s

Tracking Sensitivity

-167dBm

-166dBm

-166dBm

-160dBm

-159dBm

Re-acquisition Sensitivity

-160dBm

-156dBm

-156dBm

-157dBm

-153dBm

Cold Start Sensitivity

-148dBm

-145dBm

-145dBm

-143dBm

-138dBm

Hot Start Sensitivity

-157dBm

-157dBm

-156dBm

-155dBm

-151dBm

GPS Receiver GNSS Parameters

JTAG Programming Port

The primary purpose for the JTAG Port is for automated factory testing and to facilitate

downloading the application program into Flash memory. This feature requires the

GW16099 USB JTAG Programmer (sold as a GW11033 kit). The JTAG programming

port also includes a CPU UART interface in a logic-level configuration. This serial port

facilitates an operator console though the USB JTAG Programmer. Refer to Section 3

for USB JTAG Programmer instructions.

MIPI DSI & MIPI CSI

The processor supports MIPI DSI (Display Serial Interface) and CSI (Camera Serial

Interface) for display and cameras respectively. More information can be found on the

Venice MIPI Wiki Page: http://trac.gateworks.com/wiki/venice/mipi

Status LEDs

The board includes a surface mount LED and a bi-color LED located towards the front

edge of the board.

Label

Function

3.3V

Primary voltage rail is active

PRG

Programmable using i.MX8M GPIO[5]:DIO[4] and GPIO[5]:DIO[5]and

digital I/O signal

Surface Mount Status LED Functionality

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

15 of 32

Venice Single Board Computer Operating Manual

Power Architecture

DC input power is supplied through the barrel jack, one Ethernet connector using

802.3at Power over Ethernet, or the other Ethernet Port connector using Passive Power

over Ethernet.

Barrel Jack Power

The barrel jack at location J16 has a 2.5mm inner pin diameter. The connector is

polarized with the center pin being positive. The input voltage range is 8-60V.

The mating connector is G/S SR2048A, available from Jameco as part number

195038.

802.3at Active Power over Ethernet

One Gigabit Ethernet Port supports 802.3at Power over Ethernet by acting as a

Powered Device (PD) with power being supplied by Power Sourcing Equipment

(PSE) such as an 802.3at compliant Ethernet switch. This includes providing

detection signature, classification signature, and current inrush limiting after

being instructed to power on. The input voltage range is 36-57V as defined by

the PoE specification. The power and ground connections include full wave

bridge rectification so that they can be connected on any two data pairs.

More PoE information is available on the Gateworks wiki here:

http://trac.gateworks.com/wiki/poe

Passive Power over Ethernet

One RJ45 Ethernet jack supports Passive Power over Ethernet. This

configuration is most useful for powering the SBC through an Ethernet jack

without an 802.3at compliant PSE switch. The input voltage range is 10-60V.

The positive input voltage and ground must be applied on specific data pairs

unlike the 802.3at architecture. The positive input must be applied on the pin 1-2

and pin 4-5 data pairs and ground must be applied on the pin 3-6 and pin 7-8

data pairs.

The data pairs for Passive Power over Ethernet have a 0.8A current limit. It may

be necessary to increase the input operating voltage to deliver the power needed

for the Mini-PCIe radios and USB charging ports. As an example, assume the

application includes a high power radio card that requires a total of 8W and a

USB device that requires a total of 7W. The required power is 15W for the

peripherals plus 4W for the SBC. The total power requirement is approximately

21W assuming 90% efficiency for the primary power supply.

More PoE information is available on the Gateworks wiki here:

http://trac.gateworks.com/wiki/poe

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

16 of 32

Venice Single Board Computer Operating Manual

Switching DC/DC Regulators

All power supply voltage rails are generated with high efficiency DC to DC

switching regulators. The SBC is classified as a SELF Safety Extra Low Voltage

Device since the maximum input voltage is below the 60VDC SELV limit as

defined by IEC 60950-1 and other standards.

Feature

Benefit

High efficiencies (up to 95%)

Reduces heat generated in enclosure

High power output (up to

30W)

Supports high power Mini-PCIe cards

Thermal shutdown

Protects against overheating

Output current limit

Protects against short circuits

Controlled startup

Reduces component stress and power surges

Common mode input filter

Reduces emissions for agency certification

Switching DC/ DC Regulator Features

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

17 of 32

Venice Single Board Computer Operating Manual

2. CONNECTORS

The board interface connector pin assignments and signal descriptions are included in

the following sections. The connectors are listed in the table below.

Connector

Populated

Function

J1

Yes

Micro SD / Nano SIM Socket

J2

Yes

Coin Cell Battery Socket

J3

Yes

Serial Peripheral Interface (SPI)

J4

Yes

MIPI CSI and DSI Header

J5

Yes

Peripheral Expansion (GPIO, UART, I2C, ADC)

J6

Yes

SOM Connector

J7

No

Test Header

J8

Yes

Mini-PCIe Socket with PCIe and USB 2.0

J9

Yes

SOM Connector

J10

Yes

Mini-PCIe Socket with PCIe and USB 2.0 and SIM

J11

Yes

RS232/RS485 Serial Ports

J12

Yes

5V Fan Speed Control

J13

Yes

Tamper Switch

J14

No

Optional GPS Receiver MMCX Antenna

J15

No

Optional Power Input Header

J16

Yes

Input Power Barrel Jack

J17

Yes

Gigabit Ethernet Ports and Active/Passive PoE Input

Power

J18

No

Optional USB Host Type A Socket

J19

Yes

USB OTG Micro B Socket

J20

No

Optional Push Button Switch Header

Connector Summary

Micro-SD Flash and Cellular Nano SIM Expansion Socket (J1)

Flash expansion is possible by installing an industry standard 11mm by 15mm Flash

card into the socket. The Micro-SD Flash card cannot be installed or removed with

power applied to the SBC. The Micro-SD and Nano SIM sockets are combined. The

command signal is routed to the processor.by default. The Nano SIM socket is routed to

Mini-PCIe socket J10.

Battery Coin Cell Socket (J2)

The 12.5mm backup battery socket allows for easy replacement of the battery. A

standard 12.5mm, BR1225, 3V, 50mAH Lithium coin cell should be used when replacing

the battery. Replacement batteries can be ordered from Digi-Key with part number

P183-ND.

Serial Peripheral Interface (SPI) Expansion (J3)

An SPI port is available through a 6-pin header in a 1x6 configuration with 2mm

spacing. The mating connector is a JST PAP-06V-S, available from Digi-Key as

part number 455-1490-ND. The mating connector pins are JST SPHD-002T-P05,

available from Digi-Key as part number 455-1313-1-ND.

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

18 of 32

Venice Single Board Computer Operating Manual

Pin

Signal

1

SPI_MOSI

2

SPI_MISO

3

SPI_SCLK

4

SPI_SS0

5

3.3VDC

6

Ground

SPI Interface Connector

MIPI CSI and DSI Header (J4)

The Mobile Industry Processor Interface (MIPI) Camera Sensor Interface (CSI) and

Display Serial Interface (DSI) are available together in a 2x25 configuration with .4mm

pin spacing. The mating connector is a Hirose DF40C-50DP-0.4V(51), available from

Digi-Key. More information can be found on the Venice MIPI Wiki Page:

http://trac.gateworks.com/wiki/venice/mipi

Pin

Signal

Pin

Signal

1

Ground

2

Ground

3

CSI 0-

4

DSI 0-

5

CSI 0+

6

DSI 0+

7

Ground

8

Ground

9

CSI 1-

10

DSI 1-

11

CSI 1+

12

DSI 1+

13

Ground

14

Ground

15

CSI CLK-

16

DSI CK-

17

CSI CLK+

18

DSI CK+

19

Ground

20

Ground

21

CSI 2-

22

DSI 2-

23

CSI 2+

24

DSI 2+

25

Ground

26

Ground

27

CSI 3-

28

DSI 3-

29

CSI 3+

30

DSI 3+

31

Ground

32

Ground

33

Audio3 CLK

34

I2C CLK

35

Audio3 TX

36

I2C DATA

37

Audio3 TXFS

38

Ground

39

Audio3 RX

40

VDD 1.8V

41

Audio3 TXC

42

VDD 1.8V

43

MIPI GPIO1

44

VDD 3.3V

45

MIPI GPIO2

46

VDD 3.3V

47

MIPI GPIO3

48

VDD 5V

49

MIPI GPIO4

50

VDD 5V

MIPI CSI and DSI Header

Peripheral Expansion (J5)

The peripheral expansion connector includes digital I/O, optional serial I/O, analog

input, system reset, optional I2C, and power. The CPU connections support a 3.3V

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

19 of 32

Venice Single Board Computer Operating Manual

interface. The connector is an 10-pin header in a 1x10 configuration with 2mm pin

spacing. The mating connector is a JST PAP-10V-S, available from Digi- Key as part

number 455-1494-ND. The mating connector pins are purchased separately.

Pin

Signal

1

i.MX8M GPIO[1]:DIO[7]

2

i.MX8M GPIO[1]:DIO[9]

3

UART[3] RXD (logic level)

4

UART[3] TXD (logic level)

5

Serial Clock

i.MX8M I2C3 SCL

6

Serial Data

i.MX8M I2C3 SDA

7

GSC ADC1

8

GSC ADC2

9

3.3VDC

10

Ground

Peripheral I/O Connector

SOM Header (J6 & J9)

The System on Module (SOM) with the CPU, DRAM and Flash connects to the

baseboard. There are roughly 180 pins between the 2 sockets. The system is not

designed in a way that the SOM would be removed and the user would interface with

connectors directly. If more information is required, please contact Gateworks support.

Test Header (J7)

This is for internal Gateworks use. Please contact Gateworks technical support with any

further questions.

GATEWORKS.COM 3026 S. Higuera St San Luis Obispo, CA 93401 P:(805)781-2000

20 of 32

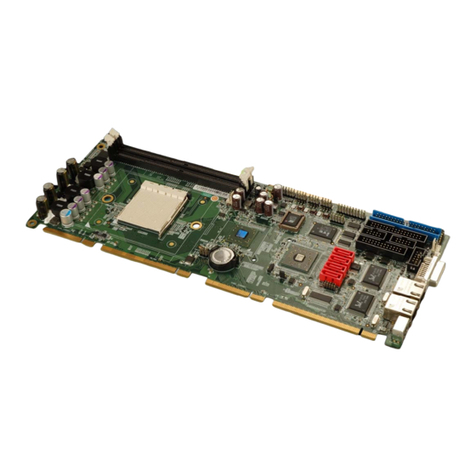

This manual suits for next models

4

Table of contents

Other GATEWORKS Single Board Computer manuals