342-86400-447PS

Issue 1

March 1994

Page 9

Copyright

GE Power Management 2001

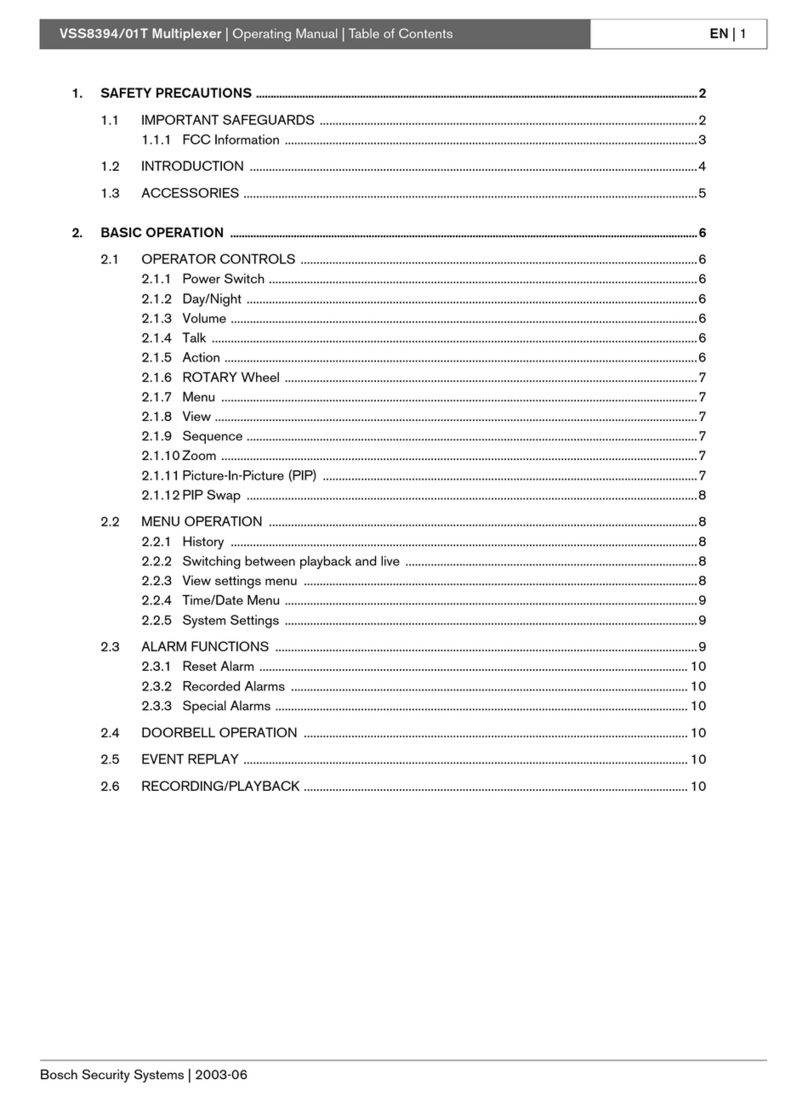

4. UNIT DESCRIPTION

The 86447 LS DATA unit can be configured with up to four data ports however,

the following description is for circuit one only. Signal paths for circuits two,

three, and four will be identical as circuit one except for designations, locations,

etc.

All user connections are made to the 86447-90 Interconnect Paddle Board. Four

terminal blocks provide transmit data, receive data, signal ground, transmit

control and receive control interfaces for all four circuits. All pinout arrangements

are provided in the Installation Section of the manual.

A simplified Block Diagram has been included at the end of this section and can

be used for reference for the following signal paths analysis, however the user

should refer to schematics EAS-86447-M1 for complete circuit descriptions.

Transmit Signal Path

The XMT DATA IN bits are received on Paddle Board TB1(1) and sent to the

back connector J1(C1) of the main assembly board 087-86447-01. Plug P4(1)

routes the signal to the RS-232 Interface Assembly Board 087-86447-02 via

J4(1).

U4 on the Interface Assembly Board provides the electrical interface to the

Paddle Board and the necessary level translation and protection from the various

interfaces for the Programmable Logic Gate Array (U2). J2(15) passes the

signal back to the main assembly board on P2(15) to the capacitor chip array

CN3(12) which provides EMI filtering and suppression for U2.

U2(5) accepts the signal where it is processed and routed through various gate

arrays in the chip.

The signal is outputted on U2(78) to the output driver U8. The JVT Interface

J1(C14, A14) consists of a balanced 50 ohm RS-422 signal pair designed for

multi-point transmission.

The unit receives its clock source from the JVT Bus J1(C15, A15) through the

input driver U6. The JVT serial bus operates at 2.592 MHz.