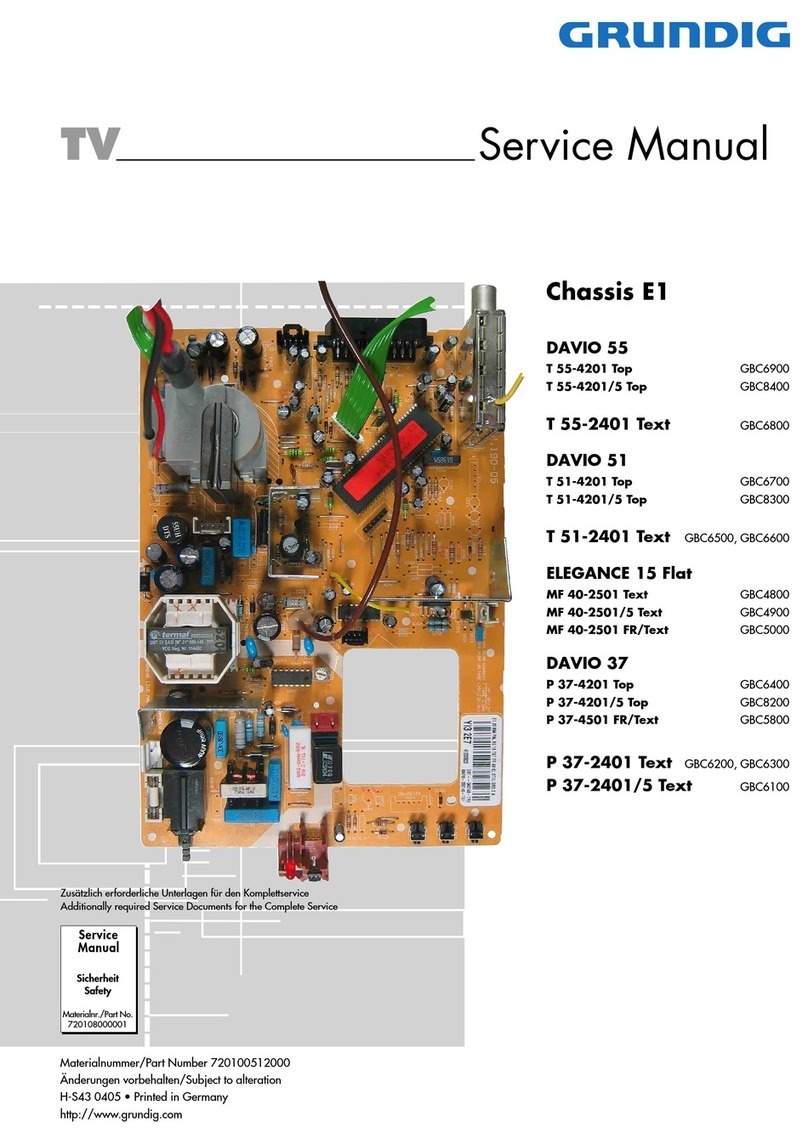

Circuit Description ST 03

2 - 2 GRUNDIG Service

whichisintegratedontotheIC800.Thesyncseparationandtimebase

circuits are also integrated on to this chip. Incoming video is stripped

of its line and field sync pulses. The horizontal and vertical syncs are

then derived from the composite sync waveform.

6. Time Base Generator

Thelinesyncisfedtothelinetimebasegeneratorcircuit.Thelinetime

baseis derivedfromthe masterclockoscillator anddividercircuit. The

linepulses fromthedivider arefedintobothPLLcircuitsalong withthe

sync and flyback pulses. These combine together to produce the line

driveforthelineoutputcircuit.TwoPLLtimeconstantsareusedtogive

good lock for both fixed, gen-locked syncs, such as from terrestrial

transmission and from weak or variable sync such as VCR.

All controls for the line time base generator are integrated and are

accessedviatheI2CbusundermicrocontrolfromIC500.Theseareset

up in the factory by a test software.

6.1 Vertical Time Base

The vertical time base is again generated on chip by the use of the

master clock in conjunction with the separated field sync. The divider

circuitcount is controlled by thesyncpulse.The counter produces the

pulsestogeneratethe vertical ramp which is in turn fed toa bufferand

then fed out to the field output circuit.

Inthe event ofnovalidsync being presentthenadirect injection mode

isusedtocontinuethefunctionoftherampgenerator.Thisdirectmode

then enables vertical scan to be maintained in the event of no signal

being present.

7. RGB Drivers

The RGB video signals are fed out on IC800-(17), -(18), -(19). These

signalsarethenbufferedbytheemitterfollowercircuitsTR801,TR802

and TR803 before being fed to the tube base panel. External RGB

signalsare also abletobefed intothisICon pins22,23and 24. These

pinsare normally fed withRGBlevelsof 700mVpp signals fornominal

display. The choice of display is determined by the switch pin on

IC800-(21). This is controlled by the output of the teletext chip blank

signal or the blanking signal from the microcontroller for on screen

graphics display or the PERITEL pin 8.

7.1 Auto Grey Scale Tracking

The system also incorporates an automatic grey scale tracking sys-

tem. This removes the need for manual adjustments to set up back-

ground luma levels in high-light and low-light areas on CRTs.

Forcorrecttrackingtheautogreyscaleworksontheprincipaloftaking

measurementsof the dark current during thefieldblankingperiodand

also inserting a peak white signal in that period and setting those

thresholdstocontroltheoutputstagesofthechip.Thisensuresthatthe

tube characteristics are constantly being matched by the video output

sothatgreyscaleandpicturecolourintegrityisconstantlymaintained.

7.2 Beam Limiter

The RGB output gains are also affected by the beam limiter circuit on

IC500. This is to prevent the tube from being damaged or its life

expectancy being shortened by excessive beam current.

Thesensingof the beam current is performedatthebottomendof the

DST secondary supplying the EHT focus and G2 voltages to the tube.

The reference point is pin 7 on the DST, this current is sensed as a

changeinvoltagedevelopedacrossresistorsandfedtothebeamlimit

sense IC800-(9). This voltage is measured against a reference which

represents maximum beam current. When the sensing level exceeds

the reference then the gain on RGB output amps is reduced, thereby

reducingthebeamcurrent.Saturationcontrol,brightnessandcontrast

are adjusted via the remote control but the nominal levels are preset

inthefactorybytheI2Cbususingthemicrocontrollerandtestsoftware.

8. System Microcontroller (IC500)

TheST6365 is adedicatedmicrocontrollerfor TVcontrolapplications.

Ithassuchfeaturesasdedicatedvoltagesynthesistuningcontrol,AFC

control and on-screen graphics display generator. Also it has a

dedicated infrared remote control serial data input. This microcontrol-

lerhasadedicatedI2CportforcommunicationtoothercontrollableICs.

The controller clock frequency is 8MHz and this clock speed is

achieved by connecting an 8MHz ceramic resonator across the

oscillator pins 31 and 32 with two 100pF capacitors, C507 and C508,

to ground from each pin. The timing for all functions performed by the

microcontroller including I2C bus are taken from this clock.

8.1 Voltage Synthesis

Theon-chipvoltagesynthesistuningperipheralhasbeenintegratedto

allow the generation of a tuning reference voltage. The peripheral is

composed of a 14 bit register that represents the tuning voltage at

pin 1. This voltage is generated using pulse width modulation and bit

rate multiplier techniques.

The 14 bit counter gives 16384 steps which allow a resolution of

approximately2mVoveratuningvoltagerangeof32V.Coarsetuning

isachievedbyPWMofthe7mostsignificantbitsofthe counter, whilst

fine tuning is achieved by BRM (Bit Rate Multiplication) of the 7 least

significant bits of the counter.

The resultant digital pulse train is fed into the base of TR410. This

invertsthepulsetrainwhichisthenfedintothe3stageintegratorwhich

integrates the pulse train into a DC voltage.

8.2 AFC Control

The output of the voltage synthesizer can be changed either by the

remote control or the local keyboard. The tuner oscillator is kept on

frequency by the application of AFC. The AFC acts on the voltage

synthesizervia a feedbackpath.TheAFC is generated byIC400.This

voltage is fed back to the AFC pin 9 on the controller. As the tuner

oscillator drifts either up or down so the signal applied to IC400

deviates from the optimum. As a result an error voltage appears on

IC400-(2). This voltage can be either positive or negative with respect

to the optimum voltage. This error voltage is fed to pin 9 of the

microcontroller. This voltage is then digitized. If the digital value is

optimumthennochangeismadetothesynthesizeddigits.Ifthedigital

value is either side of optimum, then the resultant AFC value is either

added to or subtracted from the synthesizer value.

8.3 Analog Controls

Pins2and5onthemicrocontrollerarePWMD-Aconverters.However,

these are only 6 bit resolution which is perfectly acceptable for the

analog functions they perform.

TheD-Aonpin2isusedastheelectronicvolumecontrolforthesound.

TheD-Aonpin3isusedforthemulti-levelvoltagecontrolforaudioand

video switching of IC400 and IC450. The D-A on pin 4 is used to

produce the threshold level for the AGC to the tuner. The final D-A on

pin5isasyetuncommitted.Themicrocontrollerhas3I/Oportsaswell

as the dedicated peripheral pins, some of the I/O ports also have

dedicated functions and are listed as their dedicated function, i.e. the

AFC on pin 9 is bit 3 of port B.

8.4 Key Pad Interface

Bits 0-2 and bits 4-5 of port B provide the matrix for the crosswire

keypad.

8.5 Sync Detector/Mute Control

Bit 6 of port B is a sense pin which mutes the sound when text is

displayedandincomingsignalis lost. Normally the microcontroller will

mute the sound when the aerial is removed or tuning is off station

because it detects no line lock coincidence.

However, in out-of-hours sync mode, the text chip set detects lack of

sync coincidence and mutes the sound. Bit 0 on port A senses the

status of pin 8 on the peri connector for switching video and sound to

incoming signals on the peri connector.

8.6 Peritel Monitor/OSG Control

Bit 1 on port A monitors the blanking signal on pin 16 of the peri

connector and also the blanking signal from text and OSD sources.

Bit 2ofportAactsasthecontrollinefortheswitchthatactsonSAW450

asdescribedinsection2.Bit3isusuallylinkedtoground, however for

System PAL BG/SECAM L/L’ this link is omitted.

8.7 Band Switching and LED Driver

Bits4to6ofportAarethebandswitchingoutputswhichdrivetheband

switches.Bit7 of port A is connected tothe LEDD500.Pins22and25

are OSG display pins whilst pins 26 and 27 are the sync input pins.

Pin33 is the hardwarepower-onreset. Pin 34 istheSECAM L/L SAW

selector switch. Pin 35 is IR input line. Pin 36 is BG/DK system select.

8.8 Standby Control/ Sound Mute

Pin37isavailableasastandbylineforexternaluse.Innormalstandby,

thecontrollershutsdownallcircuitsthatprovidedrivetooutputstages,

thereby placing the system in quiescent current consumption mode.

Pin39isthesoundmuteoutputwhichdrivesthesoundmutetransistor

TR5 and TR7. Pins 40 and 41 are the dedicated I2C bus.