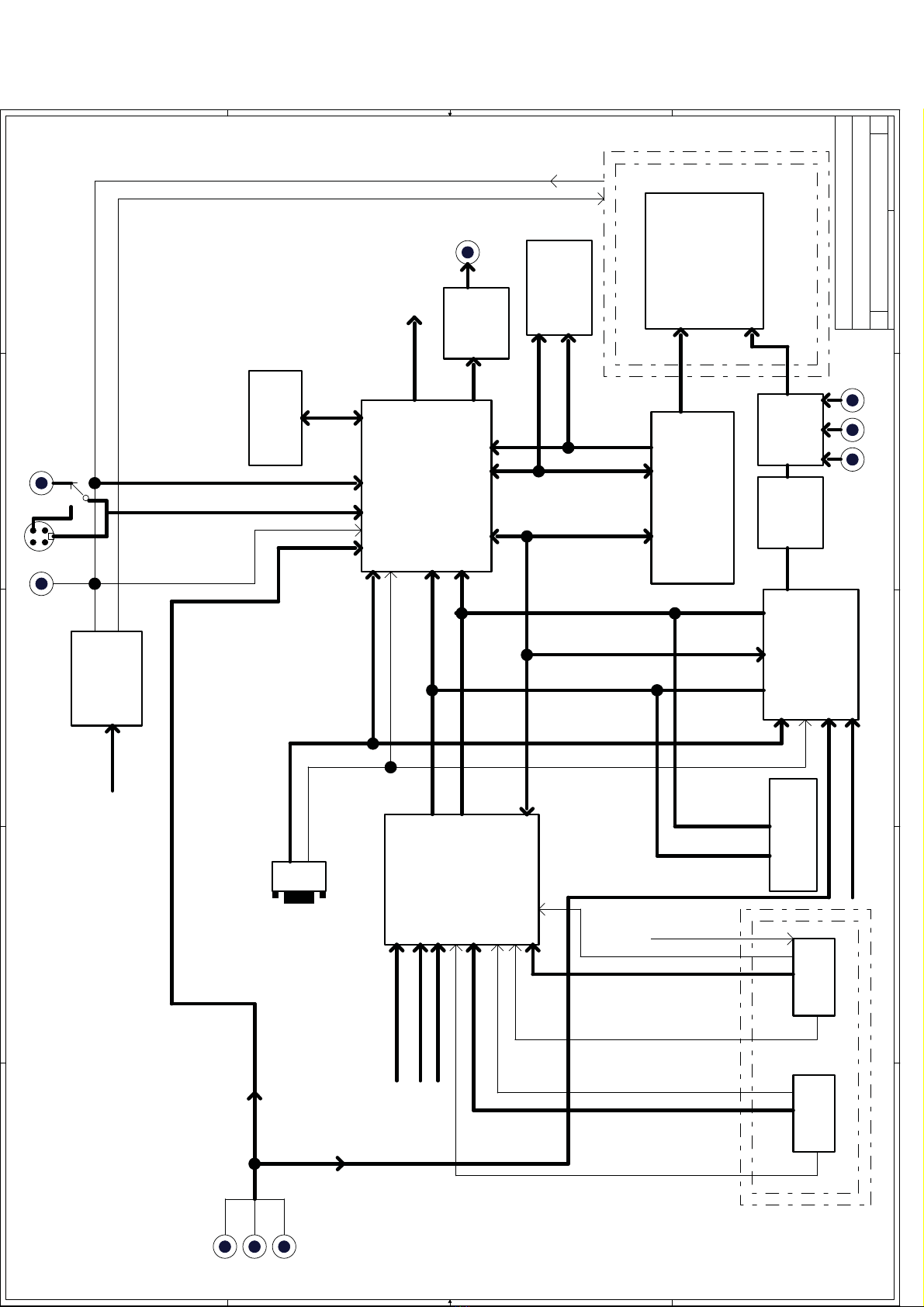

4. Key IC Description& Trouble Shooting Guide

A: MAIN CHIP SUMMARY

U11 M30620: 16-BIT CMOS SINGLE-CHIP MICROCOMPUTER

The single-chip microcomputer operate using sophisticated instructions featuring a high level of instruction

efficiency. With 1M bytes of address space, they are capable of executing instructions at high speed. In addition,

this microcomputer contains a multiplier and DMAC which combined with fast instruction processing capability.

U1 SVP-EX52: VIDEO DECODER+DE-INTERLACE+SCALE

The SVP_EX-52 video processor is a highly integrated system on a chip device, targeting the converging

HDTV-ready and PC-ready and LCD TV, PDP TV, and DLP TV applications where high precision processing of

video and data are the requirements. SVP_EX-52 contains dual-purposed triple 10-bit high-precision and

high-speed video ADCs for both PC and video inputs, a high performance 5th generation multi-format 3D digital

comb video decoder that supports NTSC, PAL and SECAM, an HDTV sync separator, motion adaptive

de-interlacing engine, and the video format conversion engine,

U4 MST3788: 8-bit Analog and HDCP Interface for Advanced Digital Displays

The MST3788 integrates both analog interfaces and HDCP compliant receivers for enabling advanced

digital display devices such as digital TVs, plasma displays, LCD TVs and projectors to receive and display.

Compliant with the HDCP 1.0 specification, the MST3788 enables consumer electronic devices to receive

uncompressed, high quality, digital video HD content over a single, low-cost DVI cable.

UA11 MSP3450G: AUDIO DECODER

The MSP 34x0G family of single-chip Multistandard Sound Processors covers the sound processing of all

analog TV-Standards worldwide,

U3 K4D263238F: 128M DDR SDRAM

UA4 TPA3004: The TPA3004D2 is a 12-W (per channel) efficient,Class-D audio amplifier

fordrivingbridged-tied stereospeakers. The TPA3004D2 can drive stereo speakers as low as

4. The high efficiency of the TPA3004

eliminates the need for external heatsinks when playingmusic.Stereo speaker volume is

controlled with a dc voltage applied to the volume control terminal offering a rangeof gain

from ¨C40 dB to 36 dB. Line outputs, for driving external headphone amplifier inputs, are also

dc voltage controlled with a range of gain from ¨C56 dB to 20 dB. An integrated 5-V regulated

supply is provided for powering an external headphone amplifier.

UA5 74HC4052 : The 74HC4052 is high-speed Si-gate CMOS devices and are pin

compatible with the HEF4052B. They are specified in compliance with JEDEC standard no.

7A. The 74HC4052 is dual 4-channel analog multiplexers or demultiplexers with common

select logic. Each multiplexer has four independentinputs/outputs (pins nY0 to nY3) and a

common input/output (pin nZ). The common channel select logics include two digital select

inputs (pins S0 and S1) and an active LOW enable input (pin E). When pin E = LOW, oneof

the four switches is selected (low-impedance ON-state)with pins S0 and S1. When pin E =

HIGH, all switches arein the high-impedance OFF-state, independent of pins S0 and S1.