Hartmann Electronic GmbH Backplanes

Motorstraße 43 Aufbausysteme (MPS)

Tel.: +49 711 1 39 89-0 Layoutservice

Fax: +49 711 8 66 11 91

www.hartmann-electronic.com

Geschäftsführer: Registergericht Stgt. HRB 7630 Deutsche Bank AG, Singen

Werner Fritz USt.-Id.-Nr. DE 147816208 BLZ 692 700 38 - Kto.-Nr. 050 1403 00

Dr. Günter Zahnenbenz Steuer-Nr. 9908300985 Swift-Code DEUTDE6F692

10

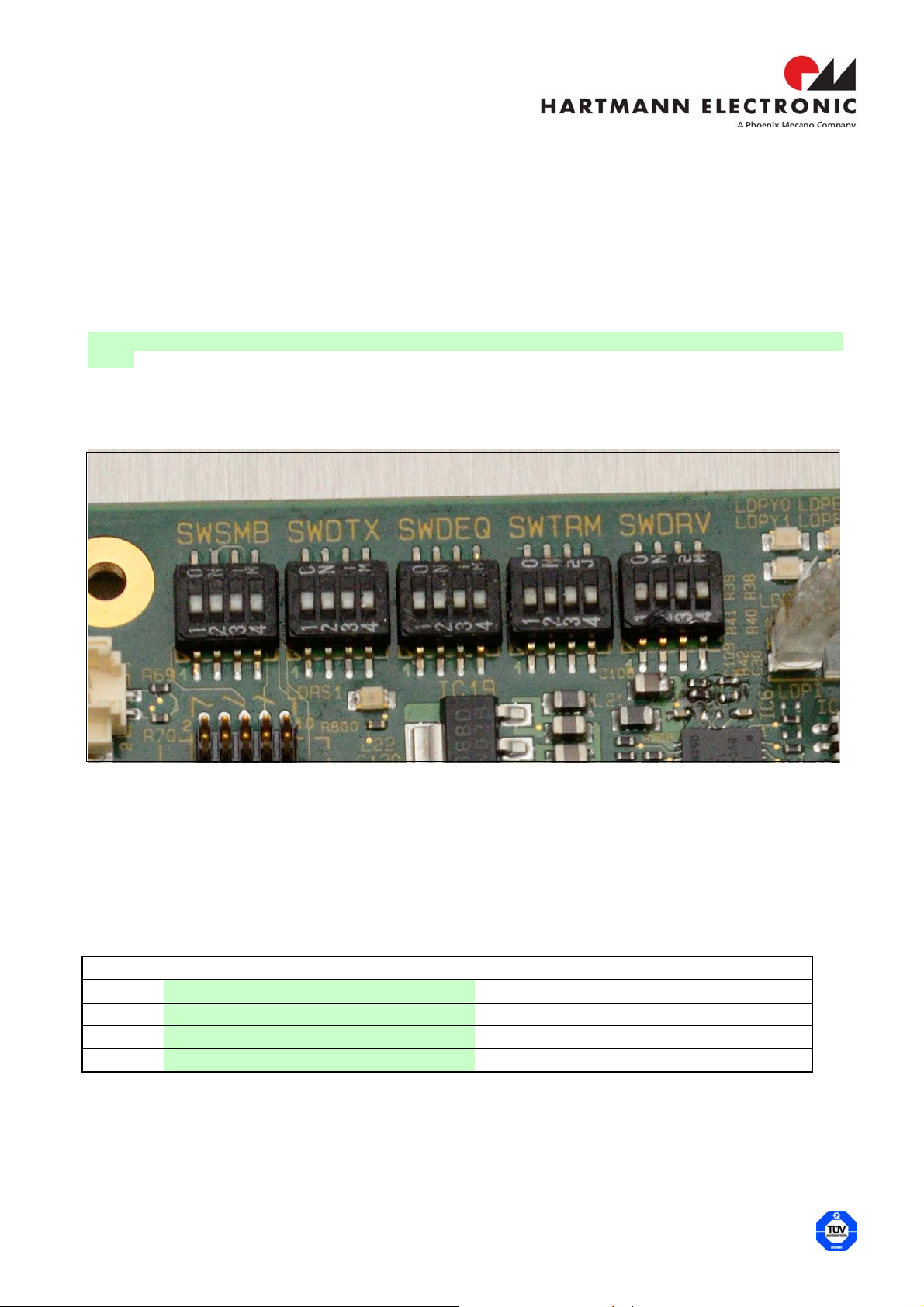

SWDRV SWDTX (Signal integrity optimization)

“LODRV”, “HIDRV”, “DTX[0:3]”

In order to meet the different application needs, the driving current and equalization of each transmitting channels

can be adjusted using Dip Switches .The driver current of each channel is set to 20mA in default mode. To

change the current value, the user can strap

the pins either for nominal value (“HIDRV”, “LODRV”) or actual value (“DTX [3:0]”), which is a scaled multiple of

Inom. The following tables illustrate the possible transmitted current values the switch provides.

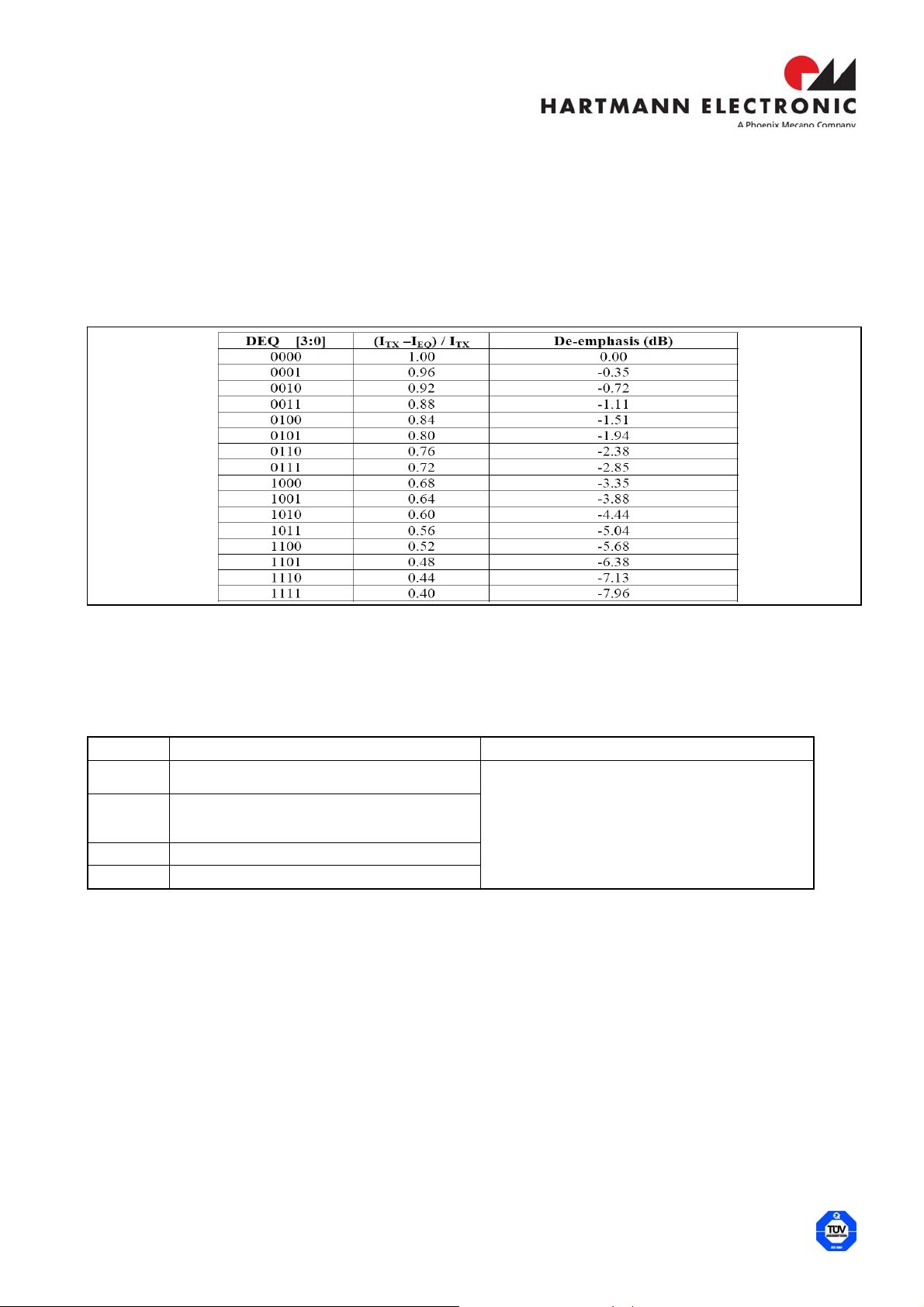

“RXEQCTL[1:0]”

In order to improve the data stream integrity across the channels, the receiver of each port of the Switch includes

a reception equalizer to mitigate the effects of ISI. The reception equalizer is implemented as a selectable high-

pass filter at the input node, and it is capable of removing as much as 0.4UI of ISI related jitter. The following

table shows a simple guideline for selecting the appropriate value to adapt with different lengths or connector

numbers in various applications.

Figure 5: Adjustment of „RXEQTL[1:0“]

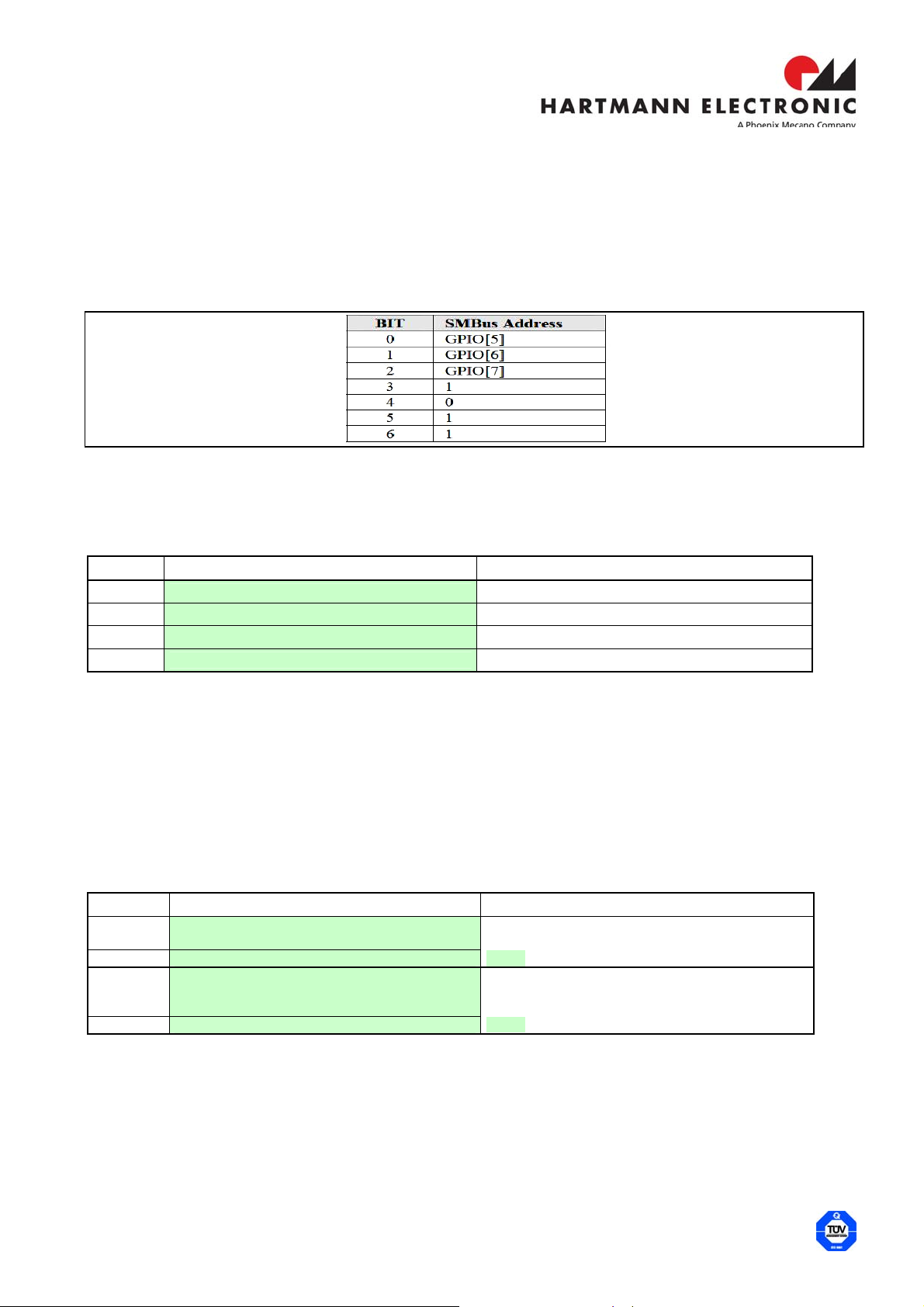

SWDRV

PIN OFF=Default/ON Value

1-8 Bit0(L = OFF) - LODRV Nominal Driver Current

2-7 Bit1(L = OFF) - HIDRV 00=20mA,01=10mA,10=28mA

3-6 Bit0(L = OFF) - RXEQCTL0 RX Equalizer Settings

4-5 Bit1(L = OFF) - RXEQCTL1

00=Jitter>0.25UI,Len>20",CON>=2,

01=Jitter>0.1UI<0.25UI,Len=8"-20",CON<=2,

1X=Jitter<0.1UI,Len<=8",CON<=1

Table 7: Setup of Dip Switch SWDRV. Default setup is marked green.

SWDTX

PIN OFF=Default/ON Value

1-8 Bit0(L = OFF) - DTX0 Multiple Nominal Driver Current

2-7 Bit1(L = OFF) - DTX1 DTX[3:0]

0000-0111 = 1.00-1.35 (+0.05)

3-6 Bit2(L = OFF) - DTX2 1000-1111 = 0.60-0.95 (+0.05)

4-5 Bit3(L = OFF) - DTX3

Table 8: Setup of Dip Switch SWDTX. Default setup is marked green.