hilscher netX 90 Use and care manual

Technical data reference guide

netX 90

Mass production

Hilscher Gesellschaft für Systemautomation mbH

www.hilscher.com

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public

Introduction 2/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

Table of contents

1Introduction.............................................................................................................................................5

1.1 About this document ......................................................................................................................5

1.2 List of revisions...............................................................................................................................5

1.3 References to documents..............................................................................................................5

2General description and features .........................................................................................................6

2.1 Block diagram.................................................................................................................................8

2.2 Technical data netX 90 ..................................................................................................................9

2.3 netX 90 signal description............................................................................................................11

3Core .......................................................................................................................................................16

3.1 CPU..............................................................................................................................................16

3.1.1 Cortex®-M4 CPU ............................................................................................................................ 16

3.1.2 xPIC CPU........................................................................................................................................ 16

3.2 DMAC...........................................................................................................................................17

3.2.1 Overview ......................................................................................................................................... 17

3.2.2 Features.......................................................................................................................................... 18

3.2.3 Typical applications......................................................................................................................... 18

3.2.4 Functional description...................................................................................................................... 19

3.2.5 Data transfer.................................................................................................................................... 20

3.2.6 DMA channel priority....................................................................................................................... 21

3.2.7 DMA flow control............................................................................................................................. 21

3.3 Crypto core...................................................................................................................................21

3.4 Memory map ................................................................................................................................22

3.5 Brown-Out Detector (BOD)..........................................................................................................23

3.6 Power-on reset and DC/DC .........................................................................................................24

3.7 System clock (oscillator) ..............................................................................................................25

3.8 Temperature sensor.....................................................................................................................25

3.9 Interrupt vectors ...........................................................................................................................26

3.10 Timer ............................................................................................................................................28

3.10.1 CPU timer........................................................................................................................................ 28

3.10.2 IEEE 1588 system time................................................................................................................... 29

3.11 Watchdog.....................................................................................................................................30

3.11.1 Function........................................................................................................................................... 30

3.11.2 WDG_ACT signal............................................................................................................................ 30

3.12 Internal memory...........................................................................................................................31

3.12.1 Internal Flash................................................................................................................................... 31

3.12.2 Internal RAM ................................................................................................................................... 31

3.13 External memory..........................................................................................................................32

3.13.1 Overview ......................................................................................................................................... 32

3.13.2 Features.......................................................................................................................................... 33

3.13.3 SDRAM interface............................................................................................................................. 34

3.13.4 SRAM/Flash interface to memory interface controller ..................................................................... 46

4Booting and SYS LED..........................................................................................................................57

4.1 Boot sequence .............................................................................................................................57

4.2 Alternative boot mode..................................................................................................................59

4.3 System LED .................................................................................................................................59

5Interfaces...............................................................................................................................................60

5.1 MMIO - Multiplex Matrix ...............................................................................................................60

5.2 Host interface...............................................................................................................................62

5.2.1 Overview ......................................................................................................................................... 62

5.2.2 Block diagram.................................................................................................................................. 62

5.2.3 Features.......................................................................................................................................... 63

5.2.4 Dual-port memory interface structure.............................................................................................. 64

5.2.5 Parallel dual-port memory interface................................................................................................. 65

5.2.6 Serial dual-port memory interface ................................................................................................... 78

5.2.7 Handshake registers........................................................................................................................ 85

5.2.8 Parallel dual-port memory timing..................................................................................................... 88

5.2.9 Serial dual-port memory timing...................................................................................................... 118

5.3 SQI/SPI ......................................................................................................................................127

5.3.1 Overview ....................................................................................................................................... 127

5.3.2 SQI................................................................................................................................................ 129

Introduction 3/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

5.3.3 SPI0…2_APP and SPI_XPIC_APP............................................................................................... 146

5.3.4 SQI0…1......................................................................................................................................... 151

5.4 I2C..............................................................................................................................................152

5.4.1 Overview ....................................................................................................................................... 152

5.4.2 Block diagram................................................................................................................................ 153

5.4.3 Features........................................................................................................................................ 154

5.4.4 Typical applications....................................................................................................................... 154

5.4.5 Functional description.................................................................................................................... 154

5.4.6 I2C devices.................................................................................................................................... 154

5.4.7 I2C signals..................................................................................................................................... 154

5.4.8 I2C signal conditions ..................................................................................................................... 155

5.4.9 I2C transfers.................................................................................................................................. 155

5.4.10 I2C acknowledge handling ............................................................................................................ 156

5.4.11 I2C 10-bit addressing .................................................................................................................... 156

5.4.12 I2C general call ............................................................................................................................. 157

5.4.13 I2C cycle stretching....................................................................................................................... 157

5.4.14 I/O timing....................................................................................................................................... 158

5.5 Multi LED....................................................................................................................................159

5.5.1 Overview ....................................................................................................................................... 159

5.5.2 Features........................................................................................................................................ 159

5.5.3 Typical applications....................................................................................................................... 160

5.5.4 Functional description.................................................................................................................... 160

5.5.5 Time-multiplexed PWM mode ....................................................................................................... 161

5.5.6 Pass-through mode....................................................................................................................... 162

5.5.7 Features for both modes ............................................................................................................... 162

5.6 GPIO ..........................................................................................................................................163

5.6.1 Overview ....................................................................................................................................... 163

5.6.2 Features........................................................................................................................................ 165

5.6.3 Typical applications....................................................................................................................... 166

5.6.4 Functional description.................................................................................................................... 166

5.6.5 Simple read/write modes............................................................................................................... 166

5.6.6 Counter as system timer................................................................................................................ 167

5.6.7 Event time capture......................................................................................................................... 167

5.6.8 Event counting............................................................................................................................... 169

5.6.9 Active time measurement.............................................................................................................. 170

5.6.10 Watchdog mode............................................................................................................................ 170

5.6.11 Standard PWM.............................................................................................................................. 171

5.6.12 PWM with shadow registers.......................................................................................................... 171

5.6.13 DC-DC PWM................................................................................................................................. 173

5.6.14 Sequencer..................................................................................................................................... 174

5.6.15 Sharing between different CPUs................................................................................................... 175

5.6.16 Interrupt handling .......................................................................................................................... 175

5.6.17 I/O timing....................................................................................................................................... 176

5.7 PIO (application) ........................................................................................................................177

5.8 BiSS/SSi.....................................................................................................................................178

5.8.1 Overview ....................................................................................................................................... 178

5.8.2 Functional description.................................................................................................................... 178

5.8.3 Trigger sources ............................................................................................................................. 179

5.8.4 Interrupt logic................................................................................................................................. 179

5.9 EnDat .........................................................................................................................................180

5.9.1 Overview ....................................................................................................................................... 180

5.9.2 Functional description.................................................................................................................... 180

5.9.3 Trigger sources ............................................................................................................................. 181

5.9.4 Edge detector and pulse former.................................................................................................... 181

5.10 CAN controller............................................................................................................................182

5.10.1 Features........................................................................................................................................ 182

5.11 UART..........................................................................................................................................183

5.12 IO-Link controller........................................................................................................................186

5.12.1 Introduction.................................................................................................................................... 186

5.12.2 Typical application......................................................................................................................... 187

5.13 ADC............................................................................................................................................188

5.14 LVDS..........................................................................................................................................189

5.15 Motion PWM...............................................................................................................................190

5.16 Quadrature decoder...................................................................................................................190

5.17 Ethernet interface.......................................................................................................................191

5.18 Fieldbus interface.......................................................................................................................193

6Debugging...........................................................................................................................................194

Introduction 4/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

7Electrical specification ......................................................................................................................194

7.1 Absolute max. ratings.................................................................................................................195

7.2 Power-up and down sequencing................................................................................................195

7.3 Power consumption / Power dissipation....................................................................................195

7.3.1 Power consumption of netX 90...................................................................................................... 195

7.4 AC/DC specifications .................................................................................................................195

7.4.1 Oscillator ....................................................................................................................................... 196

7.4.2 Power-on reset and DC/DC........................................................................................................... 196

7.4.3 BOD............................................................................................................................................... 197

7.4.4 ADC............................................................................................................................................... 197

7.5 Failure rate (FIT)........................................................................................................................197

8netX 90 package and signal information .........................................................................................198

8.1 Pin table sorted by signals .........................................................................................................198

8.2 Pin table sorted by pin number ..................................................................................................204

8.3 Pin overview netX 90 .................................................................................................................210

8.4 PAD type explanation.................................................................................................................212

8.5 Schematic view of netX 90 PAD types.......................................................................................213

8.6 netX 90 package ........................................................................................................................214

8.7 Thermal resistance.....................................................................................................................216

8.8 Moisture sensitivity level ............................................................................................................216

9Appendix .............................................................................................................................................217

9.1 Terms, abbreviations, and definitions ........................................................................................217

9.2 Legal notes.................................................................................................................................219

9.3 Registered trademarks...............................................................................................................222

9.4 List of tables...............................................................................................................................223

9.5 List of figures..............................................................................................................................224

9.6 Contacts .....................................................................................................................................227

Introduction 5/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

1 Introduction

1.1 About this document

This document describes the netX 90 chip functions.

1.2 List of revisions

Rev Date Name Chapter Revision

1 2017-06-27 HN all Preliminary.

2 2018-09-13 HN, NM,

HH all Completely revised.

Table 1: List of revisions

1.3 References to documents

This document refers to the following documents:

[1] Hilscher Gesellschaft für Systemautomation mbH: regdef_netx90_arm_app.html, Englisch,

2018.

[2] Hilscher Gesellschaft für Systemautomation mbH: Design-In Guide, netX 90, Revision 2,

English, 2018.

[3] Hilscher Gesellschaft für Systemautomation mbH: Getting started, netX Studio CDT, netX 90

development, Revision 4, English, 2018.

[4] Hilscher Gesellschaft für Systemautomation mbH: Programming Reference Guide, xPIC

Instruction Set, netX 6/10/51/52, Revision 1, English, 2015.

[5] ARM: ARMv7-M Architecture Reference Manual, ARM DDI0403E.B, English, 2014.

Download: http://infocenter.arm.com/help/index.jsp

[6] Philips Semiconductors: The I2C-Bus Specification, version 2.1, 01.2000, English.

[7] iC-Haus GmbH: http://www.biss-interface.com/

[8] ams Sensors Germany GmbH: http://www.mazet.de/en/products/industrial-metrology/data-

sheets/item/445-endat-2-2-master-basic.html

Table 2: References to documents

General description and features 6/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

2 General description and features

The netX 90 is a highly integrated Industrial Ethernet node in a 10x10 mm2, 144-pin BGA footprint

with two ARM® Cortex®-M4 cores, on-chip Flash memory, Fast Ethernet PHYs, DC/DC converter,

POR circuit, and a feature-rich set of on-chip peripherals.

The industrial communication SoC fulfils the highest demand on flexibility, determinism and

performance in terms of multiprotocol capability and low latency for short cycle times. As a result,

the netX 90 provides a superior solution with an unmatched protocol flexibility for a variety of

industrial slave or device applications in the process and factory automation.

Enhanced multiprotocol capability

The SoC features two flexible communication (xC) IPs, which support all popular Industrial

Ethernet standards, i.e. hard real-time. Most importantly, the xC architecture flexibly adapts by

software to emerging standards and future network requirements such as TSN.

Two separate system paradigms

One highlight of the chip’s internal architecture is the logical separation of the communication tasks

and the application tasks, both from software quality and security aspects. The partitioning restricts

the software access to on-chip peripherals on either side.

Built-in security and diagnostics

Built-in security features enable developers to apply a secure by design concept by building layers

of security as outlined in the IEC 62443, coupled with built-in diagnostics to monitor operating

conditions for IIoT-enabled cloud services, e.g. predictive maintenance.

Prebuilt communication firmware

Software protocol stacks for communication tasks come as prebuilt firmware, i.e. tested and pre-

certified by Hilscher. The data exchange with the protocol stack interface using the dual-ported

memory (DPM) enables application developers to quickly set up a network prototype.

Two primary design-in uses cases

Suitable for modular embedded designs as companion chip with host interface that easily pairs

with custom-specific host application processors. The host interface ensures a high degree of

interoperability for maximum data throughput as either parallel or serial interfaces.

Suitable for standalone chip application designs that make use of the second Cortex®-M4 at 100

MHz with DSP and FPU support, enhanced by a feature-rich set of standard and industry-related

peripheral units with connectivity for highly compact product application designs.

General description and features 7/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

netX 90 at a glance

Best-in class real-time

Supports PROFINET IO Device V2.3 with

Fast startup (FSU),

Dynamic Frame Packing (DFP), and

Fast-Forwarding (FFWD)

Scalable SoC platform

Standalone chip application or companion chip with host interface

Multiprotocol capability

Supports all popular Industrial Ethernet and Fieldbus standards

Embedded application

Feature-rich set of standard and industry-related peripheral units

Industrial IoT ready

Built-in security and diagnostic features for IIoT enabled services

Energy-efficient SoC

Suitable for product application designs with smallest form factors

Application examples

Multiprotocol chip interface for motion control

Black channel communication for functional safety

Variety of sensors and actuators for industrial control

Gateway interface or adapter module for universal encoders

LVDSPHY based low-cost backplane bus for industrial protocols

Remote I/O with multichannel IO-Link or as analog/digital I/O blocks

Suitable for any type of slave or device applications that require Industrial Ethernet or Fieldbus

connectivity such as instrumentations, pneumatics, gateways, and many more.

General description and features 8/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

2.1 Block diagram

Cortex M4

Subsystem

ARM App

Intlogic App

Intlogic Com

Crypt System

Communication Side Dataswitch

No access from application side except via IDPM.

Access to App side possible for debug and secure boot.

For accessibility view netxtiny_master_slaves interconnection Excel sheet

Cortex M4

Subsystem

ARM Com

4x 8kB pRAM

2x 8kB dRAM

2ch Ethernet PHY

INTRAM0 128kB

INTRAM1 128kB

INTRAM3 64kB

INTRAM4 64kB

INTRAMHS 32kB

Dual Handshake Cells

AHB Master Channels

AHB Slave Channels

BootROM 128kB

SWD

SPM1

acyclic

DPM0/DPM1/IDPM cfg

MEM8

DPM HostCPU16

or

Peripherals:

1x I2C

1x UART

3x SPI

2x SQI

2x CAN

29x PIO

Com ARM

xC01

Framebuffer

xPIC Com System

2x PHY-Ctrl

Peripherals:

2x I2C

RDY/RUN

Reset-Out

1x UART

1x SPI

xC Config

Pointer FIFO

xC BufMan

Trig/Sample

FMMUSM

xPIC App System

DS D IS

xPIC Com

Subsystem

8kB dRAM

8kB pRAM

Systime LT

Timer

WDG

CPU-Ping

DI

INTRAM2 128kB

INTRAM6 32kB App ARM

INTRAM7 32kB App xPIC

Com xPIC INTRAM5 32kB

DPM0/

SPM0

general or

fast cyclic

EA data

Win

SDRAM

Multimaster

1CS x

256MB

Flash/NVRAM

3CS x 32MB

ExtBus8/16

Shared Dataswitch

Cfg Channels (APB)

Win

HIF

SPM0

SPM0

MEM16

18 MMIO

SPM1 or

or

or

or

INTFLASH0 512kB

Motion:

2x BISS/SSI

2x EnDAT

M-PWM

M-Encoder

BOD BOD Stat

ETH

MAC

MII2

LVDS CTRL

LVDS-MII tunnels

2xMII+MDIO or 2xFieldbus

boot

App ARM

Start (reset

release) from

Com-Side (global

NETX Ctrl)

INTRAM, INTFLASH:

BIST, ECC(2bit detect, 1bit cor.)

LX

VDD3.3

VDDcore

ECC status

Clock

Supervisor

INTFLASH1 512kB

INTRAM, INTFLASH:

BIST, ECC(2bit detect, 1bit cor.)

DC/DC

VDD3.3

->

VDDcore

SQI eXecute in Place

1CS x 64MB

1x I2C

8x IO-Link

xPIC App

Subsystem

8kB dRAM

8kB pRAM

VIC

Timer

WDG

CPU-Ping

cfg DI

cfg

DIS

DMAC

(4 ch)

DMAC

(4 ch)

CoreSight, ETM

NVIC

MPU NVIC

MPU

FPU

Debug Master

Analog Macros

Peripherals (int, ext)

System Slaves/Dataswitch

System Master

Memory (SRAM, read-only, ext.)

boot Com ARM

Win

IDPM

Slave

SHA1 (160)

SHA2(256,284,512)

AES(128,192,256)

MD5

RSA / ECC (MTGY)

xC01

Subsystem

xMAC

tPEC

rPEC

xMAC

tPEC

rPEC

xC Systime VIC

Systime LT

Watchdog

Timer, 2x Systime

Systime LT

CPU-Ping

Watchdog

Timer, Systime

Systime LT

CPU-Ping

xC Bridge

DPM Tripple

Buffer

Win

Application Side Dataswitch

Access from communication side possible for debug

and secure boot.

Access to Com-side only via IDPM.

For accessibility view netxtiny_master_slaves

interconnection Excel sheet.

GPIO xPIC App port

trace

Boundary Scan

SWD/JTAG

Wdg-active

Reset Ctrl

RstIn_n

PwrOnRst

8x Com-LEDs

OSC(2.5MHz)

external

crystal

(25MHz)

PLL(400MHz)

Memory BIST

INTFLASH2 512kB

4x Multi-LED Ctrl

MLED0..3

16x App-LEDs

8x Multi-LED Ctrl

MLED4..11

4x GPIO

1x Timer

PWM

Capture

Event

Stream

Blink

GPIO ARM App port

8x GPIO

3x Timer

PWM

Capture

Event

Stream

Blink

Slaves/Memories: Access from both

sides, Com has higher priority

Master: Access to both sides

cfg cfg

Intlogic Shared

Global NETX Ctrl

cfg of external memories

IO-cfg (MUX, physical)

SPI/SQI (XiP cfg/prog)

M-ADC

CTRL

4x ADC

12bit SAR,

1MS/s

Ain MUX

20x Ain

(2+2+8+8)

Temp.

VDD

4x SH

INTFLASH0/1 (cfg/prog)

INTFLASH2 (cfg/prog)

nFIFO

gBufMan

ECC status

CRC

M

Debug Slave

MMIO cfg

UART

Figure 1: Block diagram

General description and features 9/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

2.2 Technical data netX 90

Category Features Communication Application

Core ARM® Processor Cortex®-M4 at 100 MHz with MPU Cortex®-M4 at 100 MHz with MPU and

FPU

Hilscher 32-bit RISC 1 x xPIC at 100 MHz 1 x xPIC at 100 MHz

Tightly-coupled memory 1 x D-TCM, 8 KB, 1 x I-TCM, 8 KB 1 x D-TCM, 8 KB, 1 x I-TCM, 8 KB

Memory SRAM (ECC) 576 KB 64 KB

Flash (ECC) 1024 KB 512 KB

Mask ROM 128 KB -

System DMA controller 4 channels 4 channels

WDC (ARM / xPIC) 1 / 1 1 / 1

Timer (ARM / xPIC) 3x 32-bit / 3x 32-bit 3x 32-bit / 3x 32-bit

Built-in bootloader Host Interface (DPM/SPM), Ethernet (xC0 DHCP/TFTP), Serial (FTDI USB to

JTAG/UART)

Network xC Subsystem 2 channels -

IEEE 1588 SysTime 2 1

Fast Ethernet PHY Dual-port, FX support -

100 Mbps LVDSPHY Dual-port -

Ethernet MAC Ethernet MAC 10 / 100 Mbps, MII

Peripheral UART (up to 6.25 Mbaud) 1 (shared) 3

SPI (up to 50 MHz) - 4

SQI (up to 50 MHz) 2 (Master only, with SPI mode)

I2C (up to 3.4 MHz) 2 2

CAN 2.0B (up to 1 Mbps) - 2

IO-Link V1.1 controller - 8 channels

MLED (PWM tuned) 4 8

HIF PIO / PIO / GPIO / MMIO - / - / 4 / - up to 41 / 29 / 8 / 18

Mixed signal Timer (PWM, IC/OC) 4x 32-bit (min. 10 ns) 8x 32-bit (min. 10 ns)

Motion PWM unit - 1

ADC SAR (12-bit, 2 Msps) 2x 2 channels and 2x 8 channels

Quadrature decoder - 2

EnDat 2.2 (Master E6) - 2 (with RTM)

BiSS / SSI (Master BiSS C) - 2 / 2

Host interface Parallel (DPM) 8/16-bit (Read access min. 55 ns) Internal 32-bit

Serial (SPM) 2x SPI (up to 125 MHz) /

QSPI (up to 33 MHz) -

MAC (PHY mode) MII (10/100 Mbps) -

External

memory SRAM / NOR / NAND /

SDRAM ✓/ ✓/ - / ✓(8/16-bit)

SD/MMC / SDIO SPI mode / -

SQI (XiP) ✓

Security Crypto core SSL/TLS accelerator, up to RSA-4096, ECC-512, AES-256, and SHA-512

Secure boot Mask ROM code, EMSA-PSS

Built-in support Security levels, AHB Firewall

Debug Debug / Trace JTAG/SWD, 4-bit TPIU

Boundary scan JTAG

General description and features 10/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

Category Features Communication Application

Analog DC/DC / POR / BOD ✓/ ✓/ ✓

Thermal diode ✓

Clock supervisor Xtal (RC-Osc)

Electrical Power supply Single 3.3V

Temperature range Ta-40°C ... +85°C

Power consumption TBD (≤1 W)

Package dimension 144-pin BGA, 10x10 mm2, 0.8 mm Ball Pitch

Table 3: Technical data

General description and features 11/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

2.3 netX 90 signal description

This list groups the signals of the pin assignment table with the multiplexed signals (“shared with”

operating modes), see chapter netX 90 package and signal information on page 198.

General

RST_IN_N Reset input

RDY_N Ready (RDY-LED/Console mode)

RUN_N Run (RUN-LED/Alternative boot mode)

MLED0…3 Multi-LED/Status LEDs COM0/1

COM_IO0…3 Communication input output/peripherals

Power

VDDC Power supply voltage, core

VDDIO Power supply voltage, input output

VSS (GND) Ground

PHY_VDDC Internal PHY, power supply, core

PHY_VDDIO

Internal PHY, power supply, input output

VDD_PLL Power supply voltage, core - phase lock loop

Misc Analog

OSC_XTI (XTALIN) 25 MHz Crystal input

OSC_XTO (XTALOUT) 25 MHz Crystal output

DCDC_LX_OUT DCDC output inductor

VSS_REF Ground, reference voltage

VREF_ADC Reference voltage, analog-to-digital converter

BOD Brown-out detection

MII – Media-Independent Interface (External Ethernet PHY)

MII_MDC Ethernet MAC management data clock

MII_MDIO Ethernet MAC management data input output

MII0+1_RXCLK Ethernet MAC receive clock

MII0+1_RXD0…3 Ethernet MAC receive data 0...3

MII0+1_RXDV Ethernet MAC receive data valid

MII0+1_RXER Ethernet MAC receive error

MII0+1_TXCLK Ethernet MAC transmit clock

MII0+1_TXD0…3 Ethernet MAC transmit data 0...3

MII0+1_TXEN Ethernet MAC transmit enable

MII0+1_TXER Ethernet MAC transmit error

MII0+1_COL

Ethernet MAC collision

MII0+1_CRS Ethernet MAC carrier sense

PHY0+1_LED_LINK_IN Ethernet PHY Link LED input

RST_OUT_N Reset output

CLK25OUT Clock 25 output

LVDS (Integrated dual LVDSPHY)

LVDS0+1_RXN LVDSPHY, receive input negative

LVDS0+1_RXP LVDSPHY, receive input positive

LVDS0+1_TXN LVDSPHY, transmit output negative

LVDS0+1_TXP LVDSPHY, transmit output positive

General description and features 12/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

PHY (Integrated dual Ethernet PHY)

PHY_EXTRES Ethernet PHY, reference resistor

PHY0+1_RXN Ethernet PHY, receive input negative

PHY0+1_RXP Ethernet PHY, receive input positive

PHY0+1_TXN

Ethernet PHY, transmit output negative

PHY0+1_TXP Ethernet PHY, transmit output positive

FO (Fiber optic)

FO0+1_RX Ethernet PHY, fiber optic receive data

FO0+1_SD Ethernet PHY, fiber optic signal detect

FO0+1_TX Ethernet PHY, fiber optic transmit data

FO0+1_EN_TX Ethernet PHY, fiber optic enable control

MMIO

MMIO0…17 Multiplex matrix I/O 0...17

PIO_APP

PIO_APP0…28 Programmable Input/Output, Application side

MENC

MENC_MP0+1 Motion encoder MP

MENC0+1_A Motion encoder, input A

MENC0+1_B Motion encoder, input B

MENC0+1_N Motion encoder, input index

MPWM

MPWM_BRAKE Motion Pulse Width Modulation, Brake

MPWM_FAIL Motion Pulse Width Modulation, Fail

MPWM0…5 Motion Pulse Width Modulation 0…5

HIF (8-bit or 16-bit DPM interface)

HIF_A0...17 Host interface address lines 0…17

HIF_BHEN Host interface, byte high enable

HIF_CSN Host interface, chip select

HIF_D0...15 Host interface data lines 0…15

HIF_DIRQ Host interface, data interrupt request

HIF_RDN Host interface, read

HIF_RDY Host interface, ready

HIF_SDCLK Host interface, serial data clock

HIF_SIRQ Host interface, synchron interrupt request

HIF_WRN Host interface, write

DEBUG

JT_TCK JTAG test clock

JT_TMS JTAG test mode select

JT_TDI JTAG test data input

JT_TDO JTAG test data output

JT_TRST JTAG test reset

SWDCLK Serial Wire Debug clock

SWDIO Serial Wire Debug data input output

TRACE_DATA0…3 Trace port data

TRACECLK

Trace port clock

TRACECTL Trace port control

General description and features 13/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

EXT (Extension bus/memory interface)

EXT_A0…17 Extension bus address lines 0…17

EXT_BHEN Extension bus byte high enable

EXT_CS0…2N Extension bus chip select 0…2

EXT_D0…15

Extension bus data lines 0…15

EXT_RDN Extension bus read enable

EXT_RDY Extension bus ready

EXT_WRN Extension bus write enable

IO_LINK (Controller interface)

IO_LINK0…7_IN IO-Link 0…7 input

IO_LINK0…7_OE IO-Link 0…7 output enable

IO_LINK0…7_OUT

IO-Link 0…7 output

IO_LINK0…7_WAKEUP IO-Link 0…7 wake up

SDRAM (Synchronous Dynamic Random Access Memory interface)

SD_A0…12 SDRAM address lines 0…12

SD_BA0 SDRAM bank address 0

SD_BA1 SDRAM bank address 1

SD_CASN SDRAM column address strobe

SD_CKE SDRAM clock enable

SD_CLK SDRAM clock

SD_CSN SDRAM chip select

SD_D0…15 SDRAM data lines 0…15

SD_DQM0+1 SDRAM data qualifier mask 0+1

SD_RASN SDRAM row address strobe

SD_WEN SDRAM write enable

XM (Fieldbus interface)

FB0+1CLK Fieldbus clock

XM0+1_ECLK XMAC fieldbus, external clock

XM0+1_IO0…5 XMAC fieldbus, input output 0…5

XM0+1_RX XMAC fieldbus, receive

XM0+1_TX XMAC fieldbus, transmit

XM0+1_TXOE

XMAC fieldbus, transmit output enable

XM0+1_TX_ECLK XMAC fieldbus, transmit external clock

XM0+1_TXOE_ECLK XMAC fieldbus, transmit output enable, external clock

GPIO

GPIO0…7 and 8…11 General purpose input/output 0…7 application and 8…11 communication

SPM (Serial DPM interface)

DPM0+1_SPI_CLK Serial DPM (SPI, SQI), clock

DPM0+1_SPI_CSN Serial DPM (SPI, SQI), chip select

DPM0+1_SPI_DIRQ Serial DPM (SPI, SQI), data interrupt request

DPM0+1_SPI_MISO Serial DPM (SPI), master in / slave out;

Serial DPM (SQI), serial input/output data 1

DPM0+1_SPI_MOSI Serial DPM (SPI), master out / slave in;

Serial DPM (SQI), serial input/output data 0

DPM0+1_SPI_SIRQ

Serial DPM (SPI, SQI), synchron interrupt request

DPM0+1_SQI_SIO2+3 Serial DPM (SQI), serial input/output data 2+3

General description and features 14/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

UART (Universal Asynchronous Receiver/Transmitter)

UART_APP_CTSN UART, application, clear to send

UART_APP_RTSN UART, application, request to send

UART_APP_RXD UART, application, receive data

UART_APP_TXD UART, application, transmit data

UART_CTSN UART, clear to send

UART_RTSN UART, request to send

UART_RXD UART, receive data

UART_TXD UART, transmit data

UART_XPIC_APP_CTSN UART, xPIC application, clear to send

UART_XPIC_APP_RTSN UART, xPIC application, request to send

UART_XPIC_APP_RXD

UART, xPIC application, receive data

UART_XPIC_APP_TXD UART, xPIC application, transmit data

SQI (Serial Quad I/O) / XiP (Serial flash memory interface)

SQI_CLK SQI, clock signal

SQI_CS0..2N SQI, chip select signal, negated

SQI_MOSI SQI, master in / slave out (serial input/output data 0)

SQI_MISO SQI, master out / slave in (serial input/output data 1)

SQI_SIO2+3 SQI, serial input/output data 2+3

SPI (Serial Peripheral Interface)

SPI0_APP_CS0+1N SPI, application, chip select signal, negated

SPI0…2_APP_CLK SPI, application, clock signal

SPI0…2_APP_MISO SPI, application, master in / slave out

SPI0…2_APP_MOSI SPI, application, master out / slave in

SPI1+2_APP_CS0…2N SPI, application, chip select, negated

SPI_XPIC_APP_CLK SPI, xPIC application, clock signal

SPI_XPIC_APP_CS0…2 SPI, xPIC application, chip select

SPI_XPIC_APP_MISO SPI, xPIC application, master in / slave out

SPI_XPIC_APP_MOSI SPI, xPIC application, master out / slave in

SQI (Serial Quad I/O)

SQI0_APP_CS1…2N SQI, application, chip select signal, negated

SQI0+1_APP_CLK (_B) SQI, application, clock signal (B = alternative)

SQI0+1_APP_CS0N (_B) SQI, application, chip select signal, negated, (B = alternative)

SQI0+1_APP_MISO (_B) SQI, application, master in / slave out (serial input/output data 1) (B = alternative)

SQI0+1_APP_MOSI (_B) SQI, application, master out / slave in (serial input/output data 0) (B = alternative)

SQI0+1_APP_SIO2+3 (_B) SQI, application, serial input/output data 2+3 (B = alternative)

MLED

MLED0…11 Multi Light Emitting Diode 0…3 communication; 4...11 application

ENDAT (Master 2.2)

ENDAT0+1_CLK Encoder Data clock output

ENDAT0+1_IN Encoder Data data input

ENDAT0+1_OE Encoder Data output enable

ENDAT0+1_OUT Encoder Data data output

General description and features 15/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

I2C

I2C_APP_SCL I2C, application, clock signal

I2C_APP_SDA I2C, application, data signal

I2C_XPIC_APP_SCL I2C, xPIC application, clock signal

I2C_XPIC_APP_SDA I2C, xPIC application, data signal

I2C0+1_COM_SCL I2C, communication, clock signal

I2C0+1_COM_SDA I2C, communication, data signal

BISS (Master BiSS C)

BISS0+1_MA Bidirectional/Serial/Synchronous clock output

BISS0+1_MO Bidirectional/Serial/Synchronous data output

BISS0+1_SL Bidirectional/Serial/Synchronous data input

ADC

ADC0+1_IN0+1 Analog-to-digital converter input 0+1

ADC2+3_IN0…7 Analog-to-digital converter input 0…7

CAN

CAN0+1_APP_RX CAN, application, receive data

CAN0+1_APP_TX CAN, application, transmit data

XC

XC_TRIGGER0…1 RTE synchronization signals

Table 4: netX 90 signal description

Core 16/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

3 Core

3.1 CPU

3.1.1 Cortex®-M4 CPU

The application part of the chip features a high-performance ARM® Cortex®-M4 processor core:

ARMv7ME Architecture

Thumb-2 Technology

125 DMIPS

3-stage pipeline

Integrated NVIC and MPU

Integrated DSP and SIMD instructions

Single cycle MAC

Single precision FPU

Documentation about Cortex®-M4, see reference [5].

3.1.2 xPIC CPU

The xPIC (fleXible Peripheral Interface Controller) is a 32-bit RISC CPU from Hilscher optimized

for fast and deterministic data processing. For instruction set, see reference [4].

The xPIC is used as peripheral controller for interfaces such as IO-Link, Ethernet MAC, etc. for

which Hilscher provides low-level software drivers as HAL (Hardware Abstraction Layer) for the

Cortex®-M4.

The real-time capability of the xPIC enables Hilscher to program code-optimized, custom-specific

features that are not supported by standard peripheral units. Therefore, the xPIC has a dedicated

internal peripheral bus to ensure a deterministic response for very time critical IO tasks. If the xPIC

is not used for the application, all on-chip peripherals connected at xPIC App System (see Figure

1) can be used by the Cortex®-M4 CPU.

Core 17/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

3.2 DMAC

3.2.1 Overview

The DMA controller manages data transfers between DMA slaves and memory slaves without

using the ARM CPU. This allows fast data transfers that do not affect the CPU load.

A slave is a device selected by a controlling master as the source or target of a transfer.

A slave can also begin a service request using an interrupt.

The DMA controller

is functionally compatible with the ARM master DMA controller (PL081)

is designed to use only one master channel in the system

can support up to three DMA channels

Each DMA channel can be programmed for various features, e.g.:

Transfer size

Interrupt generation

Memory and I/O address space

Transfer direction

The netX 90 includes two completely independent DMA controllers: One on the com-side and one

on the app-side. Therefore, both DMACs are connected to different peripherals. Some peripherals

are connected to both DMACs because they can be operated from either side (not at the same

time, of course).

DMAC

cfg

Peripheral 0

INTRAM

Peripheral x

...

Peripheral x+1

Peripheral y

...

flow control

... ...

DMAC

cfg

Peripheral y+1

INTRAM

Peripheral z

...

flow control

DMAC_MUX

6

... ...

Com-side App-sideshared

Dataswitch Dataswitch Dataswitch

Figure 2: Simplified block diagram of the DMA controllers

Core 18/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

3.2.2 Features

Compatible with ARM DMAC (PL081) software and register

1 AHBL master port used for DMA transfer and linked list operations

1 AHBL slave port as configuration interface

3 DMA channels with separated linked lists and configuration registers

4 FIFO elements (32-bit) per channel

Incrementing or non-incrementing addressing for source and destination

Programmable burst size.

32, 16, and 8-bit support for source and destination in all combinations

Fixed DMA channel priority:

Channel 0 has the highest priority

Channel 2 has the lowest priority

Memory-to-memory, memory-to-peripheral, peripheral-to-memory DMA transfers

DMAC or peripheral flow control

Programmable interrupt capabilities, e.g.:

error and finish interrupt generation

interrupt masking and clearing

The netX system and bus matrix implementation do not support the following DMAC features:

No AHB-protected transfers (user mode, buffer ability, cacheable)

No AHB-locked transfers

No big-endian support

No peripheral-to-peripheral DMA transfers

3.2.3 Typical applications

Optimized memory copy function

Optimized peripheral data block transfer function

Periodical data transfer to slave/master

Core 19/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

3.2.4 Functional description

The following section provides a detailed description of the DMA controller and its features.

The 3-channel DMA controller supports the following transactions in the netX system:

Peripheral-to-memory transfer

Memory-to-peripheral transfer

Memory-to-memory transfer

The netX system and its peripherals do not support peripheral-to-peripheral transfers, but they are

configurable via the register interface.

FIFO FIFO FIFO

src addr

dest addr

linked list

control

src addr

dest addr

linked list

control

src addr

dest addr

linked list

control

Channel 0 Channel 1 Channel 2

Interrupts

Error Interrupt Terminal Count Interrupt

Interrupt

AHBL

(slave)

AHBL (master)

Flow control

interface

Mux / priority

DMA Controller

or

Figure 3: Simplified internal structure of the DMA controller

Each channel supports a unidirectional DMA transfer, up to 32 bit, for a single source and

destination address. A bidirectional transfer therefore requires one channel for transmit and one for

receive.

The source and destination address can be a memory region or a DMA-capable peripheral device

of the netX. A system master programs the DMA controller via the AHBL slave interface.

Core 20/227

netX 90 | Technical data reference guide

DOC160609TRG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2017-2018

3.2.5 Data transfer

The bus width for the AHB master is 32 bit. The width of source and destination transfers may

differ. It can be identical to or narrower than that of the physical bus width. The DMA controller

packs or unpacks data according to the programming parameters.

The DMA controller supports little-endian addressing only. Internally, the DMAC treats all data as a

stream of bytes instead of 16-bit or 32-bit quantities.

Note: To avoid byte swapping of the data, always address peripheral interfaces in 32-bit

mode, if possible.

Source width Destination width Source transfer Source data Destination transfer Destination data

8 8 1/[7:0]

2/[15:8]

3/[23:16]

4/[31:24]

21

43

65

87

1/[7:0]

2/[15:8]

3/[23:16]

4/[31:24]

21212121

43434343

65656565

87878787

8 16 1/[7:0]

2/[15:8]

3/[23:16]

4/[31:24]

21

43

65

87

1/[15:0]

2/[31:16] 43214321

87658765

8 32 1/[7:0]

2/[15:8]

3/[23:16]

4/[31:24]

21

43

65

87

1/[31:0] 87654321

16 8 1/[7:0]

1/[15:8]

2/[23:16]

2/[31:24]

21

43

65

87

1/[7:0]

2/[15:8]

3/[23:16]

4/[31:24]

21212121

43434343

65656565

87878787

16 16 1/[7:0]

1/[15:8]

2/[23:16]

2/[31:24]

21

43

65

87

1/[15:0]

2/[31:16] 43214321

87658765

16 32 1/[7:0]

1/[15:8]

2/[23:16]

2/[31:24]

21

43

65

87

1/[31:0] 87654321

32 8 1/[7:0]

1/[15:8]

1/[23:16]

1/[31:24]

21

43

65

87

1/[7:0]

2/[15:8]

3/[23:16]

4/[31:24]

21212121

43434343

65656565

87878787

32 16 1/[7:0]

1/[15:8]

1/[23:16]

1/[31:24]

21

43

65

87

1/[15:0]

2/[31:16] 43214321

87658765

32 32 1/[7:0]

1/[15:8]

1/[23:16]

1/[31:24]

21

43

65

87

1/[31:0] 87654321

Table 5: DMA controllers data packing or unpacking depending on the programmed mode

To reduce latency and to improve the DMA transfer performance, observe the following

recommendations:

If feasible, use separate memory areas for data storage and linked list information.

All memory and peripheral transactions should be 32-bit wide to improve bus efficiency.

Other manuals for netX 90

2

Table of contents

Popular Microcontroller manuals by other brands

Texas Instruments

Texas Instruments TMDX654IDKEVM quick start guide

STMicroelectronics

STMicroelectronics 32L4R9IDISCOVERY user manual

Infineon

Infineon Cypress CY8CKIT-064S0S2-4343W Kit Guide

Renesas

Renesas DA14706 PRO user manual

Texas Instruments

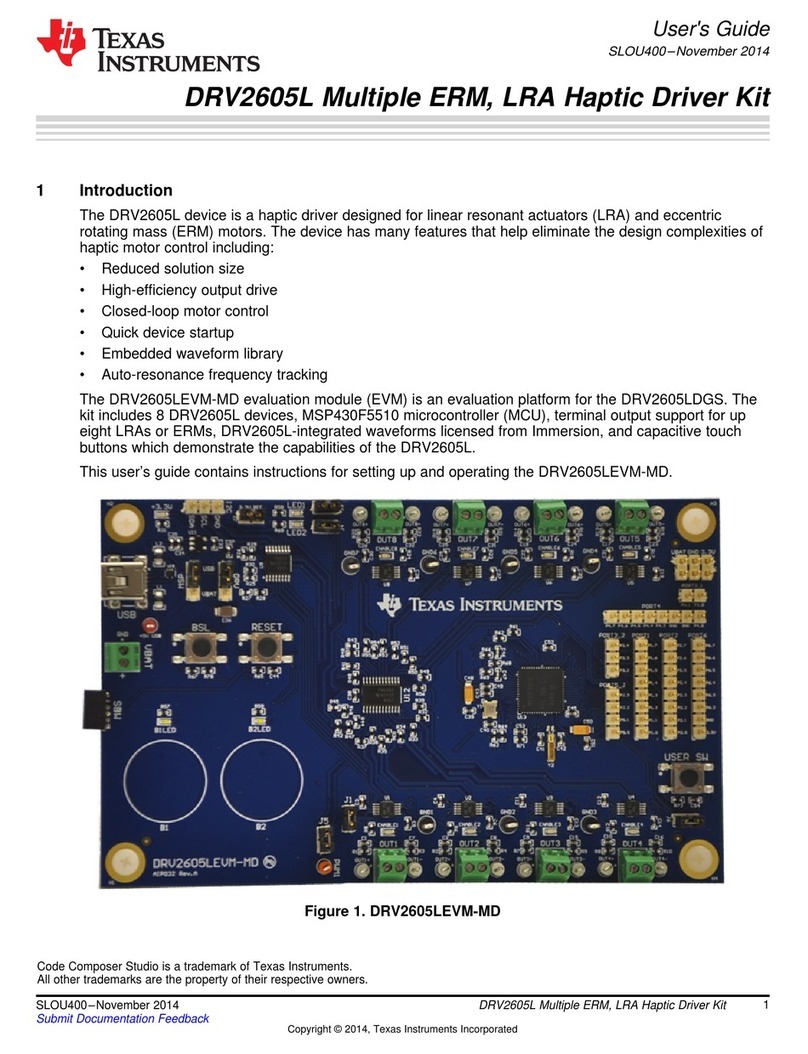

Texas Instruments DRV2605L user guide

Cypress

Cypress PSoC CY8CKIT-048 quick start guide

Texas Instruments

Texas Instruments DA8xx EVM PSP user guide

STMicroelectronics

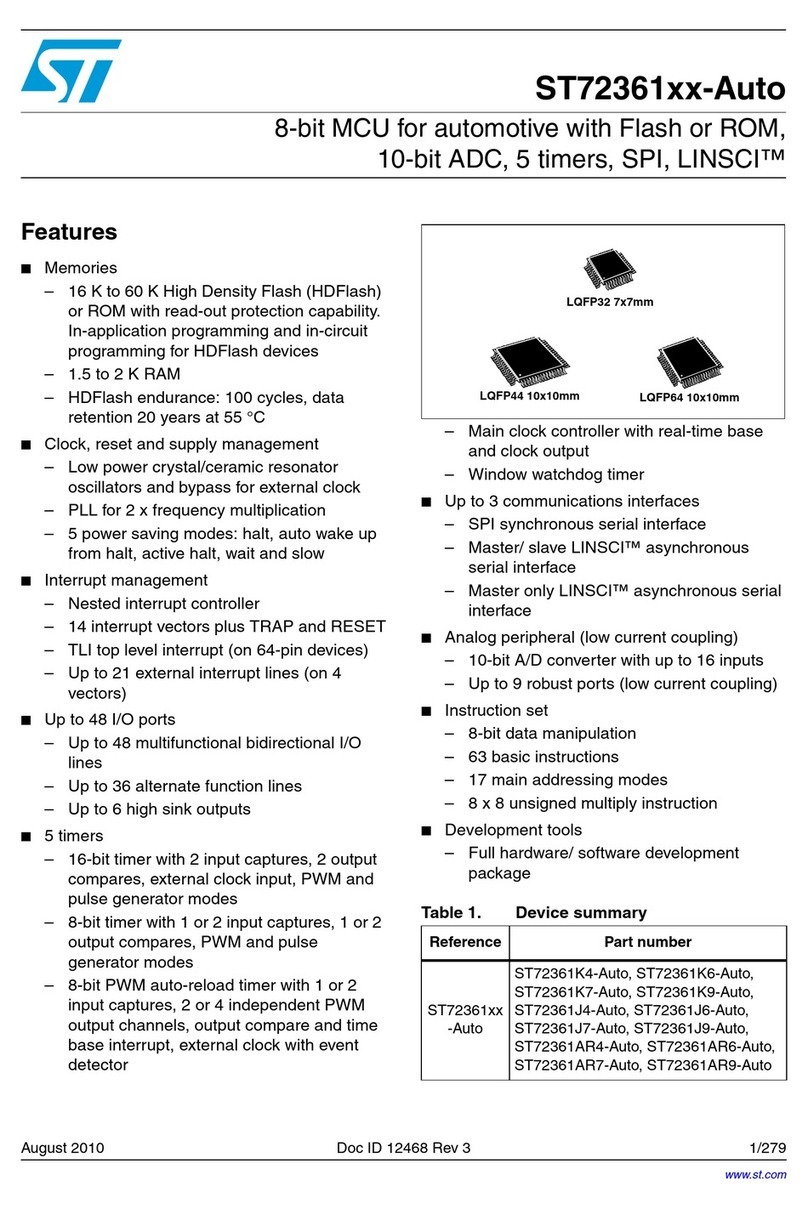

STMicroelectronics ST72361 Auto Series manual

PLX Technology

PLX Technology PCI 9054RDK-860 Hardware reference manual

Linear

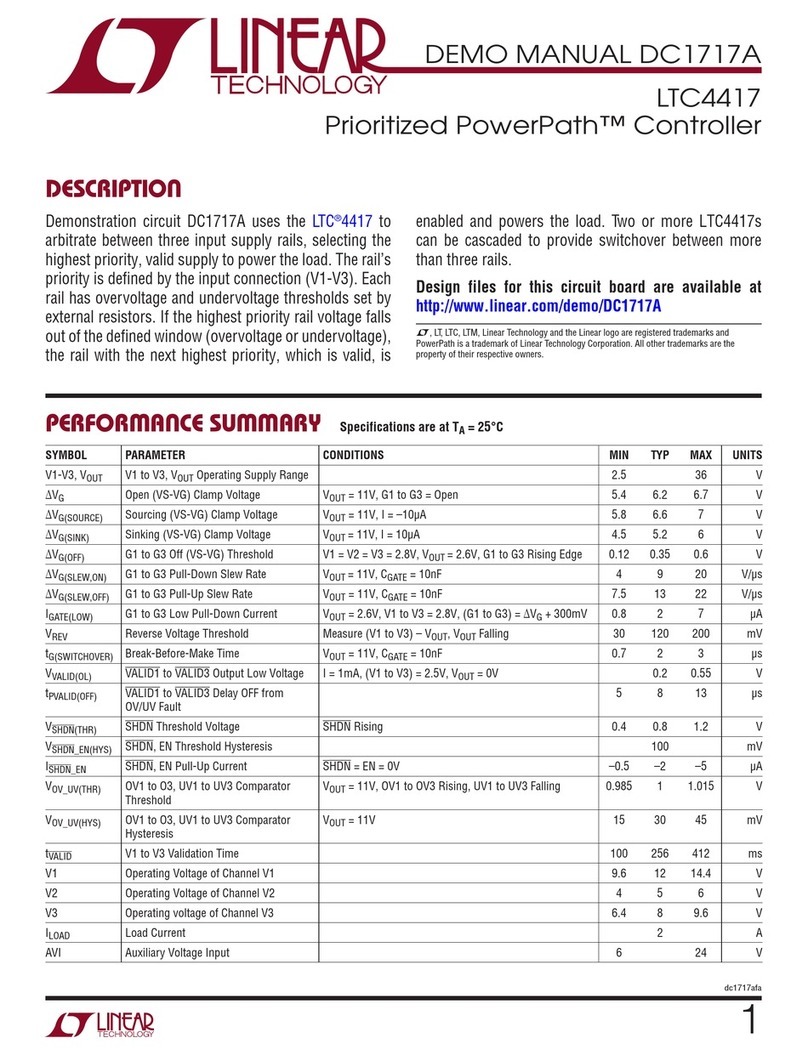

Linear DC1717A Demo Manual

ScioSense

ScioSense GP30-DEV-KIT user guide

NXP Semiconductors

NXP Semiconductors QN9080 quick start guide