4 - 3

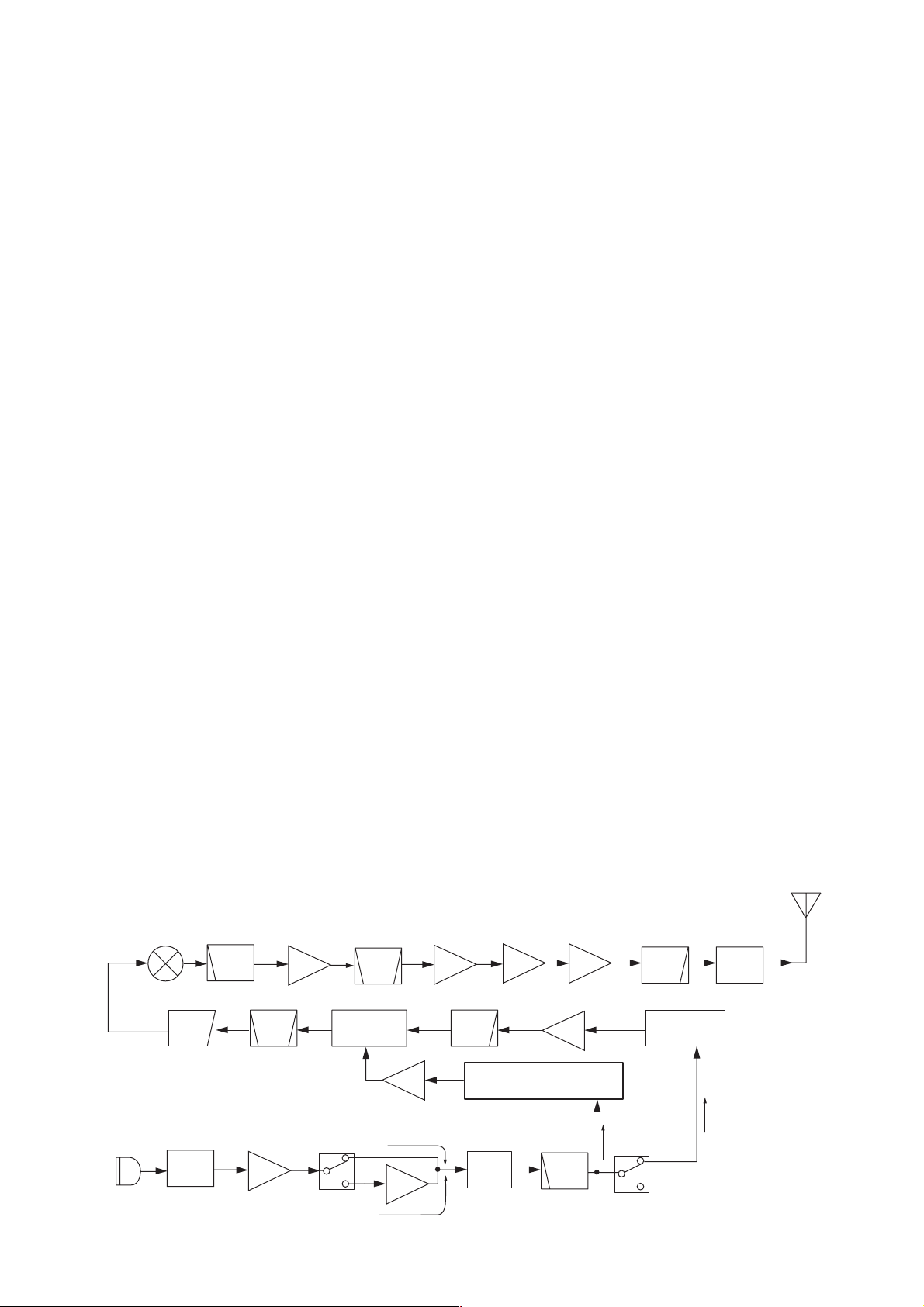

signals are applied to the CPU (IC50) via the FPGA IC

(IC200).

• DV MODE (VOICE OPERATION)

The digital audio signals from the CPU (IC50) are applied

to the AMBE CODEC IC (IC2) for code expansion, and are

then applied to the linear CODEC IC (IC1). The digital audio

signals are converted into analog audio signals at the D/A

converter section and then output from pin 34 (IC1)

The analog audio signals are applied to the mode switch

(MAIN unit; IC1411, pins 1, 7) via the J101 (pin 30) as “DAF”

signal.

• DD MODE/DV MODE (LOW SPEED DATA OPERATION)

While operating in DD mode, the output signals from

the CPU (IC50) are applied to the connected PC via the

Ethernet controller (IC104).

While operating in DV mode (low speed data operation), the

output signals from the CPU (IC50) are applied to the con-

nected PC via the USB controller (IC550).

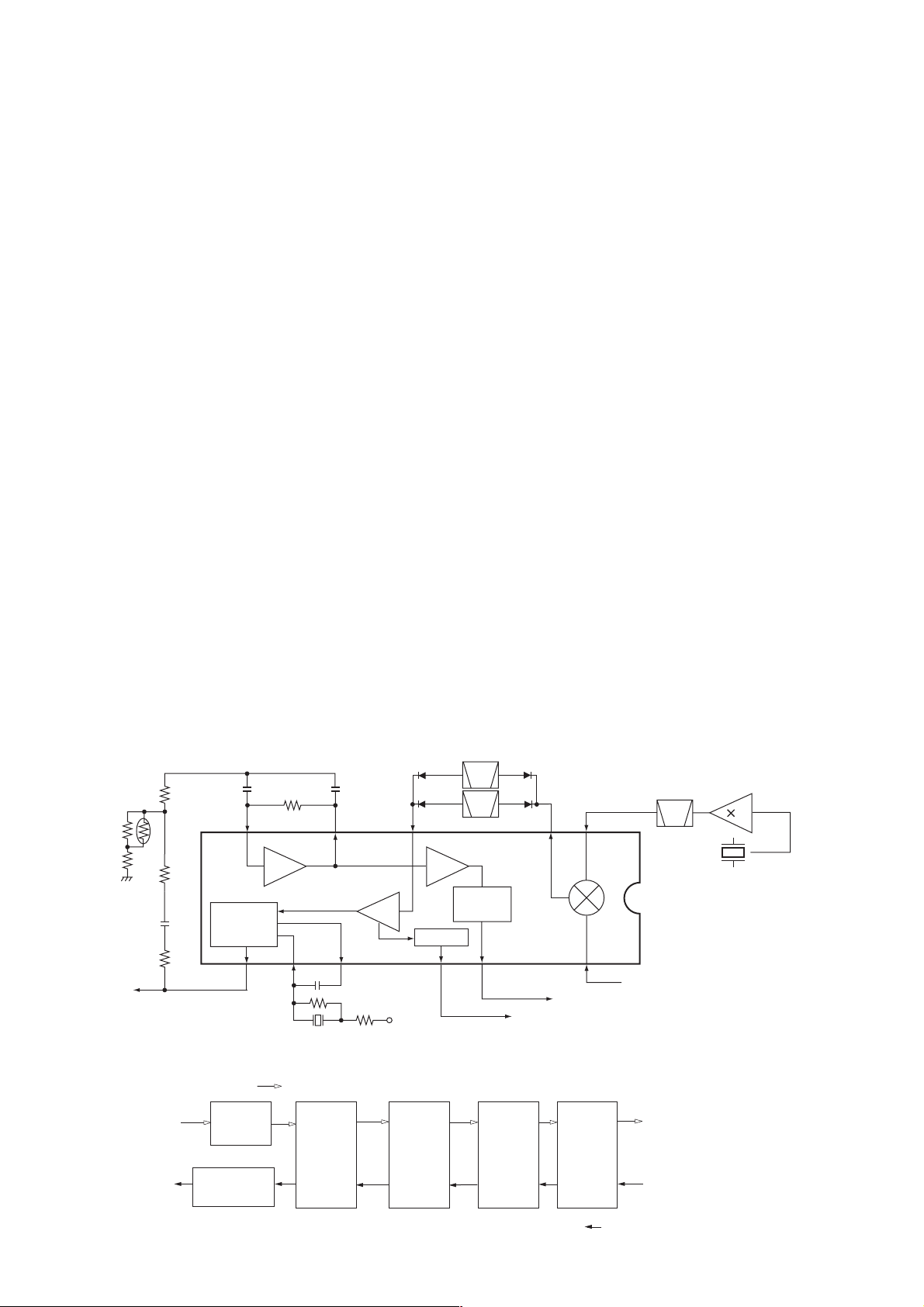

4-1-7 AF AMPLIFIER CIRCUIT (MAIN UNIT)

The AF amplifier circuit amplifies the demodulated AF sig-

nals to a level needed to drive a speaker.

• DV MODE

The AF signals from the LOGIC-1 unit are applied to the

mode switch (IC1411, pins 1, 7) and then amplified at the

buffer amplifier (IC1460, pins 1, 3). The buffer amplified

signals are applied to the filter switch (IC1462, pins 1, 6)

to select the appropriate AF filters for DV mode and then

passed through the low-pass (IC1461, pins 8, 10) and high-

pass (IC1461, pins 12, 14) filters. The filtered signals are

passed through the filter switch (IC1463, pins 1, 6) and are

then applied to the volume controller (IC1550, pins 2, 9).

• FM MODE

The AF signals from the demodulator IC (IC191, pin 9) are

applied to the mode switch (IC1411, pins 1, 6) and then

applied to the buffer amplifier (IC1460, pins, 1, 3). The buf-

fer amplified signals are applied to the filter switch (IC1462,

pins, 1, 7) to select the appropriate AF filters for FM mode

and then passed through the low-pass (IC1460, pins 6, 7,

8, 9) and high-pass (IC1460, pins 13, 14) filters. The filtered

signals are passed through the filter switch (IC1463, pins 1, 7)

and are then applied to the volume controller (IC1550, pins 2,

9).

The switched AF signals from the filter switch (IC1463, pin

1) are applied to the volume controller (IC1550, pins 2, 9).

The level adjusted AF signals (IC1550, pin 9) are applied to

the AF power amplifier (IC1551, pins 1, 4) via the AF mute

switch (Q1550).

The AF mute switch is mute the AF signals while digital

squelch, call sign squelch, noise squelch, tone squelch are

closed, the audio level is set to minimum position or trans-

mitting.

The power amplified AF signals from the AF power amplifier

(IC1551, pin 4) are applied to the speaker that is connected

to [SP] jack (J1550).

4-1-8 SQUELCH CIRCUITS (MAIN UNIT)

• DIGITAL CODE/CALL SIGN SQUELCH (DV MODE ONLY)

The digital code/call sign squelch circuit detects matched

digital code/call sign and opens the squelch only when

receiving a signal containing a matching digital code/call

sign. When digital code/call sign squelch is in use, and a sig-

nal with a unmatched digital code/call sign is received, the

digital code/call sign squelch circuit mutes the AF signals.

The detected digital audio signals from IC191 (pin 9) are

applied to the CPU (LOGIC-1 unit; IC50) via the mode

switch (IC342, pins 1, 7), GMSK MODEM IC (LOGIC-1 unit;

IC150) and FPGA IC (LOGIC-1 unit; IC200). Then the CPU

analyzes the digital code/call sign and output the AF mute

signal as “RMUT” from the pin 102 to the filter switch (IC1463,

pin 2) via the mute switch (LOGIC-1 unit; Q155).

• NOISE SQUELCH (FM MODE ONLY)

The noise squelch circuit cuts out AF signals when no RF

signals are received. By detecting noise components in

the AF signals, the squelch circuit switches the filter switch

(IC1463).

Portion of the AF signals from the demodulator IC (IC191,

pin 9) are applied to the active filter section in the demodu-

lator IC (IC191, pin 8). The active filter section filters and

amplifies noise components only. The amplified noise signals

are converted into the pulse-type signals at the noise detec-

tor section. The detected signals output from pin 14 (IC191).

The detected signals from the demodulator IC (IC191,

pin 14) are amplified at the noise amplifiers (Q192, Q193)

and then applied to the noise detector (D195). The detected

signals are applied to the CPU (LOGIC-1 unit; IC50, pin 32)

as "NOIS" signals. Then the CPU analyzes the noise condi-

tion and outputs the AF mute signal as “RMUT” from the pin

102 to the filter switch (IC1463, pin 2) via the mute switch

(LOGIC-1 unit; Q155).

• TONE SQUELCH (FM MODE ONLY)

The tone squelch circuit detects tone signals and opens the

squelch only when receiving a signal containing a matching

subaudible tone (CTCSS). When tone squelch is in use, and

a signal with a unmatched or no subaudible tone is received,

the tone squelch circuit mutes the AF signals even when

noise squelch is open.

A portion of “DEAF” signals from the buffer amplifier (IC1460,

pin 1) are applied to the low-pass filters (IC1461, pins 1, 2,

5, 7) to remove AF (voice) signals. The filtered signals are

applied to the CTCSS decoder in the CPU (LOGIC-1 unit,

IC50, pin 33) as “TONI” signals. Then the CPU analyzes

the decoded tone signals and output the AF mute signal as

“RMUT” from the pin 102 to the filter switch (IC1463, pin 2)

via the mute switch (LOGIC-1 unit; Q155).

4-1-9 S-METER CIRCUITS (MAIN UNIT)

Some of the amplified IF signal is applied to the S-meter

detector section in the demodulator IC (IC191) to be con-

verted into DC voltage. The output signal from the demodu-

lator IC (IC191, pin 12) is applied to the mode switch (IC341,

pins 10, 11) and then applied to the CPU (LOGIC-1 unit;

IC50). The CPU then outputs S-meter control signal to the

RC-24 or connected PC via the USB controller (LOGIC-1

unit; IC550).