IDT Tsi310TM User manual

®

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775

Printed in U.S.A.

©2009 Integrated Device Technology, Inc.

IDT

Tsi310™PCI-X®Bridge

User Manual

80B6020_MA001_05

September 2009

GENERAL DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance

and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitryembodied in an IDT product. The

Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

CODE DISCLAIMER

Code examples providedby IDT arefor illustrative purposes only and should not be relieduponfordeveloping applications. Any use of thecode examplesbelow is completely

at your own risk. IDT MAKES NOREPRESENTATIONSOR WARRANTIES OFANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY

OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICU-

LAR PURPOSE, ORNON-INFRINGEMENT.FURTHER,IDT MAKES NO REPRESENTATIONS OR WARRANTIESASTOTHE TRUTH,ACCURACYOR COMPLETENESS

OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR

THAT ISCONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR

SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code

examples also may be subject to UnitedStates export control lawsand maybe subject to theexportorimportlawsof other countries andit is your responsibility to comply with

any applicable laws or regulations.

LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in lifesupport devices or systemsunless a specific written agreement pertaining to

such intended use is executed between the manufacturer and an officer of IDT.

1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform,

when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is anycomponents of a life supportdevice or system whosefailure to performcanbe reasonably expected tocause the failure of thelife support device

or system, or to affect its safety or effectiveness.

IDT, the IDT logo, and Integrated Device Technology are trademarks or registered trademarks of Integrated Device Technology, Inc.

Tsi310 User Manual

80B6020_MA001_05

3

Contents

About this Document. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Document Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Related Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1. Functional Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.1 Overview of the Tsi310 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.2.1 PCI-X Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.2.2 Memory Buffer Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.2.3 Power Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.2.4 Transaction Forwarding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.2.5 Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.2.6 Optional Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.2.7 Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.2.8 IEEE®1149.1 JTAG Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.3 Operation Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.3.1 Supported Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.3.2 Buffer Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.3.3 Address Decoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.3.4 Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

1.4 Technology Highlights . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2. Bus Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.1 Overview of Bus Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.1.1 Types of Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.2 Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.2.1 Posted Write Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.2.2 Delayed/Split Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.2.3 Immediate Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.3 Read Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.3.1 Memory Read Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.3.2 I/O Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.3.3 Configuration Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Contents4

Tsi310 User Manual

80B6020_MA001_05

2.3.4 Non-Prefetchable and DWord Reads. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.3.5 Prefetchable Reads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

2.4 Configuration Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.4.1 Configuration Type 0 Access to Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

2.4.2 Type 1 to Type 0 Translation by Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.4.3 Type 1 to Type 1 Forwarding by Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.4.4 Special Cycle Generation by the Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3. Clocking and Reset Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

3.1 Clocking Domains. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.2 Clock Jitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.3 Mode and Clock Frequency Determination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.3.1 Primary Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

3.3.2 Secondary Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3.4 Clock Stability. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.5 Driver Impedance Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.6 Reset Functions and Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.6.1 Primary Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.6.2 Secondary Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.7 Bus Parking and Bus Width Determination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

3.8 Power Management and Hot-Plug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

3.9 Secondary Device Masking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.10 Handling of Address Phase Parity Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

3.11 Optional Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.12 Optional Configuration Register Access from the Secondary Bus. . . . . . . . . . . . . . . . . . . . . . . . 56

3.13 Short Term Caching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

4. Transaction Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

4.1 Overview of Transaction Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.2 General Ordering Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.3 Ordering Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

5. Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

5.1 Overview of Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.1.1 Terms and Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.1.2 Configuration Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.1.3 Type 1 PCI Configuration Space Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.2 Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Tsi310 User Manual

80B6020_MA001_05

Contents 5

5.3 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

5.4 PCI Configuration Space Header Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

5.4.1 Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

5.4.2 Device ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.4.3 Command Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

5.4.4 Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

5.4.5 Revision ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5.4.6 Class Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5.4.7 Cache Line Size Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.4.8 Latency Timer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.4.9 Header Type Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

5.4.10 BIST Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

5.4.11 Lower Memory Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

5.4.12 Upper Memory Base Address Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.4.13 Primary Bus Number Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.4.14 Secondary Bus Number Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

5.4.15 Subordinate Bus Number Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

5.4.16 Secondary Latency Timer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.4.17 I/O Base Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

5.4.18 I/O Limit Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.4.19 Secondary Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.4.20 Memory Base Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

5.4.21 Memory Limit Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.4.22 Prefetchable Memory Base Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.4.23 Prefetchable Memory Limit Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

5.4.24 Prefetchable Base Upper 32 Bits Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

5.4.25 Prefetchable Limit Upper 32 Bits Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

5.4.26 I/O Base Upper 16 Bits Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.4.27 I/O Limit Upper 16 Bits Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

5.4.28 Capabilities Pointer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

5.4.29 Reserved Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

5.4.30 Interrupt Line Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.4.31 Interrupt Pin Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.4.32 Bridge Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.5 Device-Specific Configuration Space Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

5.5.1 Primary Data Buffering Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Contents6

Tsi310 User Manual

80B6020_MA001_05

5.5.2 Secondary Data Buffering Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

5.5.3 Miscellaneous Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

5.5.4 Arbiter Mode Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

5.5.5 Arbiter Enable Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

5.5.6 Arbiter Priority Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

5.5.7 SERR# Disable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

5.5.8 Primary Retry Counter Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

5.5.9 Secondary Retry Counter Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

5.5.10 Discard Timer Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.5.11 Retry and Timer Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

5.5.12 Opaque Memory Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

5.5.13 Opaque Memory Base Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

5.5.14 Opaque Memory Limit Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

5.5.15 Opaque Memory Base Upper 32 Bits Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

5.5.16 Opaque Memory Limit Upper 32 Bits Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

5.5.17 PCI-X ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

5.5.18 Next Capabilities Pointer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

5.5.19 PCI-X Secondary Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

5.5.20 PCI-X Bridge Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

5.5.21 Secondary Bus Upstream Split Transaction Register . . . . . . . . . . . . . . . . . . . . . . . . . 140

5.5.22 Primary Bus Downstream Split Transaction Register. . . . . . . . . . . . . . . . . . . . . . . . . 141

5.5.23 Power Management ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

5.5.24 Next Capabilities Pointer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

5.5.25 Power Management Capabilities Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

5.5.26 Power Management Control/Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

5.5.27 PCI-to-PCI Bridge Support Extensions Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

5.5.28 Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

5.5.29 Secondary Bus Private Device Mask Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

5.5.30 Miscellaneous Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

6. Signals and Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

6.1 Overview of Signals and Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

6.2 Primary Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

6.3 Secondary Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

6.4 Strapping Pins and Other Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

6.5 Test Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

6.6 Power and Ground Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161

Tsi310 User Manual

80B6020_MA001_05

Contents 7

6.6.1 Filter Requirements for P_VDDA and S_VDDA. . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

6.7 Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

6.7.1 Pinout — Sorted by Signal Name. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

6.7.2 Pinout — Sorted by Grid Position . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

7. JTAG Boundary Scan. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

7.1 Overview of JTAG Boundary Scan . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

7.2 TAP Controller Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

7.3 JTAG Design Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

7.3.1 Including the Tsi310 in a JTAG Scan Ring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

7.3.2 Excluding the Tsi310 from a JTAG Scan Ring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

7.4 Instruction Register and Codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7.5 Bypass Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7.6 JTAG Device ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

7.7 Boundary Scan Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

7.7.1 Boundary Scan Register Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

8. Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

8.1 PCI/PCI-X Specification Conformance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

8.2 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

8.3 Recommended DC Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

8.4 AC Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

8.5 Power Dissipation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

9. Package Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

9.1 Package Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

9.2 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

A. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

A.1 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Contents8

Tsi310 User Manual

80B6020_MA001_05

Tsi310 User Manual

80B6020_MA001_05

9

List of Figures

Figure 1: Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 2: Configuration Transaction Address Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 3: Programmable Pull-up Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 4: De-assertion of S_RST# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 5: Filter Requirements for P_VDDA and S_VDDA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Figure 6: Inductor L1 Impedance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Figure 7: Pinout — Viewed from Above (Looking Through the Device) . . . . . . . . . . . . . . . . . . . . . . . . . 163

Figure 8: Package Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

List of Figures10

Tsi310 User Manual

80B6020_MA001_05

Tsi310 User Manual

80B6020_MA001_05

11

List of Tables

Table 1: PCI Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 2: PCI-X Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 3: Write Transaction Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 4: Read Transaction Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 5: IDSEL Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 6: Driver Impedance Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 7: Delay Times for De-assertion of S_RST#. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 8: Tsi310 Ordering Rules — PCI-X Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 9: Tsi310 Ordering Rules — PCI Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 10: Register Terms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 11: Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 12: Register Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 13: Primary Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Table 14: Secondary Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Table 15: Strapping Pins and Other Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Table 16: Test Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Table 17: Power and Ground Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Table 18: Inductor L1 Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Table 19: Signal Pin Listing by Signal Name . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Table 20: Signal Pin Listing by Grid Position. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Table 21: JTAG Logic Instruction Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 22: Boundary Scan Register Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Table 23: Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Table 24: Recommended DC Operating Conditions (TA= 0 to 70°C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

Table 25: AC Operating Conditions (TA= 0 to 70°C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

Table 26: Tsi310 Power Dissipation (Total = I/O + Core) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Table 27: Package Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Table 28: Package Thermal Resistance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Table 29: Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

List of Tables12

Tsi310 User Manual

80B6020_MA001_05

13

Tsi310 User Manual

80B6020_MA001_05

About this Document

This chapter discusses general document information about the Tsi310 PCI-X Bus Bridge User

Manual. The following topics are described:

•“Revision History” on page 13

•“Document Conventions” on page 14

•“Related Information” on page 17

Revision History

80B6020_MA001_05, Formal, September 2009

This version of the document was rebranded as IDT. It does not include any technical changes.

80B6020_MA001_04, Formal, December 2004

This document was updated to address the following changes:

• Added maximum rating information for VIN (Input voltage) (see Section 8.2 on page 192)

• Revised VIL (Maximum) and VIH (Minimum) numbers for Recommended DC operating

conditions (see Section 8.3 on page 193)

• Added power dissipation numbers (see Section 8.5 on page 194)

• Added part ordering information for Pb-free Tsi310 (see Section A on page 201)

80B6020_MA001_03, Formal, June 2004

This document was updated to incorporate a non-technical change.

80B6020_MA001_02, Formal, March 2004

This document was updated to incorporate several non-technical changes.

14

Tsi310 User Manual

80B6020_MA001_05

80B6020_MA001_01, Formal, February 2004

This document supports the Tsi310 (part numbers Tsi310A-133CE and Tsi310-133CE). For

information about the differences between these devices, see the Tsi310 Differences Document.

This document differs from the 80B6000_MA001_03 user manual in the following ways:

• Updated the Revision ID number (see Section 5.4.5 on page 77)

• Revised the explanation of the Secondary Retry Counter Register (see Section 5.5.9 on

page 123)

• Added a note about the P_CFG_BUSY signal (see Table 15 on page 157)

• Revised the reset value for the JTAG Device ID register (see Section 7.6 on page 174)

• Added a caution note in the Hot plug section about powering up Tsi310’s I/O pads (see

Section 3.8 on page 54)

• Revised the 1111 PCI command code row in Table 1 on page 28

• Added a new bullet in the section describing PCI commands not supported by the Tsi310

(see Section 2.1.1 on page 28)

• Added more information about PCI-to-PCI transactions (see Section 2.2.1.3 on page 31)

Document Conventions

This section explains the document conventions used in this manual.

Signal Notation

Signals are either active high or active low. Active low signals are defined as true (asserted)

when they are at a logic low. Similarly, active high signals are defined as true at a logic high.

Signals are considered asserted when active and negated when inactive, irrespective of voltage

levels. For voltage levels, the use of 0 indicates a low voltage while a 1 indicates a high voltage.

Signals that assume a logic low state when asserted are followed by a number sign as the last

non-numerical character “#” (for example, SIGNAL#). Signals that assume a logic high state

are not followed by an underscore character (for example, SIGNAL).

15

Tsi310 User Manual

80B6020_MA001_05

Bit Ordering Notation

When referring to PCI-X transactions, this document assumes the most significant bit is the

largest number (also known as little-endian bit ordering). For example, the PCI address/data bus

consists of AD[31:0], where AD[31] is the most significant bit and AD[0] is the least-significant

bit of the field (see the following graphic).

Object Size Notation

The following object size conventions are used for PCI/X transactions:

•Abyte is an 8-bit object.

•Aword is a 16-bit (2-byte) object.

•Adoubleword (Dword) is a 32-bit (4-byte) object.

•Aquadword is a 64-bit (8-byte) object.

Numeric Notation

The following numeric conventions are used:

• Hexadecimal values are in single quotation marks and are preceded by an x. For example:

x‘0B00’.

• Undefined hexadecimal values are indicated by a capital X. For example: x’X1’ =

undefined on reset.

• Binary values are spelled out (zero and one) or appear in single quotation marks and are

preceded by b. For example: b‘0101’.

Typographic Notation

The following italic typographic conventions are used in this manual:

• Book titles: For example, PCI Local Bus Specification (Revision 2.2).

• Important terms: For example, when a device is granted access to the PCI bus it is called

the bus master.

• Undefined values: For example, the device supports four channels depending on the setting

of the Axregister.

msb

lsb

313029282726252423222120191817161514131211109876543210

16

Tsi310 User Manual

80B6020_MA001_05

Units of Measure

The following units of measure are used in this manual:

• Prefixes: K=1024, k=1000

• Bits and bytes: An uppercase “B” stands for bytes. For example, 1 KB means 1024 bytes.

• A lowercase “b” refers to bits. For example, 1 Kb means 1024 bits.

Symbols Used

The following symbols are used in this manual:

Document Status Information

“Tsi” technical documentation is classified as either Advance, Preliminary, or Final:

• Advance: The Advance manual contains information that is subject to change and exists

until prototypes are available.

• Preliminary: The Preliminary manual contains information about a product that is near

production-ready, and is revised as required. The Preliminary manual exists until the

product is released to production.

• Formal: The Final manual contains information about a final, customer-ready product. This

type of manual can be downloaded from our website once the product is released to

production.

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or

damage to the device.

Tip

This symbol indicates a basic design concept or information considered helpful.

17

Tsi310 User Manual

80B6020_MA001_05

Related Information

The following information is useful for reference purposes when using this manual:

PCI Local Bus Specification

(Revision 2.2) This document defines the PCI hardware system including

the protocol, electrical, mechanical and configuration

specification for the PCI local bus components and

expansion boards. For more information, see

www.pcisig.com.

PCI-X Addendum to PCI Local

Bus Specification (Revision 1.0a) This document addresses the need for increased

bandwidth of PCI Devices. PCI-X enables the design of

systems and devices that can operate at speeds

significantly higher than today's specification allows. For

more information, see www.pcisig.com.

PCI-to-PCI Bridge Architecture

Specification (Revision 2.0) This document establishes the minimum behavioral

requirements that PCI-to-PCI bridges must meet to be

compliant to the PCI Local Bus Specification

(Revision 2.2). Recommendations and guidance on

optional PCI-to PCI bridge features are also provided by

this specification. For more information, see

www.pcisig.com.

PCI Bus Power Management

Interface Specification

(Revision 2.0)

This document defines power management capabilities

that enhance the base PCI architecture. For more

information, see www.pcisig.com.

18

Tsi310 User Manual

80B6020_MA001_05

19

Tsi310 User Manual

80B6020_MA001_05

1. Functional Overview

This chapter describes the main features and functions of the Tsi310. The following topics are

discussed:

•“Overview of the Tsi310” on page 19

•“Features” on page 22

•“Technology Highlights” on page 26

•“Operation Overview” on page 24

1.1 Overview of the Tsi310

The Tsi310 transparently connects two electrically separate PCI-X bus domains, allowing

concurrent operations on both buses. This results in good utilization of the buses in various

system configurations and enables hierarchical expansion of I/O bus structures.

As described by the PCI-X architecture, the Tsi310 is capable of handling 64-bit data at a

maximum bus frequency of 133 MHz (depending upon the bus topology and load) and is

backward compatible with all 3.3V I/O conventional PCI interfaces.

The Tsi310 also provides extensive buffering and prefetching mechanisms for efficient transfer

of data through the device, facilitating multi-threaded operation and high system throughput.

1. Functional Overview20

Tsi310 User Manual

80B6020_MA001_05

Figure 1: Block Diagram

The Tsi310 is composed of the following major functional blocks (see Figure 1):

• The device has two PCI-X interfaces. Each interface handles the PCI/PCI-X protocol for its

respective bus and depending on the type of transaction, can act as either a bus master or a

bus slave. These interfaces transfer data and control information flowing to and from the

blocks shown in the middle of the diagram.

• Two phase-locked loops (PLLs), one for the primary clock domain and one for the

secondary clock domain. The PLL for each clock domain is used when that bus is running

in PCI-X mode; in PCI mode, the PLL is bypassed to allow the full frequency range as

defined by the bus architecture. The two bus clocks may be run synchronously or

asynchronously. A spread-spectrum clock input, within the architectural bounds, is

supported for either or both interfaces.

• One set of configuration registers, programmable either from the primary or secondary

interface. The first 64 bytes of this address space conform to the architectural format for

bridge devices, called Header Type 1. The remaining 192 bytes are device-specific

registers. Each register is fully defined in Section 5.1.2 on page 64.

Primary PCI/PCI-X Bus

Secondary PCI/PCI-X Bus

80B6000_BK001_02

JTAG Secondary

Bus Arbiter

Primary

Clock PLL Secondary

Clock PLL

PCI-X

Interface

Bus

Master

Bus

Slave

PCI-X

Interface

Configuration Registers

Clocking & Reset

Data/Control Unit

Queue

Compare

Logic

Read Queue

8 entries PW Queue

8 entries

Address

Decode

Control

Logic

Burst Read

Buffer

4 Kbytes

Posted Write

Buffer

1 Kbyte

Single Data

Phase Buffer

4 Bytes

Data/Control Unit

Queue

Compare

Logic

Read Queue

8 entries PW Queue

8 entries

Address

Decode

Control

Logic

Burst Read

Buffer

4 Kbytes

Posted Write

Buffer

1 Kbyte

Single Data

Phase Buffer

4 Bytes Bus

Slave

Bus

Master

Table of contents

Popular Network Hardware manuals by other brands

Motorola solutions

Motorola solutions DIMETRA Express Maintenance Guide

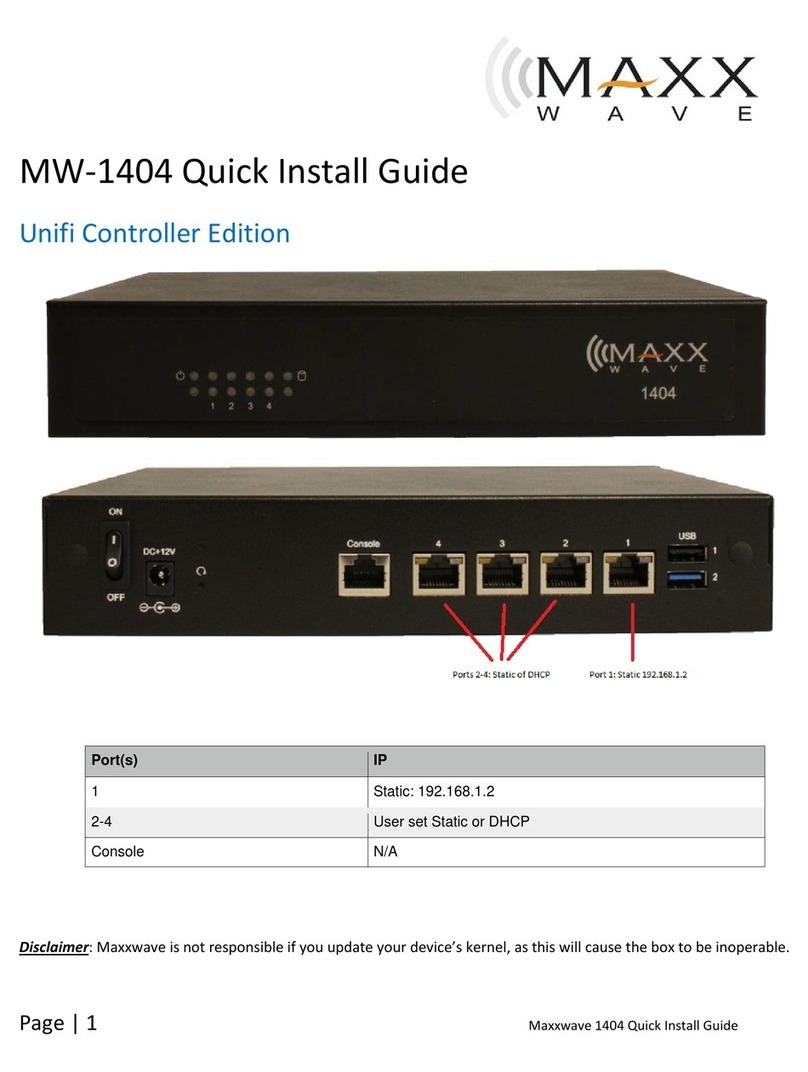

Maxx Wave

Maxx Wave MW-1404 Quick install guide

SunEyes

SunEyes Mini NVR Quick start manual

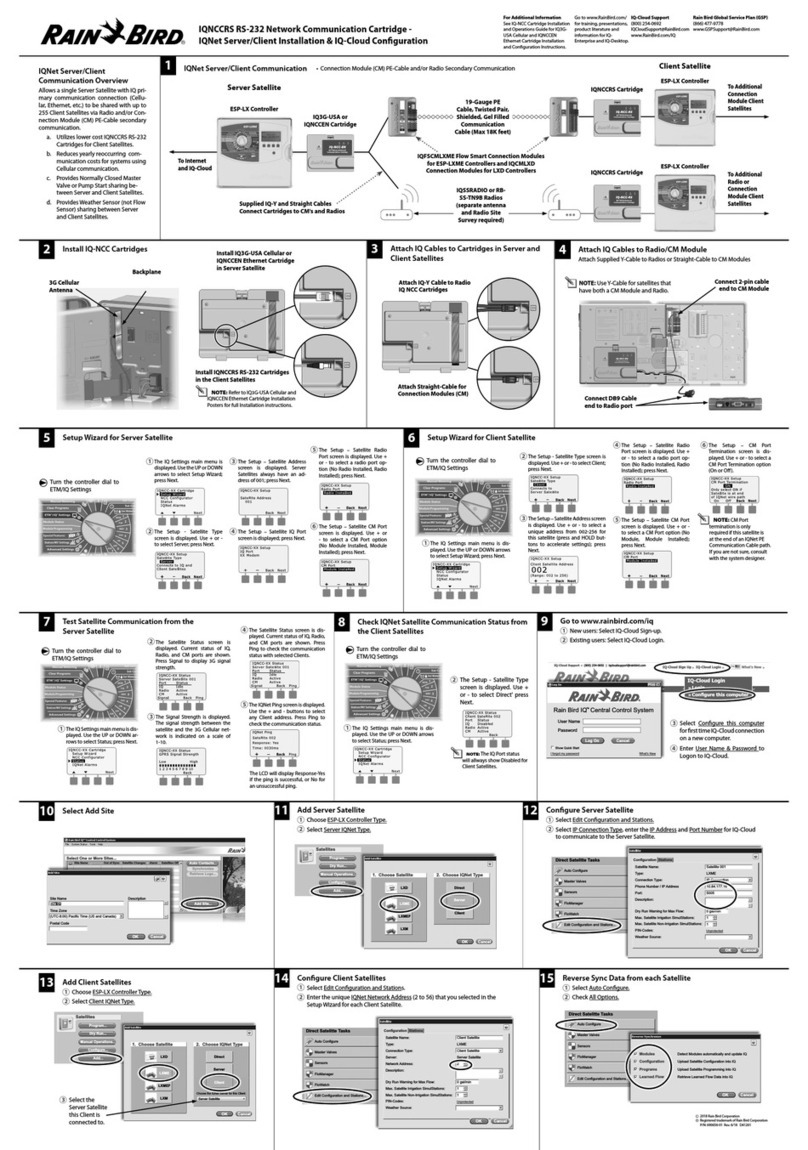

Rain Bird

Rain Bird IQNCCRS Installation and configuration

Symantec

Symantec S450 Series Safety and compliance guide

WatchNet

WatchNet ENS-08 POE Connection guide

Panasonic

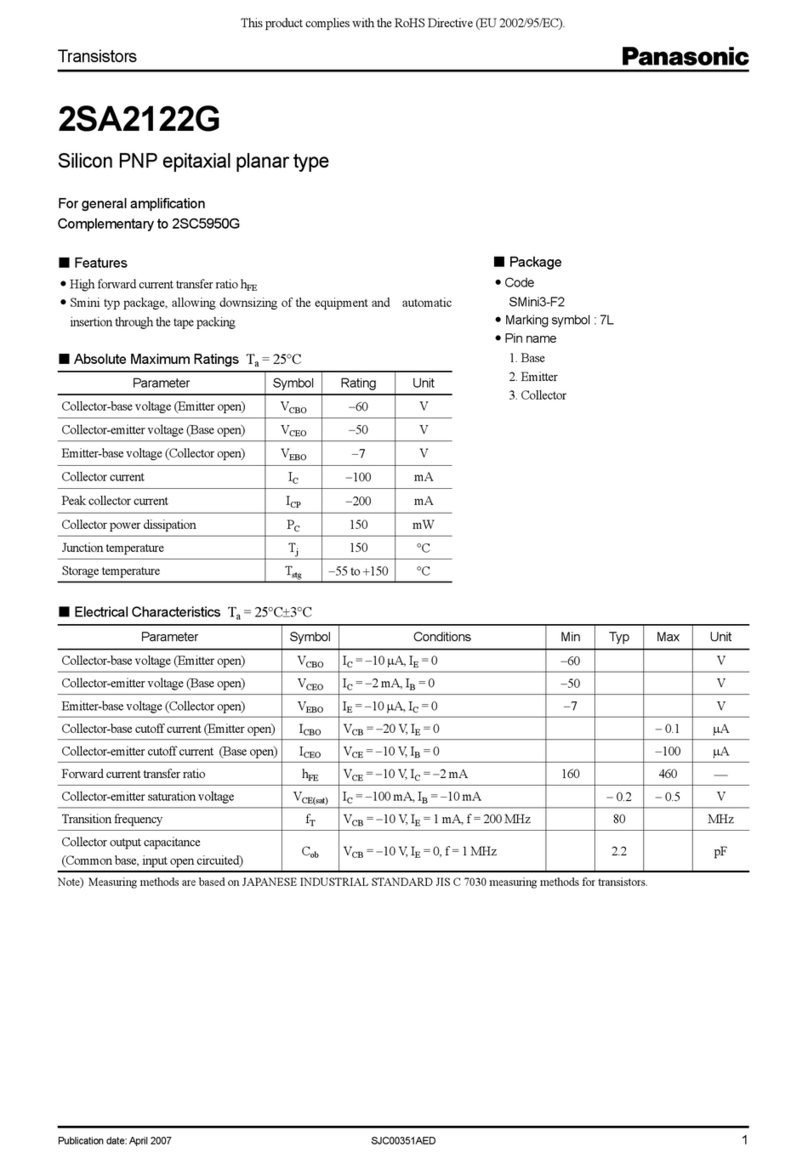

Panasonic Transistors 2SA2122G Specifications

Intel

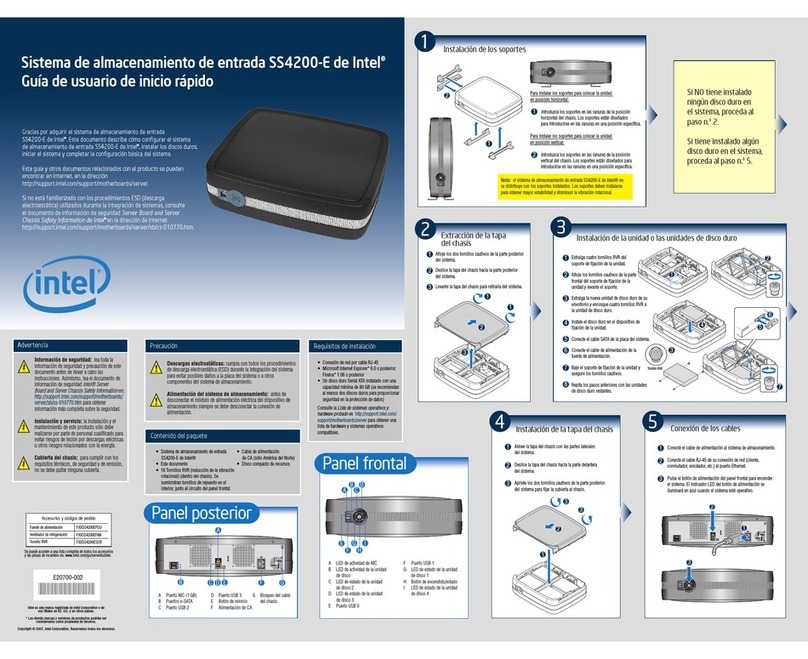

Intel SS4200-E - Entry Storage System NAS Server Guía de usuario de inicio rápido

ADTRAN

ADTRAN Smart 16e Shelf user manual

Cypress

Cypress S6SAE101A00SA1002 Operation manual

ASTRO

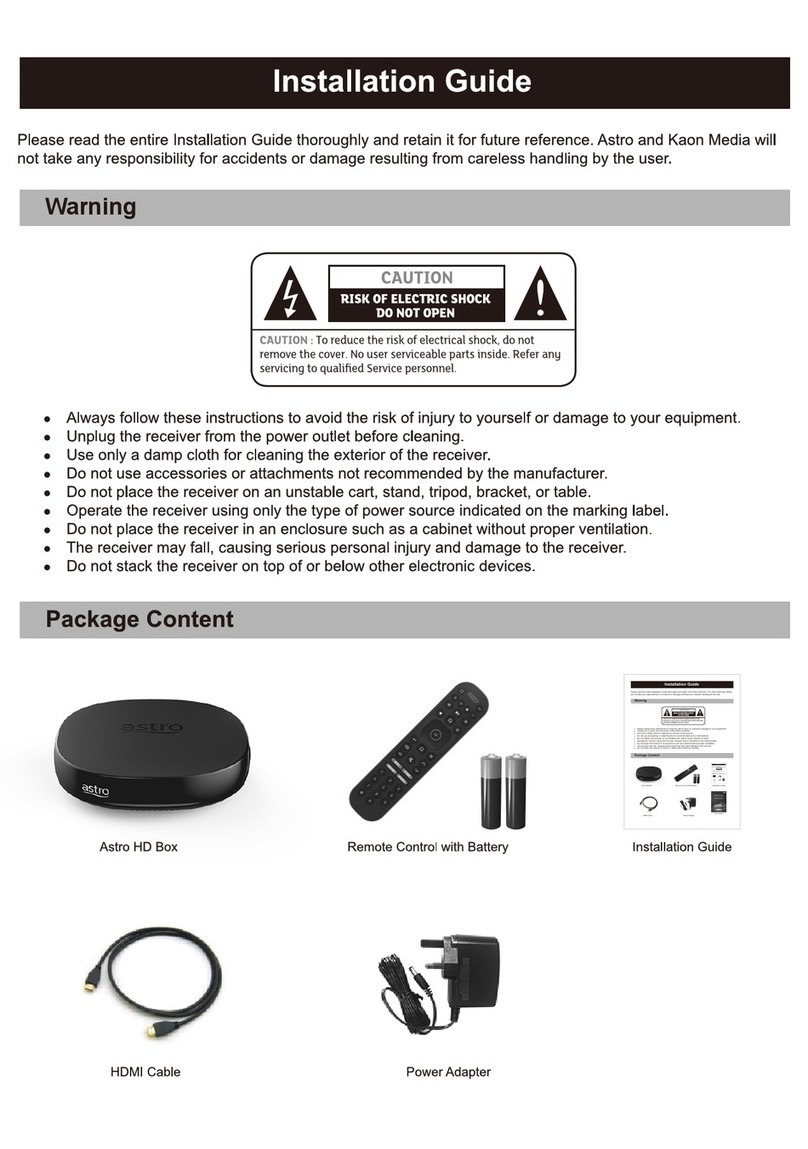

ASTRO Ulti Box installation guide

HP

HP Ethernet Network Interface Card hn230e quick start guide