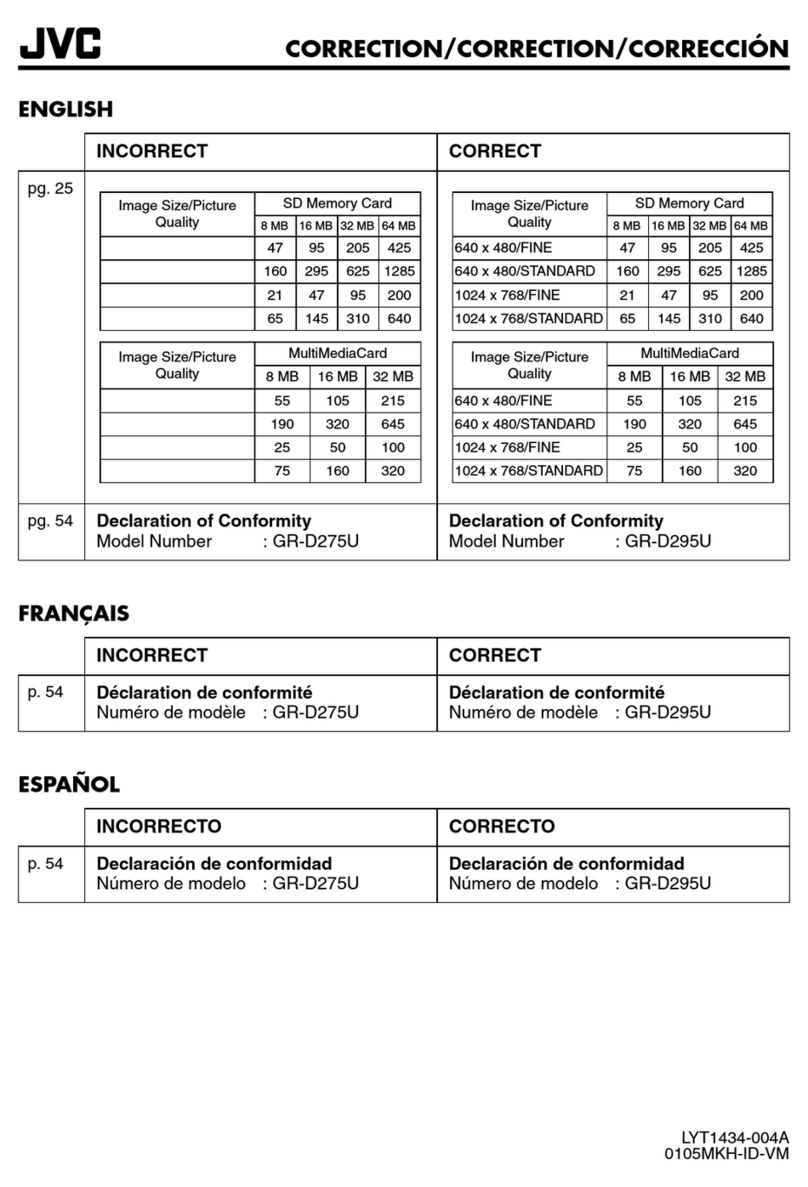

1-7

1-6

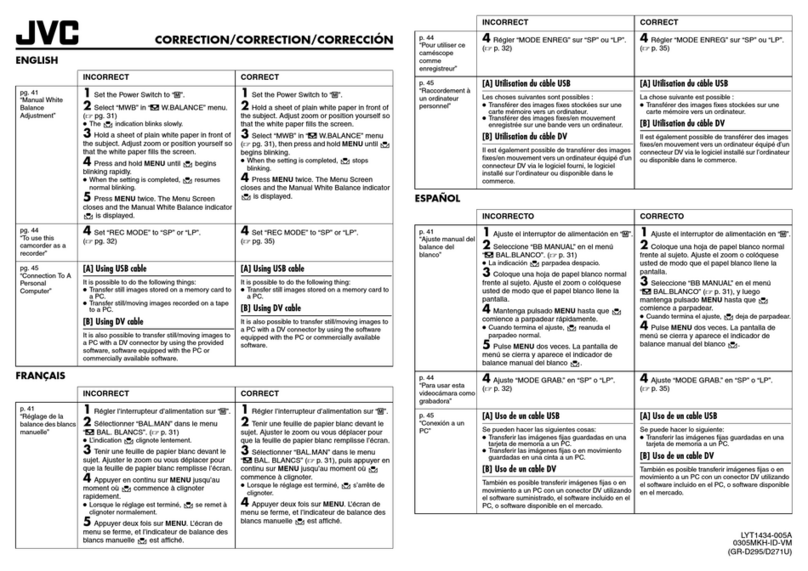

Pin Descriptions

Pin No. Pin Name Description I/O

Analog (A) or

Digital (D)

1 NC No internal connection - -

2 D0 Digital output terminal (LSB) O D

3-10 D1-D8 Digital output terminals O D

11 D9 Digital output terminal (MSB) O D

12 NC No internal connection - -

13 OADCLK Latch clock output terminal for D0 to D9 O D

14 DVSS Digital GND (0V) - D

15 DVDD Power for digital 3.0V system - D

(Should be connected to AVDD outside the IC.)

16 ADCLK Analog-to-digital conversion clock input terminal I D

17 OBP Optical black pulse input terminal I D

18 SPBLK Black level sampling clock input terminal I D

19 SPSIG Signal level sampling clock input terminal I D

20 PBLK Pre-blanking signal input terminal I D

21 OADSW OADCLK enable input terminal I D

22 AVSS Analog GND (0V) - A

23 AVDD Power for analog 3.0V system - A

24 NC No internal connection - -

25 CDSSW Signal level sampling output terminal O A

26 CDSIN CDS input terminal I A

27 ADCIN ADC input terminal I A

28 BLKSH Black level sample/hold terminal - A

29 BLKFB Black level feedback terminal - A

30 AVSS Analog GND (0V) - A

31 AVDD Power for analog 3.0V system - A

(Should be connected to DVDD outside the IC.)

32 VRT Reference voltage terminal 3 - A

(Ceramic capacitor of 0.1µF or more should be

connected between this terminal and AVss.)

33 VRB Reference voltage terminal 2 - A

(Ceramic capacitor of 0.1µF or more should be

connected between this terminal and AVss.)

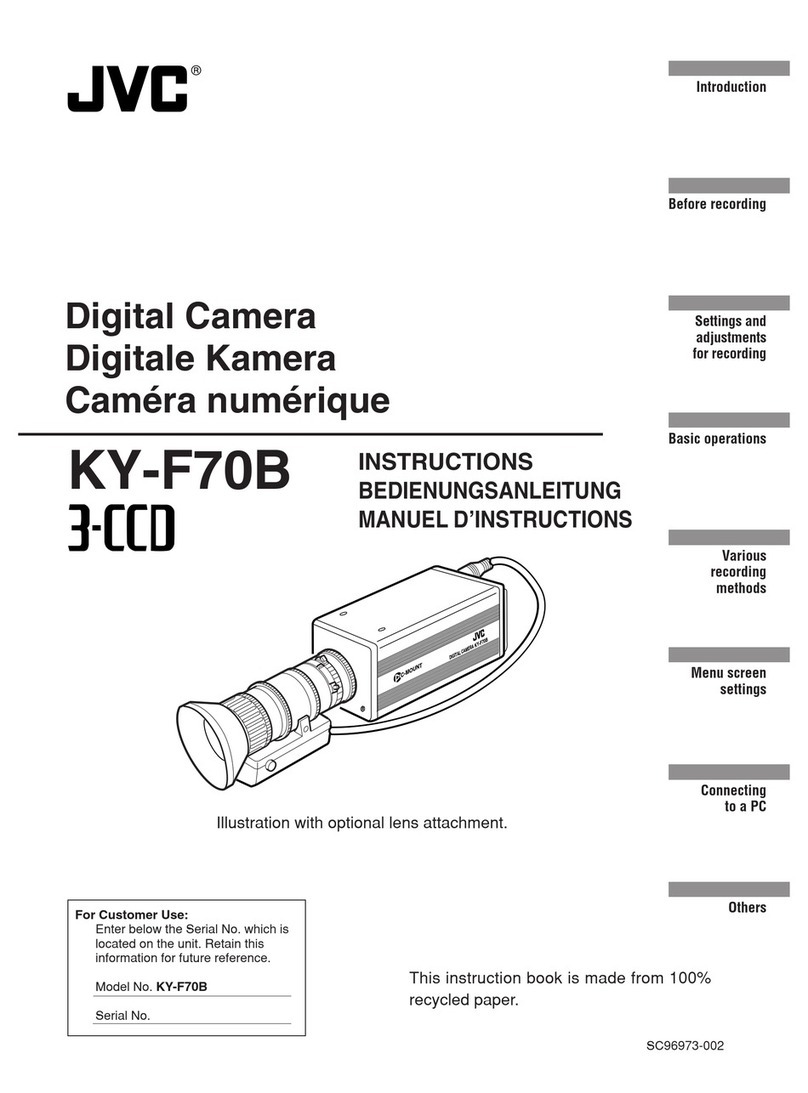

1.4 IC BLOCK DIAGRAM

1.4.1 IC 1002 (CXD2497R)

181716151098 21131214

28

27

26

25

30

3

31

32

33

6

2

37

48

34

45

38

42

47

40

46

44

39

43

41

5

4

24

23

22

20

19

35361297

11

PBLK

CLPDM

OBCLP

ADCLK

V

SS

5

ID

WEN

Pulse Generator

1/2

Selctor

Register

Selector

SSG

Latch

V Driver

OSCI

OSCO

CKI

CKO

MCKO

SNCSL

SSI

SCK

SEN

SSGSL

RST

TEST1

TEST2

V

DD

4

XSHP

XSHD

XRS

V

SS

4

V

DD

1

V

DD

5

HD

VD

V

SS

1

V

SS

5

V

DD

2

RG

V

SS

2

V

DD

3

H1

H2

V

SS

3

V1A

V1B

V2

V3A

V3B

V4

SUB

VH

VM

VL

Pin Descriptions

Pin No. Pin Name I/O Description

1VSS1 - GND

2 RST I System reset input terminal H: Reset released L: Reset

activated

(Should be activated at power ON, normally.)

(Schmitt trigger input/without protection diode on power

supply side)

3 SNCSL I Sync system switching control input terminal

(with pull-down resistor)

H: CKI sync L: MCKO sync

4 ID O Line identification pulse output terminal in the vertical

direction

5 WEN O Memory write timing pulse output terminal

6 SSGSL I Built-in SSG enable input terminal (with pull-down

resistor)

H: Built-in SSG is effective. L: External sync is effective.

7VDD1 - 3.3V power (for common logic section)

8VDD2 - 3.3V power (for RG terminal)

9 RG O Reset gate pulse output terminal for CCD

10 VSS2 - GND

11 VSS3 - GND

12 H1 O Clock output terminal for CCD horizontal register

13 H2 O Clock output terminal for CCD horizontal register

14 VDD3 - 3.3V to 5.0V power (for H1 and H2 terminals)

15 VDD4 - 3.3V power (for CDS system terminals)

16 XSHP O CCD pre-charge level sample/hold pulse output terminal

17 XSHD O CCD data level sample/hold pulse output terminal

18 XRS O Sample/hold pulse output terminal for phase matching in

analog-to-digital conversion

19 PBLK O Pulse output terminal for pulse cleaning during

horizontal and vertical blanking period

20 CLPDM O Pulse output terminal for CCD dummy signal clamping

21 VSS4 - GND

22 OBCLP O Pulse output terminal for CCD optical black signal

23 ADCLK O Clock output terminal for analog-to-digital conversion IC

Logical phase is adjustable with the serial interface data

24 VSS5 - GND

25 CKO O Inverter output terminal

26 CKI I Inverter input terminal

27 OSCO O Inverter output terminal for oscillation (If not used,

should be opened or connected to GND through a

capacitor.)

28 OSCI I Inverter input terminal for oscillation (If not used, should

be fixed to "Low".)

29 VDD5 - 3.3V power (for common logic section)

30 MCKO O System clock output terminal for signal processing IC

31 SSI I Serial interface data input terminal for setting each IC

mode (Schmitt trigger input/without protection diode on

power supply side)

32 SCK I Serial interface clock input terminal for setting each IC

mode (Schmitt trigger input/without protection diode on

power supply side)

33 SEN I Serial interface strobe input terminal for setting each IC

mode (Schmitt trigger input/without protection diode on

power supply side)

34 VD I/O Vertical sync signal input/output terminal

35 HD I/O Horizontal sync signal input/output terminal

36 VSS6 - GND

37 TEST1 I IC test terminal 1 with pull-down resistor (Should be

fixed to GND normally.)

38 VM - GND (for vertical drivers)

39 V2 O Clock output terminal for CCD vertical register

40 V4 O Clock output terminal for CCD vertical register

41 V1A O Clock output terminal for CCD vertical register

42 VH - 15.0V power (for vertical drivers)

43 V1B O Clock output terminal for CCD vertical register

44 V3A O Clock output terminal for CCD vertical register

45 VL - -7.5V power (for vertical drivers)

46 V3B O Clock output terminal for CCD vertical register

47 SUB O Pulse output terminal for CCD electronic shutter

48 TEST2 I IC test terminal 2 with pull-down resistor (Should be

fixed to GND normally.)

1.4.2 IC 2001 (CDS/AGL)

34 VRM Reference voltage terminal 1 - A

(Ceramic capacitor of 0.1µF or more should

be connected between this terminal and AVss.)

35 BIAS Internal bias terminal - A

(A 24-Kohm resistor should be connected

between this terminal and AVss.)

36 NC No internal connection - -

37 AVSS Analog GND (0V) - A

38 AVDD Power for analog 3.0V system - A

(Should be connected to DVDD outside the IC.)

39 NC No internal connection - -

40 AVSS Analog GND (0V) - A

41 AVDD Power for analog 3.0V system - A

(Should be connected to DVDD outside the IC.)

42 OEB Digital output enable control input terminal I D

43 CS Serial interface control input terminal I D

44 SCK Serial clock input terminal I D

45 SDATA Serial data input terminal I D

46 DVDD Power for digital 3.0V system - D

(Should be connected to AVDD outside the IC.)

47,48 DVSS Digital GND - D

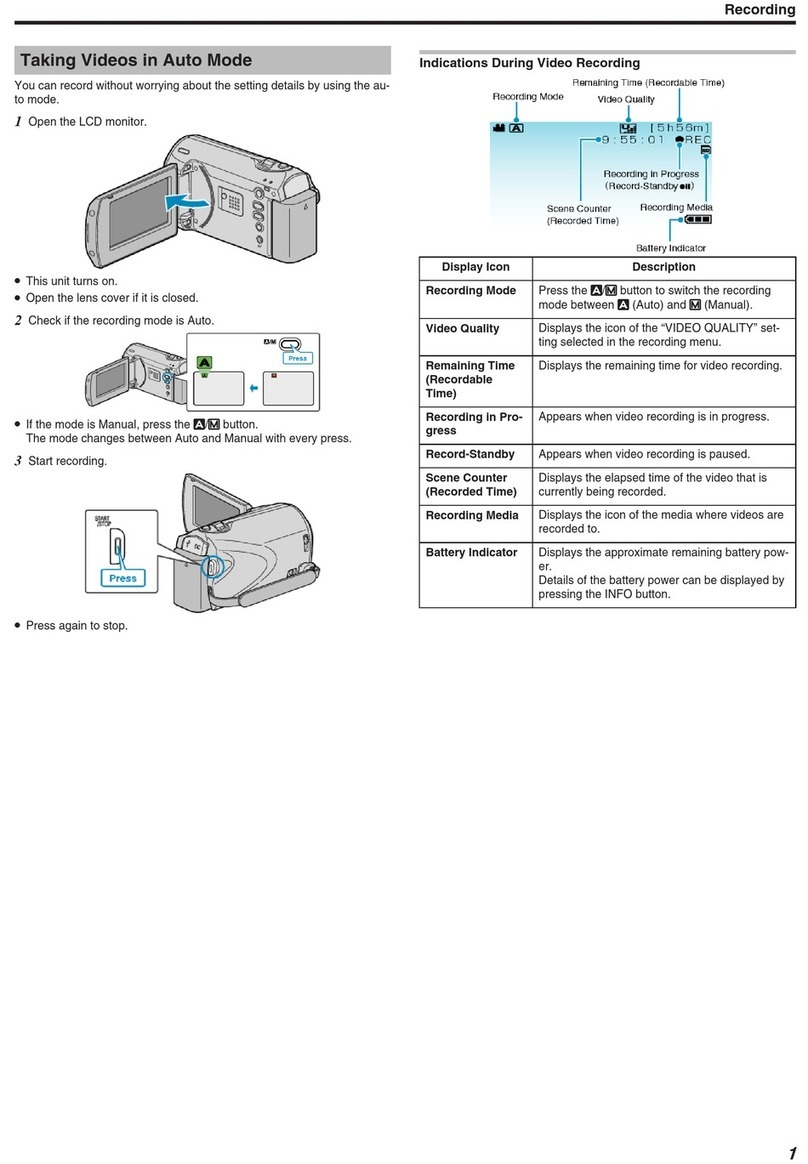

13 16 18 19

42 OEB

11 D9

10 D8

9D7

8D6

7D5

6D4

5D3

4D2

3D1

2

32

VRB

34

VRM

33

VRT

35

BIAS

43

CS

45

SDATA

44

SCK

17

29

OBP

20

PBLK

BLKFB

BLKSH

CDSIN

CDSSW

ADCIN

D0

26

25

27

21

OADSW

OADCLK

ADCLK

SPBLK

SPSIG

AVDD

DVDD

AVSS

DVSS

28 CDS PGA 10bit

ADC

Output

Latch

circuit

TIMING

gen

DC offset

compensatory Serial

Interface

Bias

Occurrence

41 46 40 48