8

LT1010

1010fc

APPLICATIO S I FOR ATIO

WUUU

without limiting. Because of this, it is capable of power

dissipation in excess of its continuous ratings.

Normally, thermal overload protection will limit dissipa-

tion and prevent damage. However, with more than 30V

across the conducting output transistor, thermal limiting

is not quick enough to ensure protection in current limit.

The thermal protection is effective with 40V across the

conducting output transistor as long as the load current is

otherwise limited to 150mA.

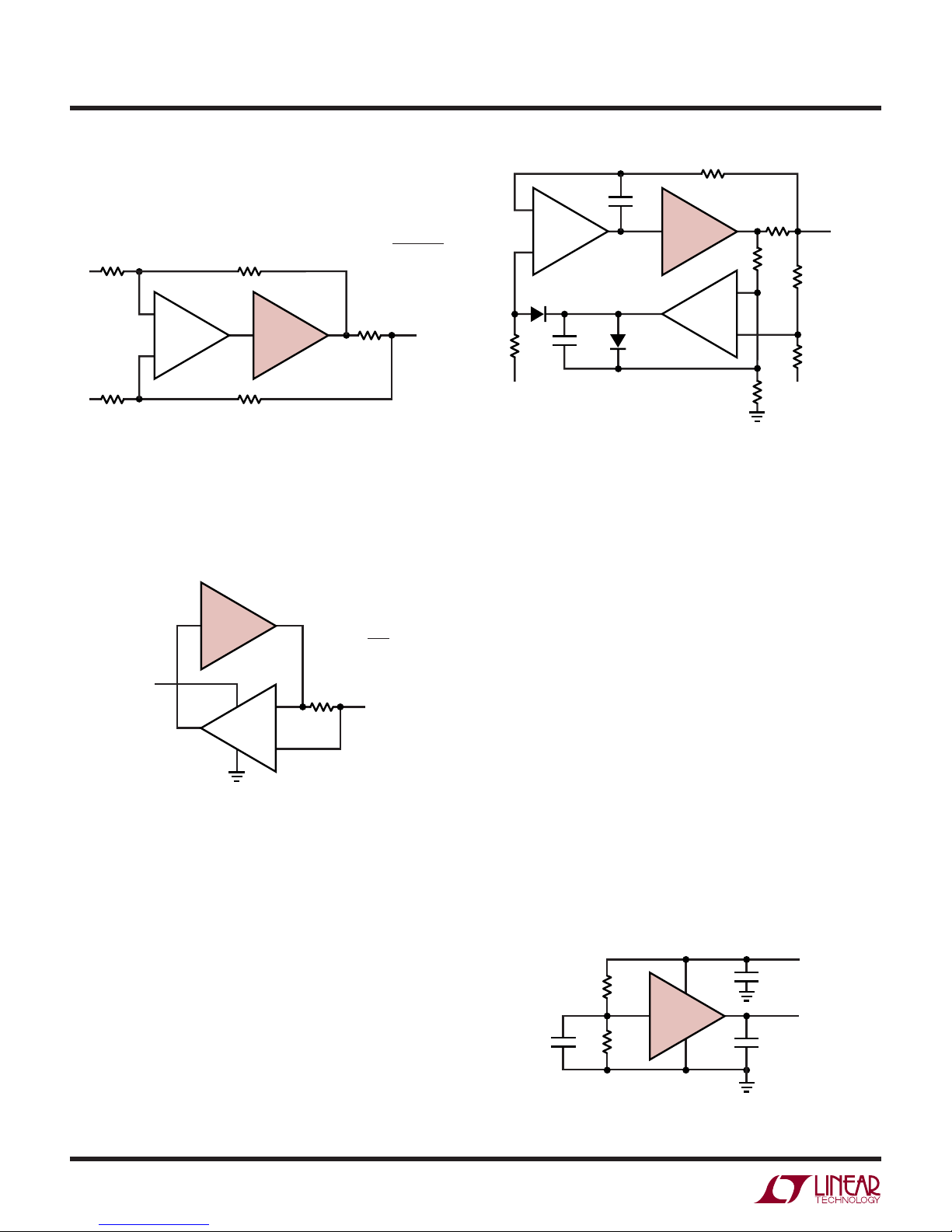

Drive Impedance

When driving capacitive loads, the LT1010 likes to be

driven from a low source impedance at high frequencies.

Certain low power op amps (e.g., the LM10) are marginal

in this respect. Some care may be required to avoid

oscillations, especially at low temperatures.

Bypassing the buffer input with more than 200pF will solve

the problem. Raising the operating current also works.

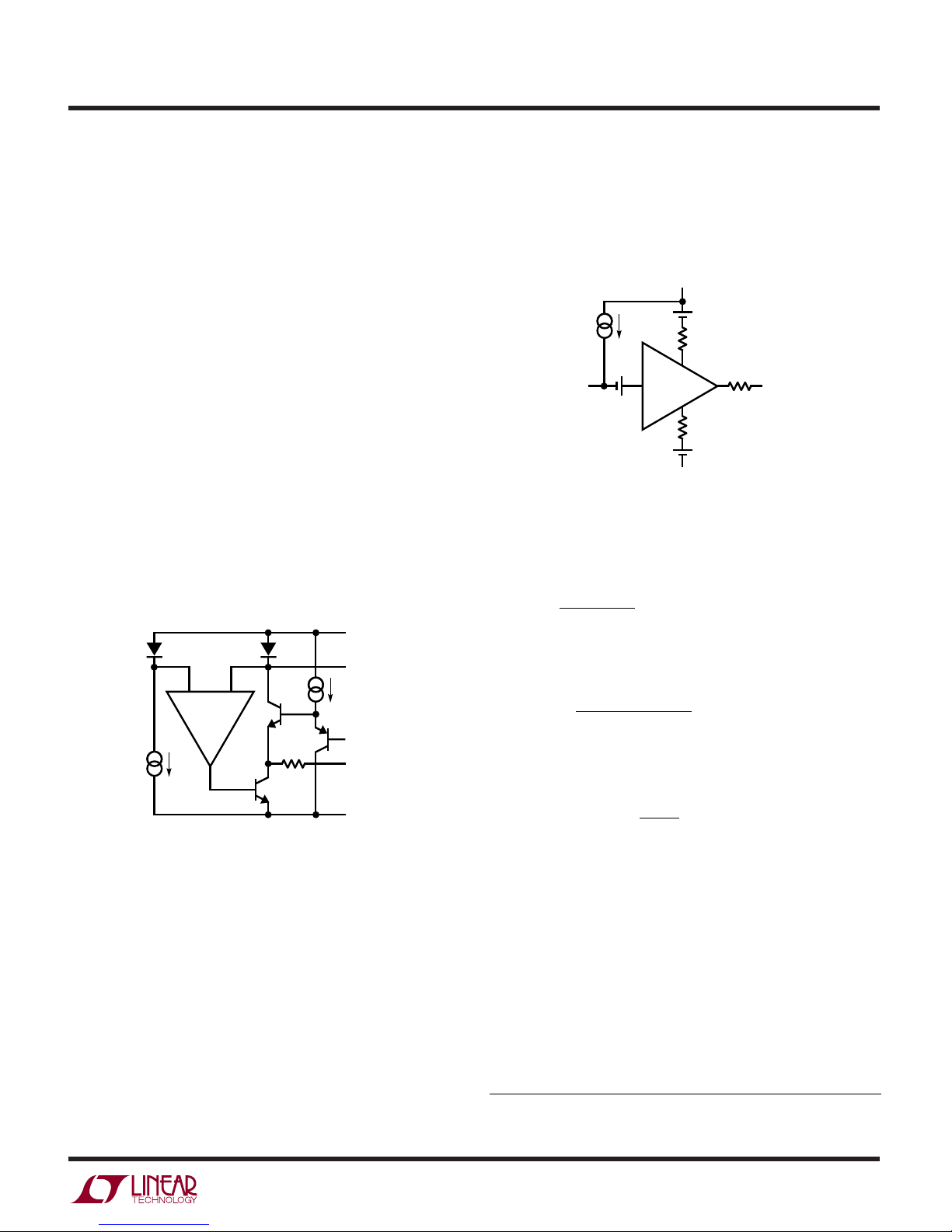

Parallel Operation

Parallel operation provides reduced output impedance,

more drive capability and increased frequency response

under load. Any number of buffers can be directly paral-

leled as long as the increased dissipation in individual

units caused by mismatches of output resistance and

offset voltage is taken into account.

When the inputs and outputs of two buffers are connected

together, a current, ∆I

OUT

, flows between the outputs:

∆=+

IVV

RR

OUT OS OS

OUT OUT

12

12

–

where V

OS

and R

OUT

are the offset voltage and output

resistance of the respective buffers.

Normally, the negative supply current of one unit will

increase and the other decrease, with the positive supply

current staying the same. The worst-case (V

IN

→V

+

)

increase in standby dissipation can be assumed to be

∆I

OUT

V

T

, where V

T

is the total supply voltage.

Offset voltage is specified worst case over a range of

supply voltages, input voltage and temperature. It would

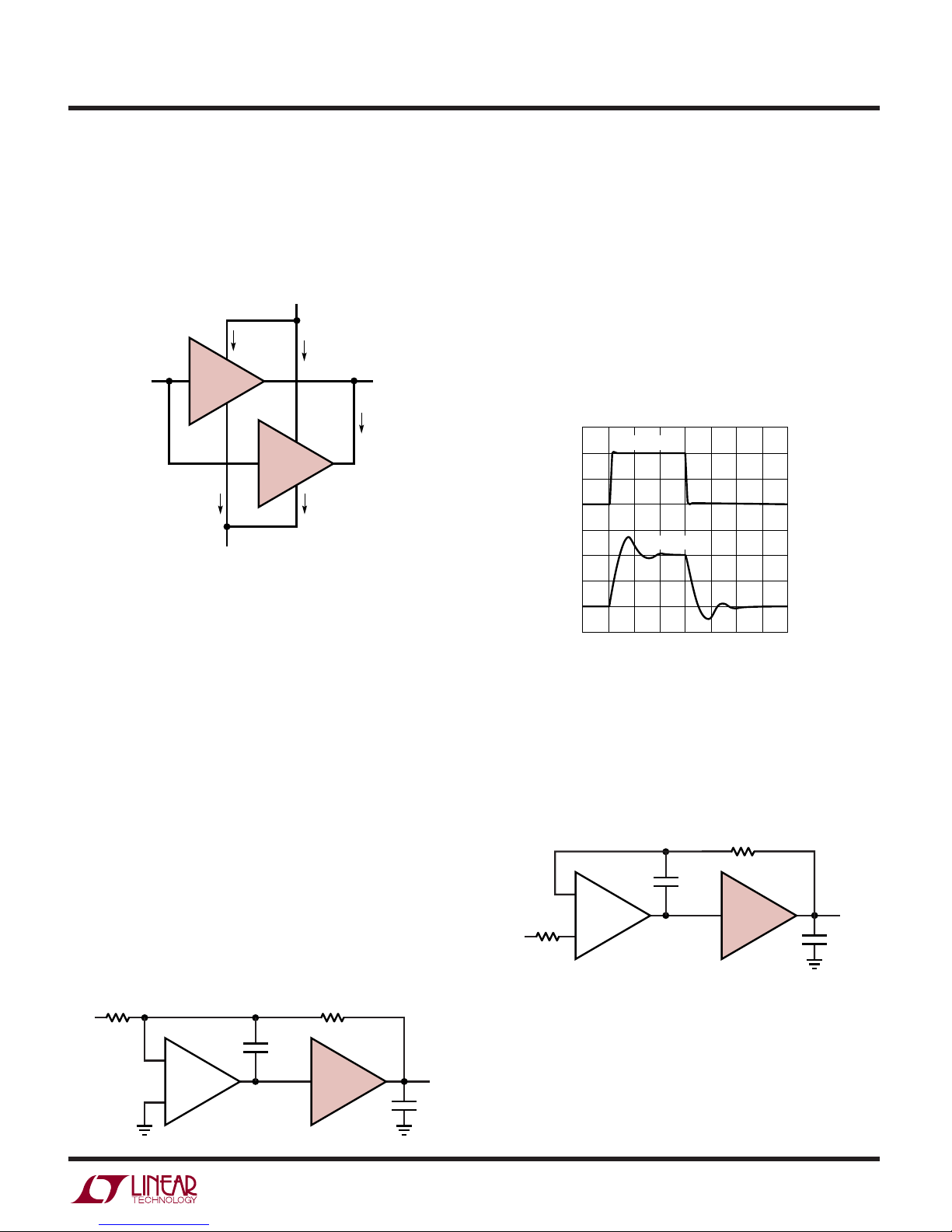

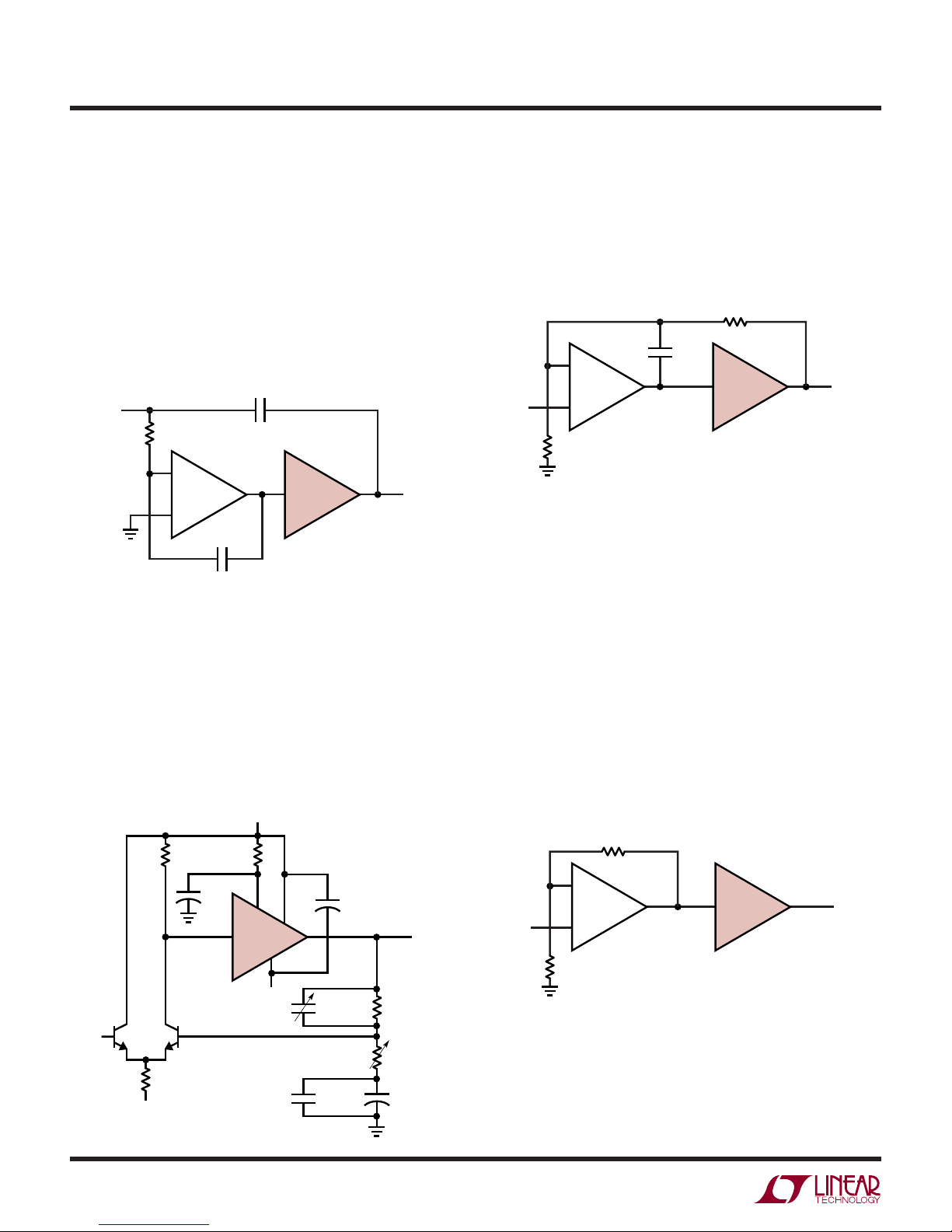

ground plane is prudent, especially when operating at high

frequencies.

The buffer slew rate can be reduced by inadequate supply

bypass. With output current changes much above

100mA/µs, using 10µF solid tantalum capacitors on both

supplies is good practice, although bypassing from the

positive to the negative supply may suffice.

When used in conjunction with an op amp and heavily

loaded (resistive or capacitive), the buffer can couple into

supply leads common to the op amp causing stability

problems with the overall loop and extended settling time.

Adequate bypassing can usually be provided by 10µF solid

tantalum capacitors. Alternately, smaller capacitors could

be used with decoupling resistors. Sometimes the op amp

has much better high frequency rejection on one supply,

so bypass requirements are less on this supply.

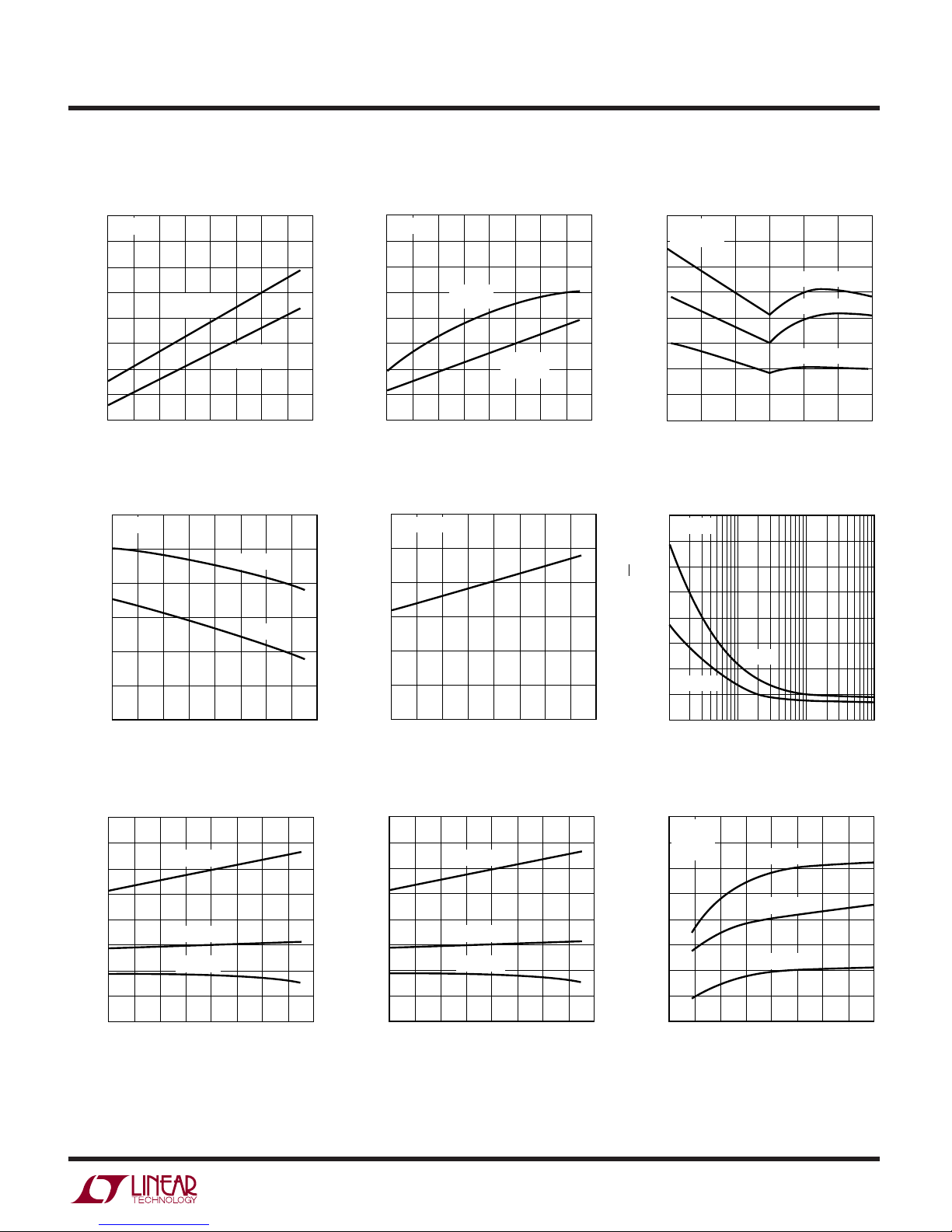

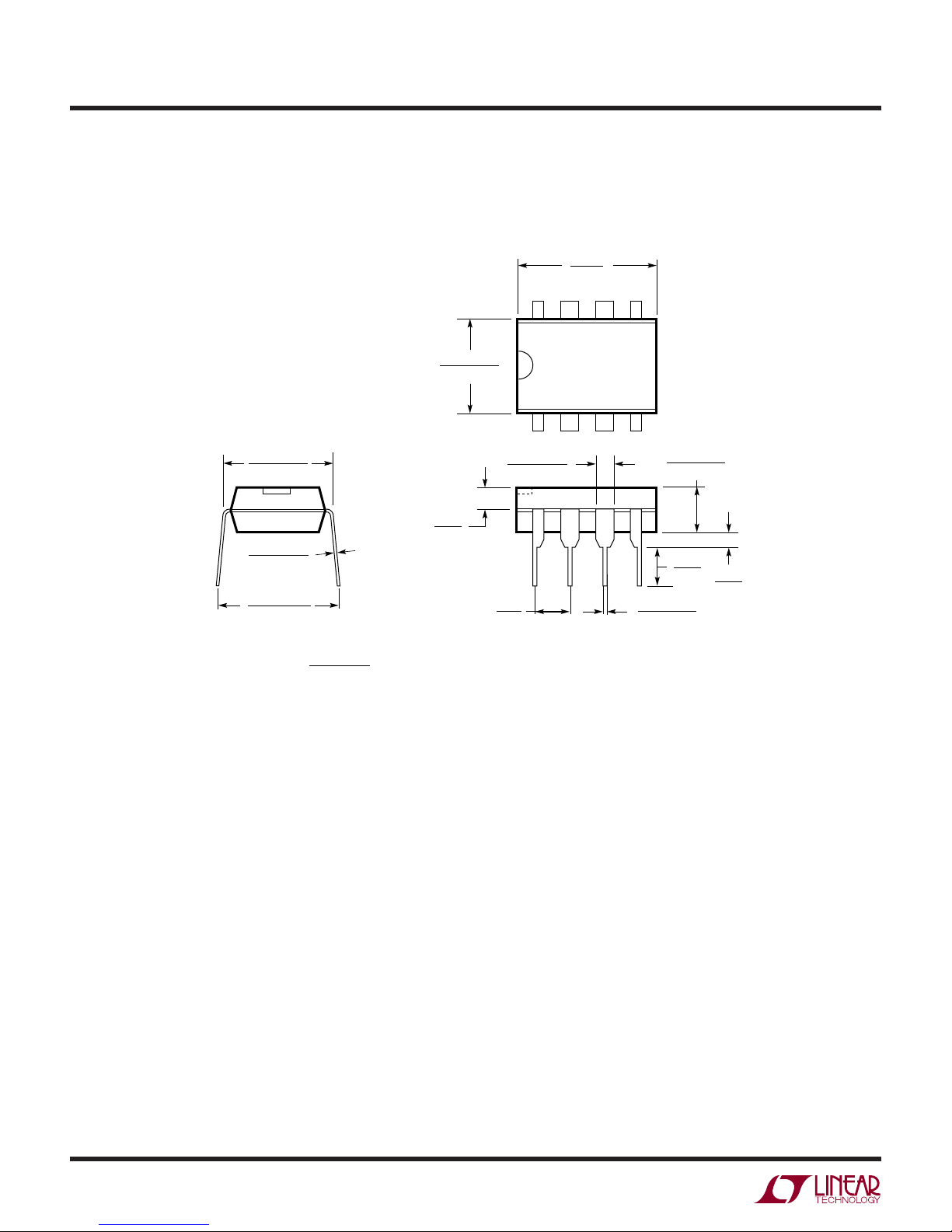

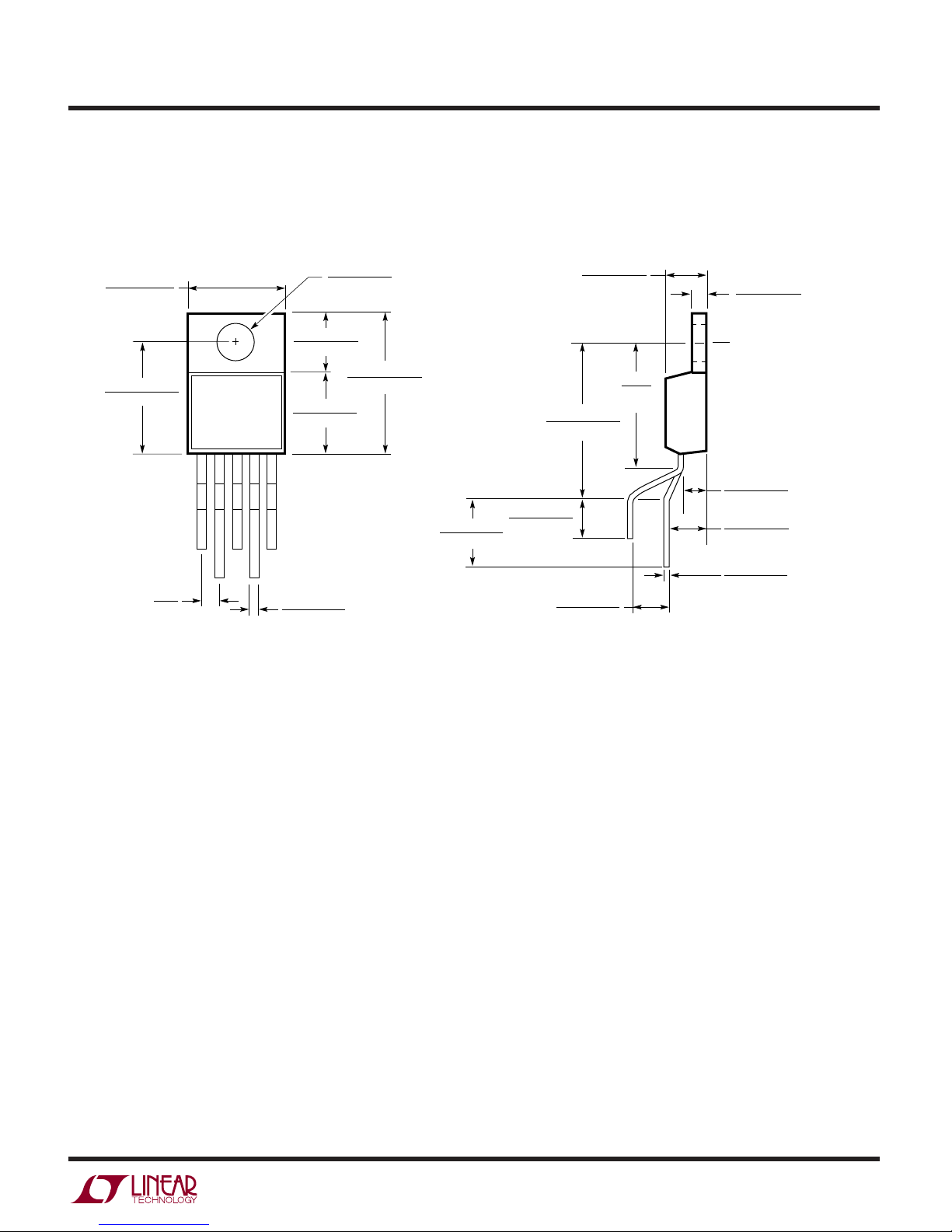

Power Dissipation

In many applications the LT1010 will require heat sink-

ing. Thermal resistance, junction to still air is 100°C/W

for the TO-220 package and 130°C/W for the miniDIP

package. Circulating air, a heat sink or mounting the

package to a printed circuit board will reduce thermal

resistance.

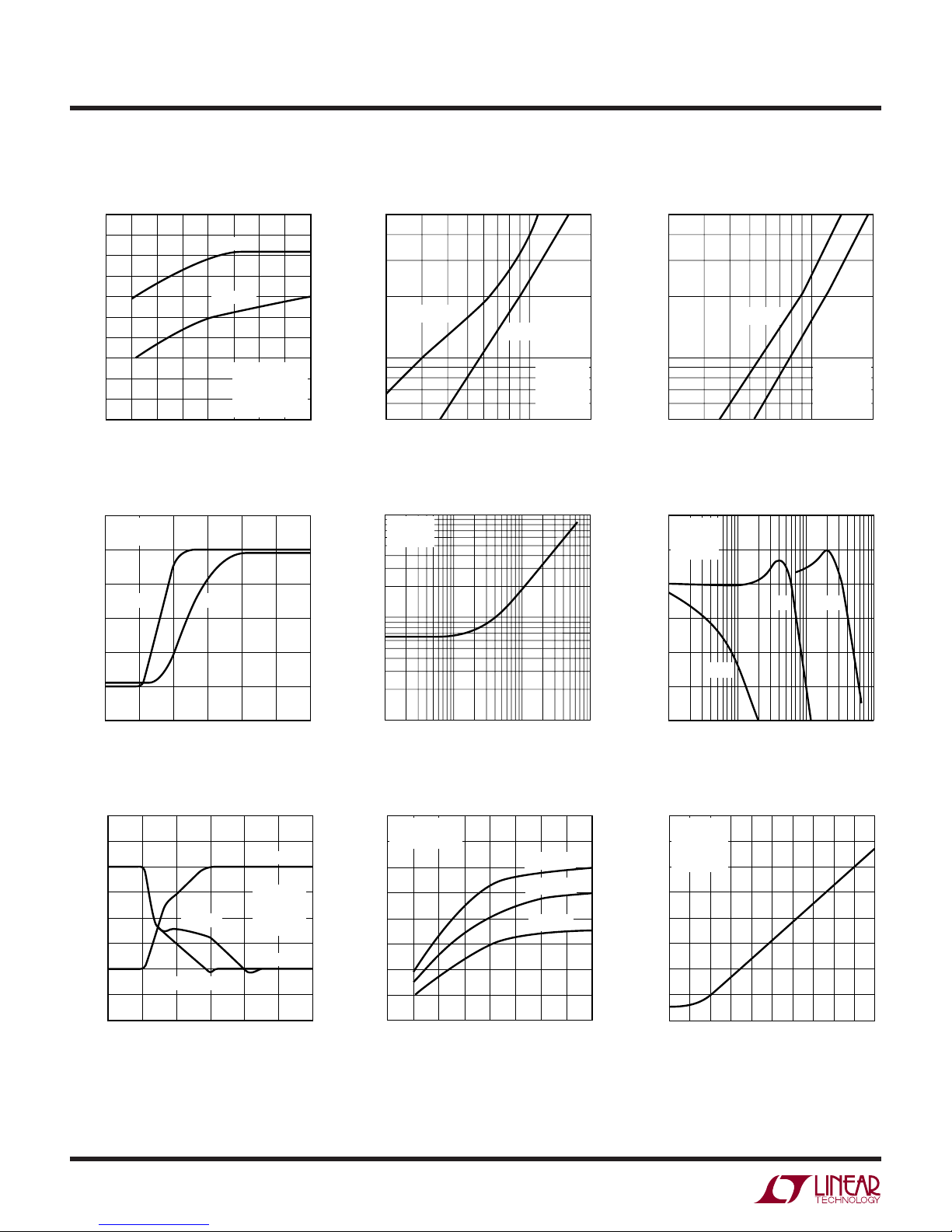

In DC circuits, buffer dissipation is easily computed. In AC

circuits, signal waveshape and the nature of the load

determine dissipation. Peak dissipation can be several

times average with reactive loads. It is particularly impor-

tant to determine dissipation when driving large load

capacitance.

With AC loading, power is divided between the two output

transistors. This reduces the effective thermal resistance,

junction to case to 15°C/W for the TO-220 package as long

as the peak rating of neither output transistor is exceeded.

The typical curves indicate the peak dissipation capabili-

ties of one output transistor.

Overload Protection

The LT1010 has both instantaneous current limit and

thermal overload protection. Foldback current limiting has

not been used, enabling the buffer to drive complex loads