MEDIATEK MT3620 Installation manual

© 2020 MediaTek Inc.

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

Specifications are subject to change without notice.

Version: v2.0

Release Date: 2019-02-19

MediaTek MT3620

Secure Wireless Connectivity Chip

Hardware User Guide

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 2 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

1 Document Revision History

Version

Date

Change List

V2.0

2020/02/19

1st public release.

Me

dia

Tek

Co

nfi

den

tial

A

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 3 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

2 Contents

1Document Revision History .................................................................................... 2

2Contents.................................................................................................................. 3

3List of Tables ........................................................................................................... 5

4List of Figures ......................................................................................................... 6

5System overview ..................................................................................................... 7

5.1 General Description ..................................................................................................................7

5.2 Block Diagram .......................................................................................................................... 8

6PCB Stack Up and Impedance Control .................................................................... 9

6.1 PCB Stack-up.............................................................................................................................9

6.2 Transmission Line...................................................................................................................10

6.2.1 50ΩSingle-ended...................................................................................................10

6.2.2 50ΩDifferential-ended..........................................................................................10

6.3 Package Information............................................................................................................... 11

6.4 Top Marking ............................................................................................................................ 12

7RF Front-End Circuit Design..................................................................................13

7.1 RF System Overview ............................................................................................................... 13

7.2 Wi-Fi RF Main Path Schematic.............................................................................................. 13

7.3 Wi-Fi RF Auxiliary Path Front-End Schematic..................................................................... 14

7.4 RF Component Placement ...................................................................................................... 15

7.4.1 RF matching circuit placement ............................................................................. 15

7.4.2 RF Power circuit placement .................................................................................. 16

7.5 Diversity...................................................................................................................................18

7.5.1 Receive diversity is supported in hardware..........................................................18

7.5.2 Full transmit/receive diversity is supported in software but requires an external

DPTP switch ...........................................................................................................18

7.5.3 Antenna Placement Guidelines for Antenna Diversity ........................................ 19

7.6 RF Layout Checklist ............................................................................................................... 20

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 4 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

8Power Rails ............................................................................................................21

8.1 MT3620 PMU Architecture .................................................................................................... 21

8.2 MT3620 Power Plan ...............................................................................................................22

8.2.1 PMU Buck 3.3V Supply Input ...............................................................................22

8.2.2 PMU Buck 1.6V Supply Output ............................................................................ 24

8.2.3 PMU LDO 2.5V Supply Output .............................................................................25

8.2.4 PMU LDO 1.6V Supply Input ................................................................................25

8.2.5 PMU LDO 1.15V Supply Output ........................................................................... 26

8.3 RTC Battery Supply................................................................................................................ 28

8.4 Power/GND Checklist............................................................................................................ 30

9Clock ......................................................................................................................31

9.1 XTAL Routing Guide...............................................................................................................32

10 Critical Components ..................................................................................... 34

10.1 Critical RF Components..........................................................................................................34

10.1.1 Balun.......................................................................................................................34

10.1.2 Diplexer ..................................................................................................................35

11 Boot Strapping Pins ...................................................................................... 36

12 SMT Guidelines ............................................................................................ 37

12.1 Recommended Pad Specification...........................................................................................37

12.2 E-pad PCB Footprint.............................................................................................................. 38

12.3 E-PAD Soldering Guideline ................................................................................................... 38

12.4 Signal Pad PCB Footprint .......................................................................................................39

12.5 Signal Pad Soldering Guideline ..............................................................................................39

12.6 Reflow Profile Guideline........................................................................................................ 40

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 5 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

3 List of Tables

Table 6-1. PCB Single Setting....................................................................................................................... 9

Table 6-2. PCB Layer Stack-up .................................................................................................................... 9

Table 8-1 MT3620 Power Rail Table ......................................................................................................... 22

Table 8-2 Power Inductor QVL list............................................................................................................ 25

Table 8-3. Checklist for Power and GND Routing.................................................................................... 30

Table 9-1. Recommend 26MHz XTAL Spec for MT3620..........................................................................31

Table 9-2. Recommend Rd/CL Value of XTAL Circuit .............................................................................31

Table 9-3. Clock Routing and Layout Guidelines ..................................................................................... 32

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 6 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

4 List of Figures

Figure 5-1 MT3620 Block Diagram ............................................................................................................. 8

Figure 6-1. A 50Ω single-ended transmission line in reference to Layer-2 .............................................10

Figure 6-2. A 50Ω differential transmission line in reference to Layer-2................................................10

Figure 7-1 RF circuit supporting 5G/2.4G, with full transmit/receive diversity .....................................13

Figure 7-2 RF circuit supporting 2.4G, single antenna (no diversity)......................................................13

Figure 7-3 RF 5G/2.4G Main Path Circuit .................................................................................................14

Figure 7-4 RF Auxiliary Path Circuit .......................................................................................................... 15

Figure 7-5 Matching Components Layout Placement ............................................................................... 15

Figure 7-6 Layout Placement for 2.4GHz/5GHz Matching Circuits ........................................................16

Figure 7-7 RF Power Rails...........................................................................................................................16

Figure 7-8 RF Power Supply Capacitor Placement.................................................................................... 17

Figure 7-9 AVDD_3V3_WF_A_TX Trace Routing Method.................................................................... 17

Figure 8-1 Chip Power Block Diagram .......................................................................................................21

Figure 8-2 PMU Buck Circuit and Layout Placement .............................................................................. 23

Figure 8-3 PMU Buck Ground Layout ...................................................................................................... 23

Figure 8-4 PMU VOUT_1V6 Circuit and Layout Placement ................................................................... 24

Figure 8-5 PMU VOUT_2V5 Output Circuit ............................................................................................ 25

Figure 8-6 PMU 1.6V LDO Input Circuit .................................................................................................. 26

Figure 8-7 AVDD_1V6_CLDO Input Layout ............................................................................................ 26

Figure 8-8 RF AVDD_1V6_XO Input Circuit........................................................................................... 26

Figure 8-9 VOUT_1V15 LDO Output Circuit .............................................................................................27

Figure 8-10 DVDD_3V3 and DVDD_1V15 Power Circuit........................................................................ 28

Figure 8-11 Battery and 3V3 Power Circuit for AVDD33_RTC ............................................................... 29

Figure 9-1 XTAL Circuit ..............................................................................................................................31

Figure 9-2. Crystal Layout Placement and Routing, Showing Layer 2 Keep-out ................................... 32

Figure 11-12-1. Recommended E-pad PCB footprint................................................................................ 38

Figure 11-12-2. Recommended E-pad solder paste stencil ...................................................................... 38

Figure 11-12-3. Recommended signal pad PCB footprint ........................................................................ 39

Figure 11-12-4. Recommended signal pad solder paste stencil................................................................ 39

MediaTek Confiden tial B

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 7 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

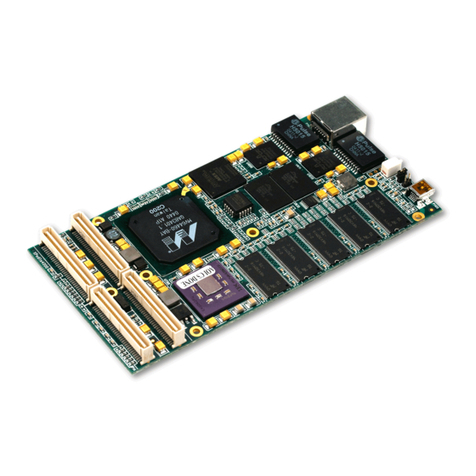

5 System overview

5.1 General Description

MT3620 is a highly integrated single chip tri-core MCU designed to meet the requirements of modern,

robust internet-connected devices. It leverages the Microsoft Codename 4x4 security architecture to

provide an unprecedented level of security to connected device manufacturers. For the lifetime of the

device the Codename 4x4 system provides device authentication and attestation, supports remote over-

the-air software updates to maintain security in the face of evolving attacks, and automates error logging

and reporting. Please refer to the “Codename 4x4 Platform Overview” document from Microsoft for

more information.

MT3620 features an application processor subsystem based on an ARM Cortex-A7 core which runs at

up to 500MHz. The chip also includes two general purpose ARM Cortex-M4F I/O subsystems, each of

which runs at up to 200MHz. These subsystems were designed to support real-time requirements when

interfacing with a variety of on-chip peripherals including UART, I2C, SPI, I2S, and ADC. They are

completely general-purpose Cortex-M4F units which may be tailored to specific application

requirements. On-chip peripherals may be mapped to any of the three end-user accessible cores,

including the CA7.

In addition to these three end-user accessible cores, MT3620 contains a security subsystem with its own

dedicated CM4F core for secure boot and secure system operation. There is also a Wi-Fi subsystem

controlled by a dedicated N9 32-bit RISC core. This contains a 1x1 dual-band 802.11a/b/g/n radio,

baseband and MAC designed to support both low power and high throughput applications without

placing computational load on the user-accessible cores.

MT3620 also includes over 5MB of embedded RAM, split among the various cores. There is a fully-

integrated PMU and a real-time clock. Flash memory is integrated in the MT3620 package. Please refer

to the “Codename 4x4 MT3620 Support Status” document from Microsoft for information about how

much memory and which hardware features are available to end-user applications. Only hardware

features supported by the Codename 4x4 system are available to MT3620 end-users.

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 8 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

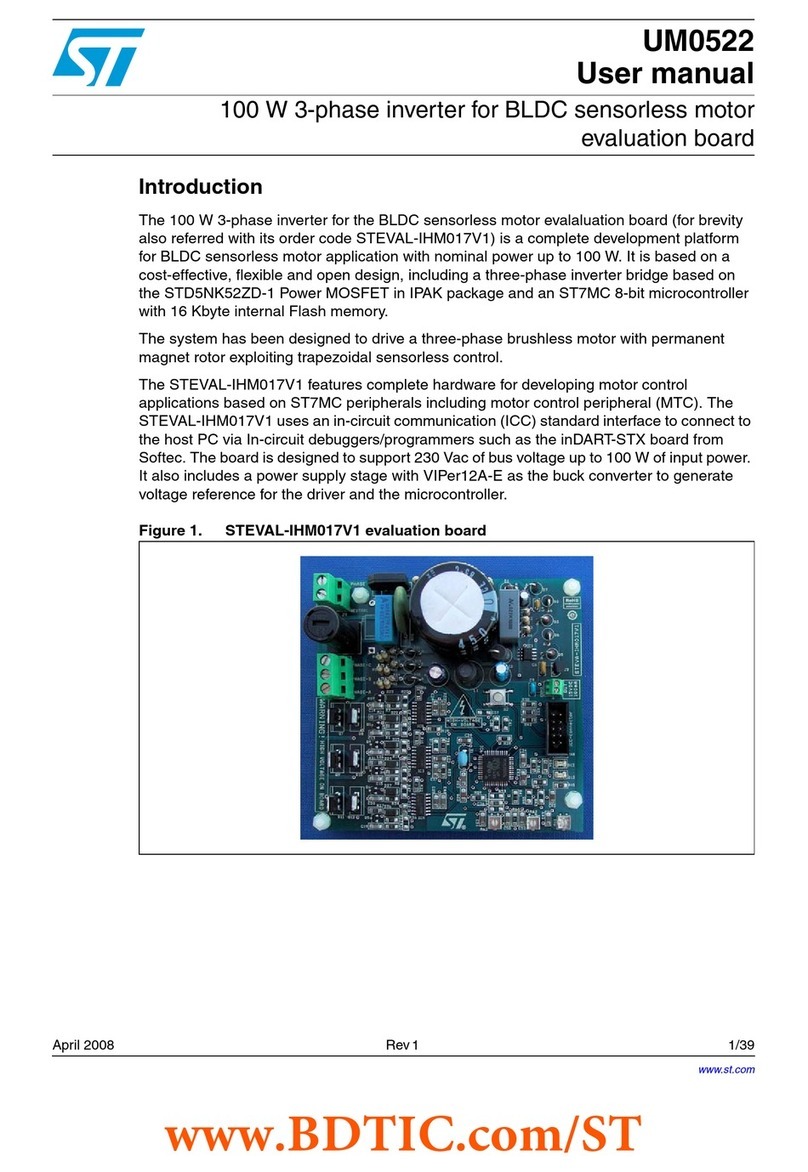

5.2 Block Diagram

Clock

generation

PMU

SWD, SWO

dual channel

flash controller

e-fuse

4kb

N9 core

ILM/DLM

SRAM/ROM Firewalls

dual-band

Wi-FiRF

Wi-Fibaseband

Wi-FiMAC

Wi-FiPSE

Wi-FiRF

SRAM

Wi-Fi subsystem

Application processor subsystem

RTC

UART x 2

PWM/counter

UART x 2

UART/SPI/I2C

up to x76/x12/x6

x5

ADC

UART x 2

I2S

x2

I/O peripherals Cortex-M4F

I/O subsystems

DMA

TCM / cache

192kB

ARM Cortex-

M4F core

SRAM

64kB

x2

e-fuse

4kb

Mailboxes

Pluton security subsystem

Pluton engine

TCM 128kB

ARM Cortex

M4F core

DMA

L2 cache

256kB

ARM Cortex-A7 corewith NEON/FPU

SRAM

4MB

Trust Zone

DMA

e-fuse

4kb

L1 cache

I:64kB / D:32kB

x8

serial flash

serial flash

64kB ROM Recovery

UART

Service UART

Dedicated

GPIO/UART

UART x 2

GPIO

x12/x6

up to x72

Figure 5-1 MT3620 Block Diagram

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 9 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

6 PCB Stack Up and Impedance Control

6.1 PCB Stack-up

The PCB stack-up should include a closely-spaced power and ground plane pair; a 4 layer PCB stack-up is

recommended, as shown in Table 1-1. Table 1-2 shows the recommended structure of the 4 layer PCB.

Table 6-1. PCB Single Setting

4 Layer PCB Single Setting

● Layer-1: signal

● Layer-2: ground plane, unbroken

● Layer-3: Vdd (3.3V) plane

● Layer-4: signal

Table 6-2. PCB Layer Stack-up

PCB Stack Up

Layer

Signal Type

Layer Type

PCB thickness

εr

mils

mm

Top side solder mask

1.0

0.025

3.5

Layer-1

differential & signal

copper + plating

2.76

0.07

prepreg

4.33

0.11

4.1

Layer-2

GND

copper

1.38

0.035

core

47.24

1.2

4.4

Layer-3

Vdd/GND

copper

1.38

0.035

prepreg

4.33

0.11

4.1

Layer-4

differential & signal

copper + plating

2.76

0.07

Bottom side solder mask

1.0

0.025

3.5

TOTAL

66.18 (mils)

1.68 (mm)

Select dielectric thickness to support required characteristic signal trace impedances and power plane

capacitance and inductance. Perform resonance analysis on all plane cavities.

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 10 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

6.2 Transmission Line

6.2.1 50ΩSingle-ended

50Ω single-ended transmission line on the top plane is in reference to the GND plane on layer-2.

Figure 6-1. A 50Ω single-ended transmission line in reference to Layer-2

6.2.2 50ΩDifferential-ended

50Ω differential transmission line on the top plane is in reference to the GND plane on layer-2.

Figure 6-2. A 50Ω differential transmission line in reference to Layer-2

Impedance matching should be guaranteed by the PCB manufacturer.

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 11 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

6.3 Package Information

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 12 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

6.4 Top Marking

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 13 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

7 RF Front-End Circuit Design

7.1 RF System Overview

The following circuit schematics show two possible RF configurations. The first supports dual band

(5GHz and 2.4GHz) and includes support to transmit and receive diversity. The second circuit is a

simplified version that supports single band (2.4GHz) and a single antenna (no diversity).

Figure 7-1 RF circuit supporting 5G/2.4G, with full transmit/receive diversity

Figure 7-2 RF circuit supporting 2.4G, single antenna (no diversity)

7.2 Wi-Fi RF Main Path Schematic

WF_A_RFIO:

WF_A_RFIO is the single-ended input and output interface for the 5GHz Wi-Fi radio transceiver.

The 5GHz Wi-Fi transceiver radio integrates a balun, PA, LNA and T/R switch.

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 14 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

WF_G_RF_IOP and WF_G_RF_ION:

WF_G_RF_IOP and WF_G_RF_ION form the differential input and output interface of the

2.4GHz Wi-Fi radio transceiver.

The 2.4GHz Wi-Fi transceiver intergrates a PA, LNA and T/R switch.

The differential pair is 50Ωhaving a matching network between 50Ω-50Ωbalun.

Figure 7-3 RF 5G/2.4G Main Path Circuit

7.3 Wi-Fi RF Auxiliary Path Front-End Schematic

WF_A_RF_AUXIN:

WF_A_RF_AUXIN is an additional single-ended input interface of the 5GHz Wi-Fi receiver

which support a 5GHz receive diversitity function.

WF_G_RF_AUXIN:

WF_G_RF_AUXIN is an additional single-ended input interface of the 2.4GHz Wi-Fi receiver

which supports a 2.4GHz receive diversitity function.

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 15 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

Figure 7-4 RF Auxiliary Path Circuit

7.4 RF Component Placement

7.4.1 RF matching circuit placement

2.4GHz matching component placement

Please make placement and layout of 2GHz matching network according to the following figures.

Figure 7-5 Matching Components Layout Placement

We stongly recommend you place RF matching circuits, including the main 2.4GHz, main 5GHz

and auxiliarlly 5GHz paths, near the MT3620 chip as the figure shows below.

R2

R58

C10

C11

C12

C13

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 16 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

Figure 7-6 Layout Placement for 2.4GHz/5GHz Matching Circuits

7.4.2 RF Power circuit placement

There are two RF power rails which can share capacitors, shown in Figure 7-5

1. AVDD_3V3_WF_A_TX, AVDD_3V3_WF_G_TX, AVDD_3V3_WF_G_PA and

AVDD_3V3_WF_A_PA

2. AVDD_1V6_WF_TRX and AVDD_1V6_WF_AFE

Figure 7-7 RF Power Rails

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 17 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

Place these RF power capacitors as close as possible to the relevant pins. Each pin/pin-pair should be

decoupled with a 2.2uF or 4.7uF capacitor in parallel with a 10pF capacitor. The 10pF capacitor

effectively acts as a filter to reduce high-frequency noise.

Figure 7-8 RF Power Supply Capacitor Placement

If necessary, pin 157 (NC) can be used for AVDD_3V3_WF_A_TX trace routing as shown below.

Figure 7-9 AVDD_3V3_WF_A_TX Trace Routing Method

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 18 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

7.5 Diversity

7.5.1 Receive diversity is supported in hardware

The figure shown below is a block diagram of the RF front-end design when using on-chip receive

diversity.

Receive diversity is supported without the need for an external switch, by way of two additional

receive-only diversity antenna ports.

Per-packet antenna diversity (fast-diversity).

Basebase softwware automatically controls switching between the main and auxilliary receive

paths.

Transmission only occurs throug the main antenna port.

BBPLL

RSSI

Meter

R-cal

RC-cal

SX0

(3~4GHz)

LPF

5G TRX

TRSW

Balun

RFDIG

BG

WF_A_RFIO

WF_G_RF_ION

TRSW

2.4G TRX

WF_G_RF_AUXIN

WF_A_RF_AUXIN

Antenna

port

WF_G_RF_IOP

M

M

M

M

M

M

AGC

ANT_ASSIGN

Antenna

Diversity

Engine

7.5.2 Full transmit/receive diversity is supported in software but requires

an external DPTP switch

The figure shown below shows the RF front-end design when supporting full transmit/receive antenna

diversity.

Full transmit/receive antenna diversity requires an external DPDT RF switch.

In this case RF transceiving is fixed to the main path only, and does not use the auxilliary diversity

receive ports.

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 19 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

If full diversity is selected, the baseband software automatically drives the WF_ANTSEL0/1 pins

to control the external diverisity switch.

BBPLL

RSSI

Meter

R-cal

RC-cal

SX0

(3~4GHz)

LPF

5G TRX

TRSW

Balun

RFDIG

BG

WF_A_RFIO

WF_G_RF_ION

TRSW

2.4G TRX

Antenna

port

WF_G_RF_IOP

WF_ANTSEL0

WF_ANTSEL1DPDT

M

M

M

M

AGC

ANT_ASSIGN

Antenna

Diversity

Engine

7.5.3 Antenna Placement Guidelines for Antenna Diversity

Radio signals rarely pass directly from one point in space to another. In reality, the signals are reflected

off walls etc. and will form multiple simultaneous paths between the two points. This results in points

in space where there are strong signals, and conversely, points where there are very weak signal, or nulls.

In the case of a device having a single antenna, if the antenna happens to be in a null, it may struggle or

even fail to reliably connect and transfer data.

Adopting the use of two antenna can help to overcome these problems. More specifically though, to gain

the full advantages of antenna diversity the two antennas need to be (a) physically separated by a

distance of at least a ¼ wavelength. At 2.4GHZ, a ¼ wavelength is approximately 3cm and at 5GHz,

approximately 1.5 cm. In addition, the polarization of the radio signals can be altered as they passes

through different mediums such as walls and doors. By placing the two antennas at 90’ to each other

maximises the likelihood that at least of the them will be correctly oriented to receive a strong signal.

This is illustrated in the following diagram.

MT3620

Hardware User Guide

MediaTek Confidential

© 2020 MediaTek Inc.

Page 20 of 40

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure

of this information in whole or in part is strictly prohibited.

7.6 RF Layout Checklist

Parameter

Description

Hint

Impedance (Z)

50Ω (single-ended)

No external termination required, on-chip

termination resistor is implemented.

Trace Routing

Routing method

RF traces should be as short as possible.

RF traces should be surrounded by a strong

ground with many vias connected to the

reference ground.

RF traces should be straight and always on

the 1st layer. Avoid changing layers and any

vias.

Ground Plane

must be ground referenced

The reference ground for RF traces should

be on the 2nd layer.

The reference ground of RF traces should be

complete planes, and preferably unbroken.

Others

Other notifications

Do not let any noisy traces run near or cross

RF traces, e.g. data lines, clock signals,

digital power and ground traces, etc.

Matching devices should be as small as

possible, e.g. 0201 is better than 0402.

Table of contents

Other MEDIATEK Computer Hardware manuals