MEDIATEK Ralink MT7620 Operating instructions

MT7620

PROGRAMMING

GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

PGMT7620_V.1.0_040503

Page 2 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

MT7620 Overview

The MT7620 SoC includes a high performance 580 MHz MIPS24KEc CPU core and USB host controller/PHY,

which is designed to enable a multitude of high performance, cost-effective IEEE 802.11n applications with a

MediaTek (Ralink) client card.

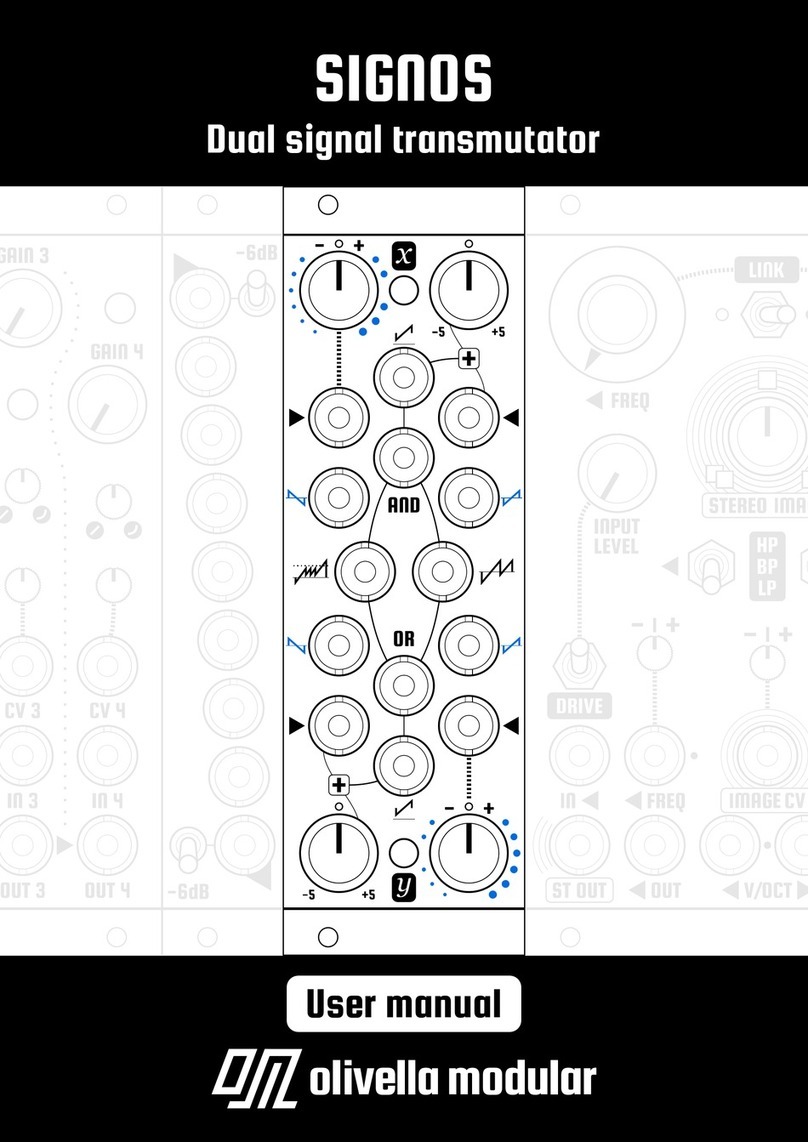

Functional Block Diagram

MIPS 24KEc

64 KB I-Cache

32 KB D-

Cache

(580 MHz) OCP Bridge

OCP

_IF

Arbiter

DRAM

Controller

RBUS (SYS_CLK)

SPI

NFC

PBUS

GDMA

RJ45 x5

Switch

(4FE + 2GE)

5-Port EPHY

RGMII

TMII/MII

x2

PCIe 1.1

PHY

Single-Port

USB 2.0 PHY

Host/

Device

PCIe x1

UART

GPIO

PCM x4

I2S

I2C

I2S

PBUS

INTC

I2C

GPIO

/LED

SPI

NAND

UART

ToCPU

interrupt

s

16-Bit

SDR/DDR1/DDR2

EJTAG

WLAN

11n 2x2

2.4 GHz

Timer

PCM

SDHC

SD

Figure 1-1 MT7620 Block Diagram

There are several masters (MIPS 24KEc, USB , PCI Express) in the MT7620 SoC on a high performance, low

latency Rbus, (Ralink Bus). In addition, the MT7620 SoC supports lower speed peripherals such as UART, GPIO,

and SPI via a low speed peripheral bus (Pbus). The SDRAM/DDR1/DDR2 controller is the only bus slave on the

Rbus. It includes an Advanced Memory Scheduler to arbitrate the requests from bus masters, enhancing the

performance of memory access intensive tasks.

PGMT7620_V.1.0_040503

Page 3 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

Table of Contents

1. MIPS 24K PROCESSOR 11

1.1 FEATURES 11

1.2 BLOCK DIAGRAM 12

1.3 MEMORY MAP SUMMARY 13

1.4 CLOCK PLAN 14

1.5 CPU CLOCK MUX 15

2. REGISTERS 16

2.1 NOMENCLATURE 16

2.2 SYSTEM CONTROL 17

2.2.1 FEATURES 17

2.2.2 BLOCK DIAGRAM 17

2.2.3 LIST OF REGISTERS 18

2.2.4 REGISTER DESCRIPTIONS (BASE:0X1000_0000) 19

2.3 TIMER 46

2.3.1 FEATURES 46

2.3.2 BLOCK DIAGRAM 47

2.3.3 LIST OF REGISTERS 48

2.3.4 REGISTER DESCRIPTIONS (BASE:0X1000_0100) 49

2.4 INTERRUPT CONTROLLER 53

2.4.1 FEATURES 53

2.4.2 BLOCK DIAGRAM 53

2.4.3 LIST OF REGISTERS 54

2.4.4 REGISTER DESCRIPTIONS (BASE:0X1000_0200) 55

2.5 SYSTEM TICK COUNTER 60

2.5.1 LIST OF REGISTERS 60

2.5.2 REGISTER DESCRIPTIONS (BASE:0X1000_0D00) 61

2.6 UART 62

2.6.1 FEATURES 62

2.6.2 BLOCK DIAGRAM 62

2.6.3 LIST OF REGISTERS 63

2.6.4 REGISTER DESCRIPTIONS (BASE:0X1000_0500) 64

2.7 UART LITE 72

2.7.1 FEATURES 72

2.7.2 BLOCK DIAGRAM 72

2.7.3 LIST OF REGISTERS 73

2.7.4 REGISTER DESCRIPTIONS (BASE:0X1000_0C00) 74

2.8 PROGRAMMABLE I/O 81

2.8.1 FEATURES 81

2.8.2 BLOCK DIAGRAM 81

2.8.3 LIST OF REGISTERS 82

2.8.4 REGISTER DESCRIPTIONS (BASE:0X1000_0600) 84

2.9 I2CCONTROLLER 97

2.9.1 FEATURES 97

2.9.2 BLOCK DIAGRAM 97

2.9.3 LIST OF REGISTERS 98

PGMT7620_V.1.0_040503

Page 4 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.9.4 REGISTER DESCRIPTIONS (BASE:0X1000_0900) 99

2.10 NAND FLASH CONTROLLER 105

2.10.1 FEATURES 105

2.10.2 NORMAL MODE FLOW 105

2.10.3 ECC 105

2.10.4 LIST OF REGISTERS 108

2.10.5 REGISTER DESCRIPTIONS (BASE:0X1000_0800) 109

2.11 PCM CONTROLLER 116

2.11.1 FEATURES 116

2.11.2 BLOCK DIAGRAM 116

2.11.3 LIST OF REGISTERS 118

2.11.4 REGISTER DESCRIPTIONS (BASE:0X1000_2000) 119

2.11.5 PCM CONFIGURATION 130

2.12 GENERIC DMA CONTROLLER 132

2.12.1 FEATURES 132

2.12.2 BLOCK DIAGRAM 132

2.12.3 PERIPHERAL CHANNEL CONNECTION 133

2.12.4 LIST OF REGISTERS 134

2.12.5 REGISTER DESCRIPTIONS (BASE:0X1000_2800) 135

2.13 SPI CONTROLLER 139

2.13.1 FEATURES 139

2.13.2 BLOCK DIAGRAM 139

2.13.3 LIST OF REGISTERS 140

2.13.4 REGISTER DESCRIPTIONS (BASE:0X1000_0B00) 141

2.14 I2S CONTROLLER 152

2.14.1 FEATURES 152

2.14.2 BLOCK DIAGRAM 152

2.14.3 I2SSIGNAL TIMING FOR I2SDATA FORMAT 153

2.14.4 LIST OF REGISTERS 154

2.14.5 REGISTER DESCRIPTIONS (BASE:0X1000_0A00) 155

2.15 MEMORY CONTROLLER 159

2.15.1 FEATURES 159

2.15.2 BLOCK DIAGRAM 159

2.15.3 SDRAM INITIALIZATION SEQUENCE 159

2.15.4 SDRAM POWER SAVING CONFIGURATION 160

2.15.5 DDR INITIALIZATION SEQUENCE 161

2.15.6 LIST OF REGISTERS 162

2.15.7 REGISTER DESCRIPTIONS (BASE:0X1000_0300) 163

2.16 RBUS MATRIX AND QOSARBITER 178

2.16.1 FEATURES 178

2.16.2 BLOCK DIAGRAM 178

2.16.3 LIST OF REGISTERS 179

2.16.4 REGISTER DESCRIPTIONS (BASE:0X1000_0400) 180

2.17 USB HOST CONTROLLER &PHY 183

2.17.1 FEATURES 183

2.17.2 BLOCK DIAGRAM 183

2.17.3 REGISTER DESCRIPTION (BASE:0X101C.0000) 183

2.17.4 EHCI OPERATION REGISTERS (BASE:0X101C.0000) 184

PGMT7620_V.1.0_040503

Page 5 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.17.5 OHCI OPERATION REGISTERS (BASE:0X101C.1000) 185

2.18 USB DEVICE CONTROLLER 186

2.18.1 FEATURES 186

2.18.2 BLOCK DIAGRAM 186

2.18.3 BULK OUT 186

2.18.4 LEGACY MODE 187

2.18.5 AGGREGATION MODE 187

2.18.6 DE-AGGREGATION MODE 188

2.18.7 BULK-OUT AGGREGATION FORMAT 189

2.18.8 BULK IN 189

2.18.9 PDMA DESCRIPTOR FORMAT 190

2.18.10 REGISTER DESCRIPTIONS (BASE:0X1012_0000) 192

2.18.11 USB DEVICE CONTROLLER REGISTERS 192

2.18.12 UDMA REGISTERS 193

2.18.13 PDMA REGISTERS 194

2.19 FRAME ENGINE 202

2.19.1 PSE FEATURES 202

2.19.2 PPE FEATURES 202

2.19.3 PACKET DMA (PDMA) FEATURES 202

2.19.4 BLOCK DIAGRAM 203

2.19.5 PDMA FIFO-LIKE RING CONCEPT 204

2.19.6 PDMA TX DESCRIPTOR FORMAT 205

2.19.7 PDMA RX DESCRIPTOR FORMAT 207

2.19.8 GLOBAL REGISTERS (BASE:0X1010_0000) 209

2.19.9 CPU PORT REGISTERS (BASE:0X1010_0400) 216

2.19.10 PDMA REGISTERS (BASE:0X1010_0800) 223

2.19.11 MIB COUNTER DESCRIPTION (BASE:0X1010_1000) 235

2.20 ETHERNET SWITCH 237

2.20.1 FEATURES 237

2.20.2 BLOCK DIAGRAM 238

2.20.3 FRAME CLASSFICATION 238

2.20.4 SWITCH L2/L3 ADDRESS TABLE 240

2.20.5 VIRTUAL LAN 244

2.20.6 ACCESS CONTROL LOGIC 247

2.20.7 ARL REGISTERS (BASE:0X1011_0000) 252

2.20.8 BMU REGISTERS 291

2.20.9 PORT REGISTERS 308

2.20.10 MAC REGISTERS 320

2.20.11 MIB REGISTERS 329

2.20.12 GSW CONFIGURATION REGISTERS 338

2.20.13 MDIO CONTROL 347

2.21 PCI/PCIE CONTROLLER 354

2.21.1 BLOCK DIAGRAM 355

2.21.2 PCIE CONTROLLER ACTING AS A PCIE DEVICE 356

2.21.3 BLOCK DIAGRAM 357

2.21.4 PCI/PCIE MASTER ACCESS IN HOST MODE 358

2.21.5 PCIE CONTROLLER HOST MODE INITIALIZATON EXAMPLE 359

2.21.6 HOST-PCI BRIDGE REGISTERS (BASE:0X1014_0000) 359

2.21.7 PCIE0RC CONTROL REGISTERS (BASE:0X1014_2000) 363

PGMT7620_V.1.0_040503

Page 6 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.21.8 MEMORY WINDOWS REGISTERS (BASE:0X1015_0000) 367

2.21.9 IO WINDOWS (BASE:0X1016_0000) 367

2.22 802.11N 2T2R MAC/BBP 368

2.22.1 FEATURES 368

2.22.2 BLOCK DIAGRAM 368

2.22.3 802.11N 2T2R MAC/BBP REGISTER MAP 369

2.22.4 SCH/WPDMA REGISTERS (BASE:0X1018_0000) 370

2.22.5 PBF REGISTERS (BASE:0X1018_0000) 382

2.22.6 RF TEST REGISTERS (BASE:0X1018_0000) 392

2.22.7 MAC REGISTERS (BASE:0X1018_0000) 393

2.22.8 MAC TIMING CONTROL REGISTERS (BASE:0X1018_0000) 409

2.22.9 MAC POWER SAVE CONFIGURATION REGISTERS (BASE:0X1018_0000) 416

2.22.10 MAC TX CONFIGURATION REGISTERS (BASE:0X1018_0000) 421

2.22.11 MAC RX CONFIGURATION REGISTERS (BASE:0X1018_0000) 449

2.22.12 MAC SECURITY CONFIGURATION REGISTERS (BASE:0X1018_0000) 457

2.22.13 MAC HCCA/PSMP CONTROL STATUS REGISTERS (BASE:0X1018_0000) 458

2.22.14 MAC STATISTIC COUNTERS (BASE:0X1018_0000) 462

2.22.15 MAC SEARCH TABLE (BASE:0X1018_1800) 471

3. SECURITY ENTRY FORMATS AND KEY TABLES 473

3.1 SECURITY ENTRY FORMAT TABLES (BASE:1018.0000, OFFSET:0X4000) 473

3.1.1 SECURITY KEY FORMAT (8DW) 473

3.1.2 IV/EIV/WAPI_PN FORMAT (4DW) 473

3.1.3 WCID ATTRIBUTE ENTRY FORMAT (1DW) 474

3.1.4 SHARED KEY MODE ENTRY FORMAT (1DW) 475

3.2 SECURITY TABLES (OFFSET:0X4000) 476

3.3 SECURITY TABLE MAP 476

3.3.1 PAIRWISE KEY TABLE (OFFSET:0X4000) 477

3.3.2 IV/EIV TABLE (OFFSET:0X6000) 477

3.3.3 WCID ATTRIBUTE TABLE (OFFSET:0X6800) 477

3.3.4 SHARED KEY TABLE (OFFSET:0X6C00) 477

3.3.5 SHARED KEY MODE (OFFSET:0X7000) 478

3.3.6 SPARE MEMORY SPACE MODE (OFFSET:0X7010 TO 0X73EC) 478

3.3.7 SHARED KEY MODE EXTENSION (FOR BSS_IDX=8 TO 15) (OFFSET:0X73F0) 479

3.3.8 SHARED KEY TABLE EXTENSION (FOR BSS_IDX=8 TO 15) (OFFSET:0X7400) 479

3.3.9 WAPI PN TABLE (EXTENSION OF IV/EIV TABLE)(OFFSET:0X7800) 480

4. TX/RX DESCRIPTORS AND WIRELESS INFORMATION 481

4.1 TX DESCRIPTORS AND FRAME INFORMATION 481

4.1.1 TXD FORMAT 482

4.1.2 TX WIRELESS INFORMATION 484

4.2 RX DESCRIPTORS AND WIRELESS INFORMATION 488

4.2.1 RXD FORMAT 489

4.2.2 RXINFO FORMAT 490

4.2.3 RXWI FORMAT 492

4.3 BRIEF PHYRATE FORMAT AND DEFINITION 494

4.3.1 MODULATION AND CODING SCHEME 495

5. SD HOST CONTROLLER 497

5.1 FEATURES 497

PGMT7620_V.1.0_040503

Page 7 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

5.2 SD HOST BLOCK DIAGRAM 497

5.2.1 BASIC DMA MODE 498

5.2.2 LINKED-LIST BASED DMA MODE 498

5.2.3 DMA GENERIC PACKET DESCRIPTOR (GPD) FORMAT 500

5.2.4 DMA BUFFER DESCRIPTOR (BD) FORMAT 502

5.2.5 REGISTER DESCRIPTION (BASE:0X1013_0000) 503

6. LIST OF REGISTERS 504

7. ABBREVIATIONS 520

8. REVISION HISTORY 523

PGMT7620_V.1.0_040503

Page 8 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

Table of Figures

FIGURE 1-1 MT7620 BLOCK DIAGRAM .......................................................................................................................... 2

FIGURE 1-1 MIPS 24KEC PROCESSOR .......................................................................................................................... 12

FIGURE 1-2 MT7620 CLOCK DIAGRAM ........................................................................................................................ 14

FIGURE 1-3 CPU CLOCK MUX ..................................................................................................................................... 15

FIGURE 2-1 SYSTEM CONTROL BLOCK DIAGRAM ............................................................................................................. 17

FIGURE 2-2 TIMER BLOCK DIAGRAM............................................................................................................................. 47

FIGURE 2-3 INTERRUPT CONTROLLER BLOCK DIAGRAM .................................................................................................... 53

FIGURE 2-4 UART BLOCK DIAGRAM............................................................................................................................. 62

FIGURE 2-5 UART LITE BLOCK DIAGRAM ...................................................................................................................... 72

FIGURE 2-6 PROGRAMMABLE I/O BLOCK DIAGRAM ........................................................................................................ 81

FIGURE 2-7 I2C CONTROLLER BLOCK DIAGRAM .............................................................................................................. 97

FIGURE 2-8 NORMAL MODE FLOW............................................................................................................................. 105

FIGURE 2-9 24-BIT ECC GENERATED FROM 512-BYTE DATA ..........................................................................................106

FIGURE 2-10 HARDWARE ECC DETECTION FLOWCHART................................................................................................. 107

FIGURE 2-11 PCM CONTROLLER BLOCK DIAGRAM........................................................................................................ 116

FIGURE 2-12 GENERIC DMA CONTROLLER BLOCK DIAGRAM...........................................................................................132

FIGURE 2-13 SPI CONTROLLER BLOCK DIAGRAM ..........................................................................................................139

FIGURE 2-14 I2STRANSMITTER BLOCK DIAGRAM..........................................................................................................152

FIGURE 2-15 I2S TRANSMIT/RECEIVE .........................................................................................................................153

FIGURE 2-16 SRAM/SDRAM CONTROLLER BLOCK DIAGRAM ........................................................................................159

FIGURE 2-17 QOSARBITRATION BLOCK DIAGRAM ........................................................................................................178

FIGURE 2-18 USB HOST CONTROLLER &PHY BLOCK DIAGRAM......................................................................................183

FIGURE 2-19 USB DEVICE CONTROLLER BLOCK DIAGRAM ..............................................................................................186

FIGURE 2-20 DE-AGGREGATION FLOW........................................................................................................................188

FIGURE 2-21 BULK-OUT AGGREGATION FORMAT ..........................................................................................................189

FIGURE 2-22 PDMA TX DESCRIPTOR FORMAT .............................................................................................................190

FIGURE 2-23 PDMA RX DESCRIPTOR FORMAT.............................................................................................................191

FIGURE 2-24 USB DEVICE REGISTER MAPPING.............................................................................................................192

FIGURE 2-25 FRAME ENGINE BLOCK DIAGRAM.............................................................................................................203

FIGURE 2-26 PDMA FIFO-LIKE RING CONCEPT ...........................................................................................................204

FIGURE 2-27 PDMA TX DESCRIPTOR FORMAT .............................................................................................................205

FIGURE 2-28 PDMA RX DESCRIPTOR FORMAT.............................................................................................................207

FIGURE 2-29 ETHERNET SWITCH BLOCK DIAGRAM ........................................................................................................238

FIGURE 2-30 PHY ADDRESS DECODING (I)...................................................................................................................347

FIGURE 2-31 PHY ADDRESS DECODING (II).................................................................................................................. 348

FIGURE 2-32 PCIE HOST TOPOLOGY...........................................................................................................................354

FIGURE 2-33 PCIE AP MODE....................................................................................................................................355

FIGURE 2-34 PCIE CONTROLLER BEHAVING AS A PCIE ENDPOINT.....................................................................................356

FIGURE 2-35 PCIE RC/EP BLOCK DIAGRAM ................................................................................................................357

FIGURE 2-36 PCIE MEMORY SPACE PROGRAMMABLE MAPPING......................................................................................358

FIGURE 2-37 PCI MEMORY SPACE FIXED MAPPING.......................................................................................................358

FIGURE 2-38 I/O SPACE PROGRAMMABLE MAPPING..................................................................................................... 358

FIGURE 2-39 802.11N 2T2R MAC/BBP BLOCK DIAGRAM ...........................................................................................368

FIGURE 2-40 802.11N 2T2R MAC/BBP REGISTER MAP .............................................................................................. 369

FIGURE 3-1 SECURITY KEY MEMORY LOCATIONS ...........................................................................................................476

FIGURE 4-1 TXD AND TX FRAME INFORMATION............................................................................................................481

FIGURE 4-2 TXD FORMAT ........................................................................................................................................482

FIGURE 4-3 RX DESCRIPTOR RING ..............................................................................................................................488

PGMT7620_V.1.0_040503

Page 9 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

FIGURE 4-4 RX DESCRIPTOR FORMAT.......................................................................................................................... 489

FIGURE 4-5 RXINFO FORMAT...................................................................................................................................490

FIGURE 4-6 RXWI FRAME FORMAT............................................................................................................................ 492

FIGURE 5-1 SD HOST BLOCK DIAGRAM .......................................................................................................................497

FIGURE 5-2 BASIC DMA...........................................................................................................................................498

FIGURE 5-3 DESCRIPTOR DMA.................................................................................................................................. 499

FIGURE 5-4 GPD FORMAT........................................................................................................................................500

FIGURE 5-5 BD FORMAT ..........................................................................................................................................502

PGMT7620_V.1.0_040503

Page 10 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

List of Tables

TABLE 2-1UART LITE INTERRUPT PRIORITIES................................................................................................................. 75

TABLE 2-2 PDMA RX FIELD DESCRIPTIONS ..................................................................................................................191

TABLE 2-3 RULE MASK.............................................................................................................................................249

TABLE 2-4 RATE CONTROL ........................................................................................................................................249

TABLE 2-5 RULE CONTROL ........................................................................................................................................249

TABLE 2-6 TRTCM METER TABLE............................................................................................................................... 251

TABLE 2-7 ADDRESS TABLE WRITE DATA REGISTER:MAC ADDRESS .................................................................................277

TABLE 2-8 ADDRESS TABLE WRITE DATA REGISTER:DIP ENTRY....................................................................................... 277

TABLE 2-9 ADDRESS TABLE WRITE DATA REGISTER:SIP ENTRY .......................................................................................277

TABLE 2-10 ADDRESS TABLE READ DATA REGISTER:MAC ENTRY ....................................................................................279

TABLE 2-11 ADDRESS TABLE READ DATA REGISTER:DIP ENTRY.......................................................................................280

TABLE 2-12 ADDRESS TABLE READ DATA REGISTER:SIP ENTRY .......................................................................................280

TABLE 2-13 VLAN AND ACL WRITE DATA-I REGISTER:VLAN ENTRY...............................................................................281

TABLE 2-14 VLAN AND ACL WRITE DATA-I REGISTER:ACL RULE TABLE ..........................................................................282

TABLE 2-15 VLAN AND ACL WRITE DATA-I REGISTER:ACL RULE MASK ..........................................................................282

TABLE 2-16 VLAN AND ACL WRITE DATA-I REGISTER:ACL RATE CONTROL .....................................................................282

TABLE 2-17 VLAN AND ACL WRITE DATA-I REGISTER:ACL RULE CONTROL .....................................................................282

TABLE 2-18 VLAN AND ACL WRITE DATA-I REGISTER:TRTCM METER TABLE................................................................... 283

TABLE 2-19 VLAN AND ACL WRITE DATA-II REGISTER:VLAN ENTRY..............................................................................283

TABLE 2-20 VLAN AND ACL WRITE DATA-II REGISTER:ACL RULE TABLE .........................................................................283

TABLE 2-21 VLAN AND ACL WRITE DATA-II REGISTER:ACL RULE MASK .........................................................................283

TABLE 2-22 VLAN AND ACL WRITE DATA-II REGISTER:ACL RATE CONTROL ....................................................................283

TABLE 2-23 VLAN AND ACL WRITE DATA-II REGISTER:ACL RULE CONTROL ....................................................................283

TABLE 2-24 VLAN AND ACL WRITE DATA-II REGISTER:TRTCM METER TABLE.................................................................. 284

TABLE 2-25 DEBUG CONTROL REGISTER:DEBUG ID AND CONTROL ..................................................................................289

TABLE 2-26 PCI/PCIE SCENERIO AND RELATIVE CONTROL REGISTER SETTINGS.....................................................................356

TABLE 2-27: 0X1398 TX_RATE_LUT_EN =0AND MULTI_MAC_ADDRESS =0 .........................................................471

TABLE 2-28: 0X1398 TX_RATE_LUT_EN =1AND MULTI_MAC_ADDRESS =0 .........................................................471

TABLE 2-29: 0X1398 TX_RATE_LUT_EN =1AND MULTI_MAC_ADDRESS =1 .........................................................472

TABLE 3-1 IV/EIV FORMAT ......................................................................................................................................473

TABLE 3-2 WAPI_PN FORMAT .................................................................................................................................474

TABLE 3-3 WCID ATTRIBUTE ENTRY FORMAT ..............................................................................................................475

TABLE 3-4 SHARED KEY MODE ENTRY FORMAT (1DW) .................................................................................................475

TABLE 3-5 PAIRWISE KEY TABLE (OFFSET:0X4000)....................................................................................................... 477

TABLE 3-6 IV/EIV TABLE (OFFSET:0X6000)................................................................................................................ 477

TABLE 3-7 WCID ATTRIBUTE TABLE (OFFSET:0X6800) .................................................................................................477

TABLE 3-8 SHARED KEY TABLE (OFFSET:0X6C00)......................................................................................................... 478

TABLE 3-9 SHARED KEY MODE (OFFSET:0X7000) ........................................................................................................ 478

TABLE 3-10 SHARED KEY MODE EXTENSION (FOR BSS_IDX=8 TO15) (OFFSET:0X73F0)....................................................479

TABLE 3-11 SHARED KEY TABLE EXTENSION (FOR BSS_IDX=8 TO15) (OFFSET:0X7400) ....................................................480

TABLE 3-12 WAPI PN TABLE (EXTENSION OF IV/EIV TABLE)(OFFSET:0X73F0) ...............................................................480

TABLE 4-1 TX DESCRIPTOR FORMAT FIELD DESCRIPTIONS ...............................................................................................483

TABLE 4-2 TXWI FRAME FORMAT..............................................................................................................................484

TABLE 4-3 TXWI FIELD DESCRIPTIONS ........................................................................................................................487

TABLE 4-4 RXWI FIELD DESCRIPTIONS ........................................................................................................................493

TABLE 4-5 BRIEF PHY RATE FORMAT AND DEFINITION ..................................................................................................494

TABLE 4-6 MODULATION AND CODING SCHEME ...........................................................................................................496

PGMT7620_V.1.0_040503

Page 11 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

1. MIPS 24K Processor

1.1 Features

8-stage pipeline

32-bit address paths

64-bit data paths to caches and external interfaces

MIPS32-Compatible Instruction Set

Multiply-Accumulate and Multiply-Subtract Instructions (MADD, MADDU, MSUB, MSUBU)

Targeted Multiply Instruction (MUL)

Zero/One Detect Instructions (CLZ, CLO)

Wait instructions (WAIT)

Conditional Move instructions (MOVZ, MOVN)

Prefetch instructions (PREF)

MIPS32 Enhanced Architecture (Release 2) Features

Vectored interrupts and support for an external interrupt controller

Programmable exception vector base

Atomic interrupt enable/disable

GPR shadow registers (one, three or seven additional shadows can be optionally added to minimize

latency for interrupt handlers)

Bit field manipulation instructions

MIPS32 Privileged Resource Architecture

MIPS DSP ASE

Fractional data types (Q15, Q31)

Saturating arithmetic

SIMD instructions operate on 2x16 b or 4x8 b simultaneously

3 additional pairs of accumulator registers

Programmable Memory Management Unit

32 dual-entry JTLB with variable page sizes

4-entry ITLB

8-entry DTLB

Optional simple Fixed Mapping Translation (FMT) mechanism

MIPS16e™ Code Compression

16-bit encodings of 32-bit instructions to improve code density

Special PC-relative instructions for efficient loading of addresses and constants

SAVE & RESTORE macro instructions for setting up and tearing down stack frames within subroutines

Improved support for handling 8 and 16-bit datatypes

Programmable L1 Cache Sizes

Instruction cache size: 32 KB

Data cache size: 16 KB

4-Way Set Associative

Up to 8 outstanding load misses

Write-back and write-through support

32-byte cache line size

PGMT7620_V.1.0_040503

Page 12 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

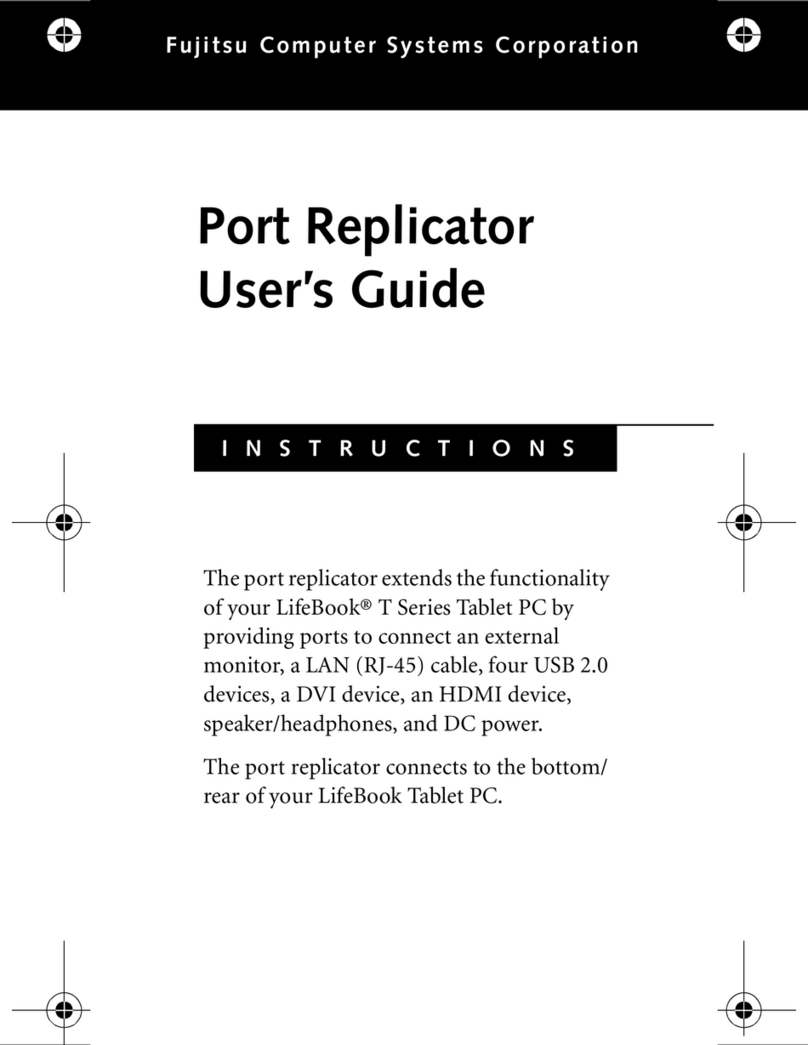

1.2 Block Diagram

Instruction

scratchpad

RAM

i-cache 0/8/16/32/64 KB

4-way set associative Trace

TAP

CorExtend Fetch Unit

8-entry instruction buffer

512-entry BHT

4-entry RPS

Execution Unit

(RF/ALU/

Shift)

BIU

4-entry merging

write buffer,

10 outstanding

reads

MMU

16/32/64 JTLB or FMT

Non-blocking load/store

unit

8 outstanding misses

D-cache

0/8/16/32/64 KB

4-way set associative

Data scratchpad

RAM

System Co-

processor

Power

Managment

CP2

MDU

EJTAG Off/on chip

trace I/F

Off-chip

Debug I/F

OCP

Interface on-

chip Bus(es)

DSPRAM

DMA OCP

Interface

User-defined

COP2 block

User-defined

CorExtend

block

ISPRAM DMA

OCP I/F

Fixed / Required

Optional

Figure 1-1 MIPS 24KEc Processor

PGMT7620_V.1.0_040503

Page 13 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

1.3 Memory Map Summary

Start

End

Size

Description

0000.0000

-

0FFF.FFFF

256 MBytes

DDR2 256 MB/ DDR1 256 MB/SDRAM 128 MB

1000.0000

-

1000.00FF

256 Bytes

SYSCTL

1000.0100

-

1000.01FF

256 Bytes

TIMER

1000.0200

-

1000.02FF

256 Bytes

INTCTL

1000.0300

-

1000.03FF

256 Bytes

MEM_CTRL (SDR/DDR)

1000.0400

-

1000.04FF

256 Bytes

Rbus Matrix CTRL

1000.0500

-

1000.05FF

256 Bytes

UART

1000.0600

-

1000.06FF

256 Bytes

PIO

1000.0700

-

1000.07FF

256 Bytes

<<Reserved>>

1000.0800

-

1000.08FF

256 Bytes

NAND Controller

1000.0900

-

1000.09FF

256 Bytes

I2C

1000.0A00

-

1000.0AFF

256 Bytes

I2S

1000.0B00

-

1000.0BFF

256 Bytes

SPI

1000.0C00

-

1000.0CFF

256 Bytes

UARTLITE

1000.0D00

-

1000.0DFF

256 Bytes

MIPS CNT

1000.2000

-

1000.27FF

2 KBytes

PCM (up to 16 channels)

1000.2800

-

1000.2FFF

2 KBytes

Generic DMA (up to 64 channels)

1000.3000

-

1000.37FF

2 KBytes

<<Reserved>>

1000.3800

-

1000.3FFF

2 KBytes

<<Reserved>>

1000.4000

-

100F.FFFF

<<Reserved>>

1010.0000

-

1010.FFFF

64 KBytes

Frame Engine

1011.0000

-

1011.7FFF

32 KBytes

Ethernet Swtich

1011.8000

1011.FFFF

32 KBytes

ROM

1012.0000

-

1012.7FFF

32 KBytes

USB Device Control

1012.8000

-

1012.FFFF

32 KBytes

<<Reserved>>

1013.0000

-

1013.3FFF

16 KBytes

SDHC

1013.4000

-

1013.FFFF

48 KBytes

<<Reserved>>

1014.0000

-

1017.FFFF

256 KBytes

PCI Express

1018.0000

-

101B.FFFF

256 KBytes

WLAN BBP/MAC

101C.0000

-

101F.FFFF

256 KBytes

USB Host

1020.0000

-

1023.FFFF

256 KBytes

<<Reserved>>

1024.0000

-

1027.FFFF

256 KBytes

<<Reserved>>

1028.0000

-

1BFF.FFFF

<<Reserved>>

1C00.0000

-

1C00.7FFF

32 KB ROM

When the system is powered on, a 24 KB internal

boot ROM is mapped.

PGMT7620_V.1.0_040503

Page 14 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

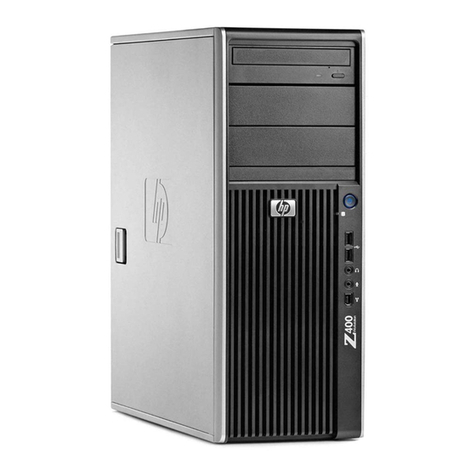

1.4 Clock Plan

BBP PLL

20/40 MHz

CPU PLL

(SSC)

600 MHz

EPHY

20/40 MHz

PCIe PHY (PLL)

USB PHY (TSMC)

12/48 MHz

PLL_PCIe CG

(w/ SSC)

20/40 Mhz

PCIe_CLK (EXT)

EPHY_CLK

125 MHz

PCIe_PHY_CLK

2.5 GHz

DRAM_CLK

/3

/4

/5

20/40 MHz

Xtal in

RF

100 MHz

250 MHz GSW

480 MHz

/12

20/40 MHz

CLK_PERI

(Timer/Uart/I2C/I2S)

20/40 MHz

CPU_CLK

SYS_CLK

OCP_SYNC

/10

48 MHz

/4

12 MHz

PCM_480

20/40 MHz

PCM_240

/2

0

1

0

1

CPU_CLK_AUX0

CPU_CLK_AUX1

PCIe DRV

CLK_SDHC

PLL_CLK *

(1/M)

Figure 1-2 MT7620 Clock Diagram

PGMT7620_V.1.0_040503

Page 15 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

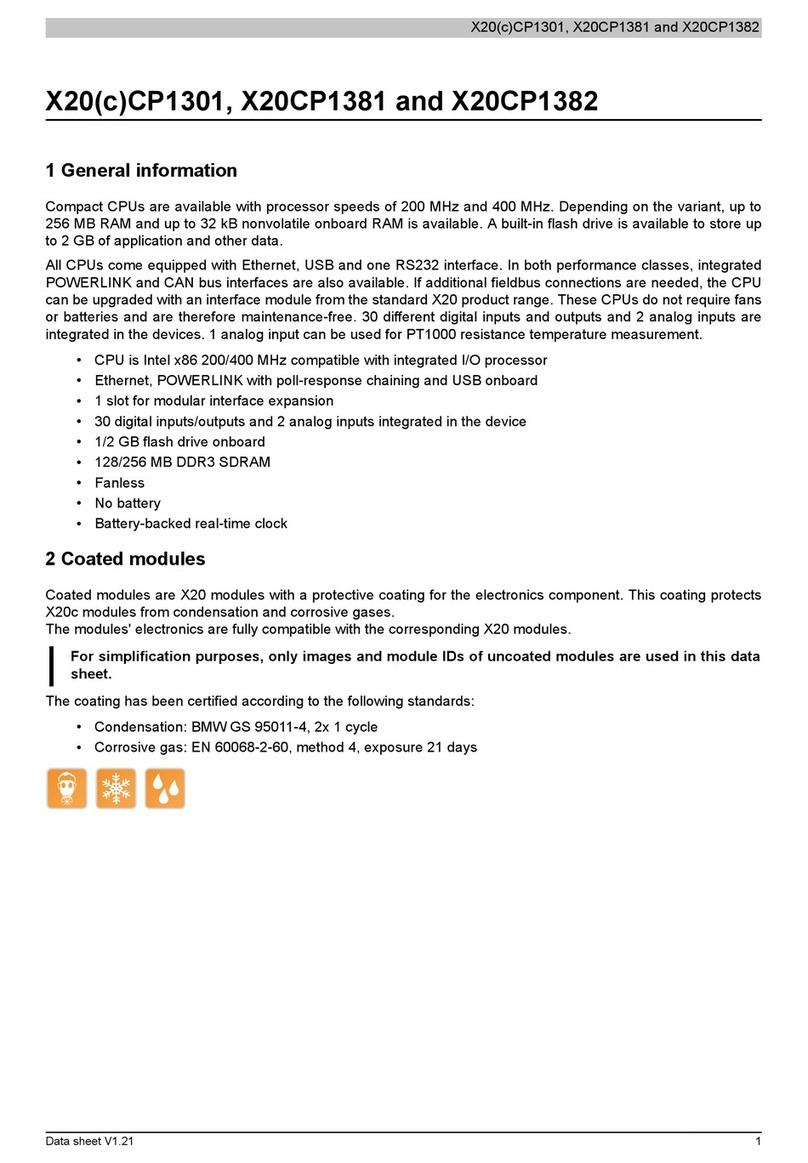

1.5 CPU Clock Mux

BBP

PLL

CPU

PLL

/3

/4

Crystal /2 480 MHz

20/40 MHz

CPU_CLK

SYS_CLK

600 MHz

Fractional

Clock

Generator

DRAM_CLK

CPU_SYS_CLKCFG: (offset: 0x003C)

CPU_CLK_AUX0

CPU_CLK_AUX1

0

1

0

1

CPLL_CFG0: (offset: 0x0054)

CPLL_CFG1: (offset: 0x0058)

Figure 1-3 CPU Clock Mux

PGMT7620_V.1.0_040503

Page 16 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2. Registers

2.1 Nomenclature

The following nomenclature is used for register types:

RO Read Only

WO Write Only

RW Read or Write

RC Read Clear

W1C Write One Clear

- Reserved bit

X Undefined binary value

PGMT7620_V.1.0_040503

Page 17 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.2 System Control

2.2.1 Features

Provides read-only chip revision registers

Provides a window to access boot-strapping signals

Supports memory remapping configurations

Supports software reset to each platform building block

Provides registers to determine GPIO and other peripheral pin muxing schemes

Provides some power-on-reset only test registers for software programmers

Combines miscellaneous registers (such as clock skew control, status register, memo registers, etc)

2.2.2 Block Diagram

System Control

Registers

PalmBus Interface

System Control Block

CPU Rbus Wrapper

Pin Muxing Block

Platform Blocks

PCIe, PCM, ...

Boot Strapping Signals

Cache Hit/Miss Strobes

To/From MIPS

Memory Remapping

GPIO Pin Muxing Scheme

Per Block S/W Reset

Miscellaneous Registers

Figure 2-1 System Control Block Diagram

PGMT7620_V.1.0_040503

Page 18 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.2.3 List of Registers

No.

Offset

Register Name

Description

Page

1

0x0000

CHIPID0_3

Chip ID ASCII Character 0-3

19

2

0x0004

CHIPID4_7

Chip ID ASCII Character 4-7

19

3

0x000C

REVID

Chip Revision Identification

19

4

0x0010

SYSCFG0

System Configuration Register 0

19

5

0x0014

SYSCFG1

System Configuration Register 1

20

6

0x0018

TESTSTAT

Firmware Test Status Register

22

7

0x001C

TESTSTAT2

Firmware Test Status Register 2

22

8

0x0020

Reserved

-

22

9

0x0024

Reserved

-

23

10

0x0028

Reserved

-

23

11

0x002C

CLKCFG0

Clock Configuration Register 0

23

12

0x0030

CLKCFG1

Clock Configuration Register 1

24

13

0x0034

RSTCTRL

Reset Control

25

14

0x0038

RSTSTAT

Reset Status

26

15

0x003C

CPU_SYS_CLKCFG

CPU and SYS Clock Control

27

16

0x0040

CLK_LUT_CFG

Clock Look Up Table Configuration

29

17

0x0044

CUR_CLK_STS

Current clock status

30

18

0x0048

BPLL_CFG0

BB PLL Configuration 0

31

19

0x004C

BPLL_CFG1

BB PLL Configuration 1

31

20

0x0054

CPLL_CFG0

CPU PLL Configuration 0

33

21

0x0058

CPLL_CFG1

CPU PLL Configuration 1

36

22

0x005C

USB_PHY_CFG

USB PHY control

36

23

0x0060

GPIOMODE

GPIO Purpose Select

36

24

0x0064

PCIPDMA_STAT

Control and Status of PDMA in PCIe Device

39

25

0x0088

PMU0_CFG

Power Management Unit 0 Configuration

39

26

0x008C

PMU1_CFG

Power Management Unit 1 Configuration

40

27

0x0098

PPLL_CFG0

PCIe PLL Configuration 0

41

28

0x009C

PPLL_CFG1

PCIe PLL Configuration 1

43

29

0x00A0

PPLL_DRV

PCIe Driver Configuration

44

PGMT7620_V.1.0_040503

Page 19 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.2.4 Register Descriptions (base: 0x1000_0000)

1. CHIPID0_3: Chip ID ASCII Character 0-3 (offset: 0x0000)

Bits

Type

Name

Description

Initial Value

31:24

RO

CHIP_ID3

ASCII CHIP Name Identification Character 3

0x36

23:16

RO

CHIP_ID2

ASCII CHIP Name Identification Character 2

0x37

15:8

RO

CHIP_ID1

ASCII CHIP Name Identification Character 1

0x54

7:0

RO

CHIP_ID0

ASCII CHIP Name Identification Character 0

0x4D

2. CHIPID4_7: Chip Name ASCII Character 4-7 (offset: 0x0004)

Bits

Type

Name

Description

Initial Value

31:24

RO

CHIP_ID7

ASCII CHIP Name Identification Character 7

0x20

23:16

RO

CHIP_ID6

ASCII CHIP Name Identification Character 6

0x20

15:8

RO

CHIP_ID5

ASCII CHIP Name Identification Character 5

0x30

7:0

RO

CHIP_ID4

ASCII CHIP Name Identification Character 4

0x32

3. REVID: Chip Revision Identification (offset: 0x000C)

Bits

Type

Name

Description

Initial Value

31:17

-

-

Reserved

0x0

16

RO

PKG_ID

Package ID

0: DRQFN-148 pin

1: TFBGA-269 ball

NOTE: This value is determined by the package

used.

-

15:12

-

-

Reserved

0x0

11:8

RO

VER_ID

Chip Version Number

0x2

7:4

-

-

Reserved

0x0

3:0

RO

ECO_ID

Chip ECO Number

0x1

4. SYSCFG0: System Configuration Register 0 (offset: 0x0010)

Bits

Type

Name

Description

Initial Value

31:24

RW

TEST_CODE

Test Code

Default value is from bootstrap and can be

modified by software.

0x0

23

-

-

Reserved

0x0

22:12

RO

BS_SHADOW

BS shadow register for last boot-up value

Displays a backup copy of the last bootup value.

BS

11:9

-

-

Reserved

0x0

PGMT7620_V.1.0_040503

Page 20 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

Bits

Type

Name

Description

Initial Value

8

RO

DRAM_FROM_EE

DRAM Configuration from EEPROM

0: DRAM/PLL configuration from EEPROM.

1: DRAM configuration from Auto Detect.

For more information see the Bootstrapping

Pins Description in the datasheet for this chip.

BS

7

RO

DBG_JTAG_MODE

Debug JTAG Mode

0: EPHY_LED

1: JTAG MODE

BS

6

RO

XTAL_FREQ_SEL

Xtal Frequency Select

0: 20 MHz

1: 40 MHz

BS

5:4

RO

DRAM_TYPE

DRAM Type

0: SDRAM (150 MHz) (LVTTL 3.3 V) TSOP

Package

1: DDR1 (200 MHz) TSOP Package

2: DDR2 (200 MHz) FBGA Package

BS

3:0

RO

CHIP_MODE

Chip Mode

A vector to set chip function/test/debug modes

in non-test/debug operation.

For more information see the Bootstrapping

Pins Description in the datasheet for this chip.

BS

5. SYSCFG1: System Configuration Register 0 (offset: 0x0014)

Bits

Type

Name

Description

Initial Value

31:30

-

-

Reserved

-

29:28

RW

DDR_DPIN_RXPWD

SDRAM Data Pin Receiver Circuit Power Down

Control*

(DQ/DQS)

0: Disable (SDR/DDR1/DDR2 default)

1: Enable

2: Enable while data pin is output mode.

3: Enable while data pin is input mode.

BS

27:26

RW

DDR_DPIN_ODT

SDRAM Data Pin On Die Termination Setting*

(DQ/DQS)

[27:26]

SDR

(3.3 V)

SDR

(2.5 V/

1.8 V)

DDR1

DDR2

0

(Disable)

(Disable)

(Disable)

(Disable)

1

75 Ω

75 Ω

75 Ω

75 Ω

2

150 Ω

150 Ω

150 Ω

150 Ω

3

N/A

N/A

N/A

N/A

BS

Table of contents

Other MEDIATEK Computer Hardware manuals

Popular Computer Hardware manuals by other brands

Renesas

Renesas R-IN32M4-CL2 TESSERA user manual

Arduino

Arduino ASX00049 Product reference manual

Supero

Supero BPN-SAS2-216EL1 user guide

Panasonic

Panasonic AJ-PCD35P operating instructions

Synology

Synology DS1813+ technical information

Flann Microwave

Flann Microwave 600 Series Operation and maintenance manual