Panasonic CQC8305U - AUTO RADIO/CD DECK User manual

Other Panasonic Car Receiver manuals

Panasonic

Panasonic CQ-VW220W User manual

Panasonic

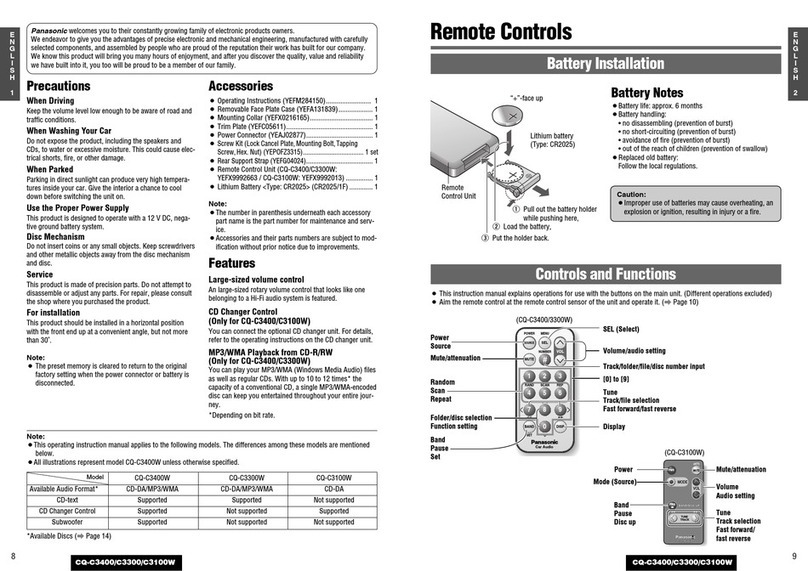

Panasonic CQ-C3305W User manual

Panasonic

Panasonic CQC1303U - AUTO RADIO/CD DECK Setup guide

Panasonic

Panasonic CR-W402UA User manual

Panasonic

Panasonic PP103914 User manual

Panasonic

Panasonic CQ-FX721N User manual

Panasonic

Panasonic CQDVR592U - AUTO RADIO/CD/DVD PL User manual

Panasonic

Panasonic CQ-E01EN User manual

Panasonic

Panasonic CQ-FX321N User manual

Panasonic

Panasonic CQ-MR500N User manual

Panasonic

Panasonic PalmTheater DVD-LV70 User manual

Panasonic

Panasonic CQDP171U - AUTO RADIO/CD DECK User manual

Panasonic

Panasonic C7113U User manual

Panasonic

Panasonic CQVD6505U - IN-DASH DVD MONITOR User manual

Panasonic

Panasonic CQ-HX2083U User manual

Panasonic

Panasonic CQ4300U - AUTO RADIO/CD TRUCK User manual

Panasonic

Panasonic CQ2500CEU - AUTO RADIO/CASSETTE User manual

Panasonic

Panasonic CQ-DVR7000U User manual

Panasonic

Panasonic C5303U User manual

Panasonic

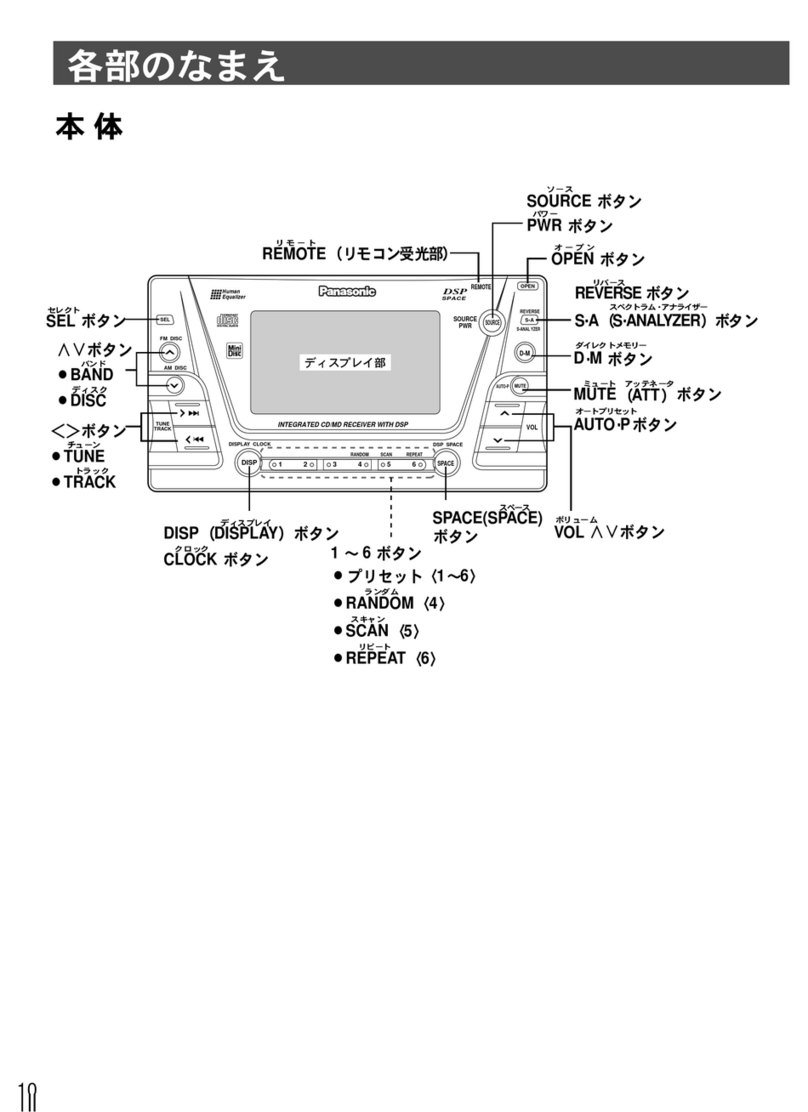

Panasonic DSP Space User manual