2-1

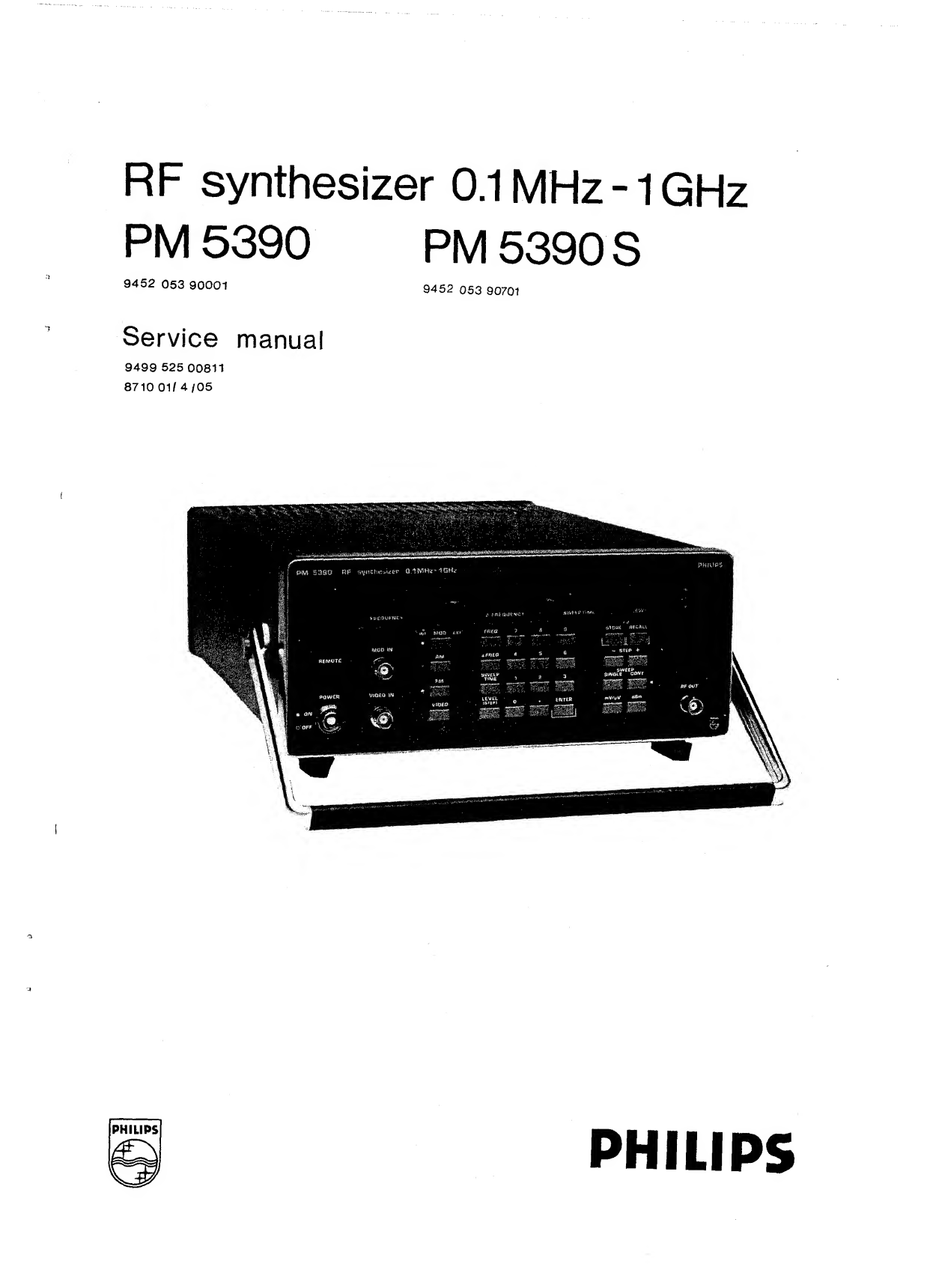

2. OPERATING PRINCIPLE

2.1. basic PRINCIPLE OF OPERATION, fig. 30 a

The operation of the PM 5390 1GHz RF synthesizer is based on the principle of indirect synthesis;

frequencies are generated by VCOs (Voltage Controlled Oscillators) in digital Phase-Locked Loops

(PLL).

Four of the six frequency ranges -for frequencies from 340 to 1020 MHz- are generated by the maid

oscillator VCO la ... Id. Mixer oscillators VCO 2a and 2b generate 4fixed frequencies for mixing

with the corresponding 4frequency ranges of the main oscillator.

The two lower frequency ranges from 0.1 to 340 MHz are generated by mixing VCO la or VCO

(assisted by VCO 2just mentioned) with the fixed 510 MHz frequency of VCO 3. For this the output

signal is switched to mixer 2.

All 3oscillators VCO 1, VCO 2and VCO 3are related to the 5MHz X-tal reference oscillator .

Frequency control operates by comparing the output signal from VCO 1, mixed with the relevant

frequency generated by oscillator VCO 2, with asignal from the reference oscillator. Both signals are

divided down to 1kHz -the reference signal by afixed reference divider and the output signal by a

programmable divider controlled via ports by the microprocessor.

Also in phase-locked loop 2the frequency is controlled via ports by setting the division factor of divider

2, in this case to 4values for the 4fixed frequencies.

Frequency synthesizer HEF 4750 and programmable divider 1, HEF 4751, are two ICs matched to each

other. Divider 1provides a'fast output' FF to allow fast frequency locking and a'slow output' FS which

is used for fine phase control.

2.2. description OF THE BLOCK DIAGRAM, fig. 30

The instrument works under control of the 8085 microprocessor within the central processing unit,

CPU. The program memory consists of two EPROMs. On the data memory chip two further functions

are implemented, i.e. atimer,generating sweep control signals, and 12 output ports for the modulation

modes on the modulation interface. In the long-term data memory up to 8complete parameter settings

of the instrument can be stored and recalled. For this the BATTERY switch at the rear panel must be

set to '1' (ON). The low-power CMOS RAM is backed-up by aNiCd battery pack. It ensures storage

after mains switch off or in case of mains failure. Ports 2and 3on unit 2and port 1on unit 1control

all circuitries on the various units.

The keyboard/display unit 5contains all display elements and switches (keys). Together with unit 4

it forms asandwich pack. The central circuit on the kevboard/display interface unit 4is the micropro-

cessor controlled keyboard controller. This interface component produces the scan signals for the key-

board matrix and picks up the return lines, sends the data information for the 7-segment displays and

controls the multiplex lines for the display positions.

The IEC bus interface is built-up in standard configuration. The data, transfer control and management

signals are transferred via aflat cable from the IEEE bus connector on the small unit 6at the rear

of the instrument to the interface. The address switches are also attached to the small rear unit.

The operating principle of the oscillators VCO 1.VCO 2and VCO 3was already described in the pre-

vious chapter 2.1. The output of the main oscillator VCO 1is fed to the automatic level control. Afn-

plitude modulation can be added after this stage. Video modulation is also applied here.