Philips Semiconductors Product specification

SA70161.3GHz low voltage fractional-N synthesizer

1999 Nov 04 9

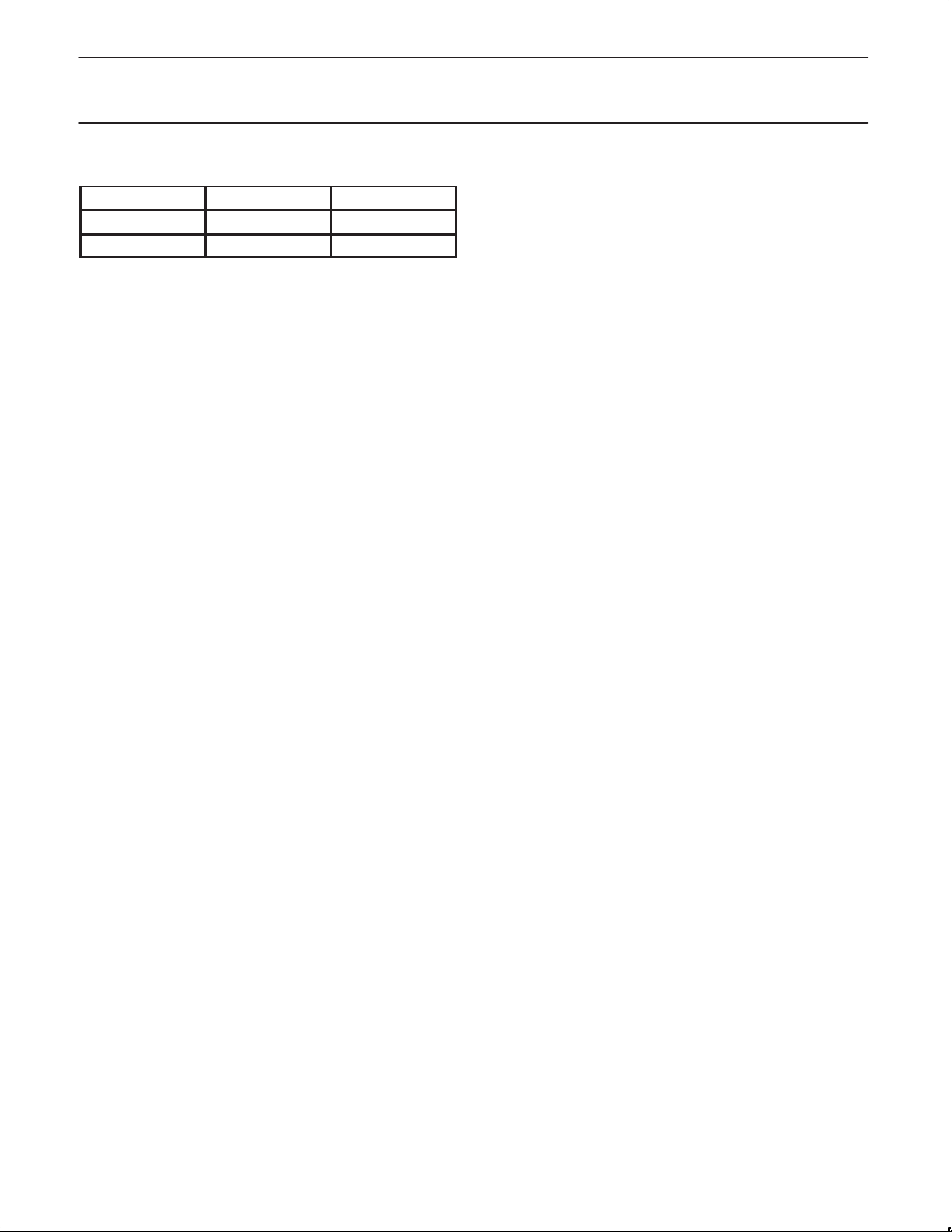

Main Output Charge Pumps and Fractional

Compensation Currents (see Figure 6)

The main charge pumps on pins PHP and PHI are driven by the

main phase detector and the charge pump current values are

determined by the current at pin RSET in conjunction with bits CP0,

CP1 in the B-word (see table of charge pump ratios). The fractional

compensation is derived from the current at RSET, the contents of

the fractional accumulator FRD and by the program value of the

FDAC. The timing for the fractional compensation is derived from

the main divider. The main charge pumps will enter speed up mode

after the A-word is set and strobe goes High. When strobe goes

Low, charge pump will exit speed up mode.

Principle of Fractional Compensation

The fractional compensation is designed into the circuit as a means

of reducing or eliminating fractional spurs that are caused by the

fractional phase ripple of the main divider. If ICOMP is the

compensation current and IPUMP is the pump current, then for each

charge pump:

IPUMP_TOTAL = IPUMP + ICOMP.

The compensation is done by sourcing a small current, ICOMP, see

Figure 7, that is proportional to the fractional error phase. For proper

fractional compensation, the area of the fractional compensation

current pulse must be equal to the area of the fractional charge

pump ripple. The width of the fractional compensation pulse is fixed

to 128 VCO cycles, the amplitude is proportional to the fractional

accumulator value and is adjusted by FDAC values (bits FC7–0 in

the B-word). The fractional compensation current is derived from the

main charge pump in that it follows all the current scaling through

external resistor setting, RSET, programming or speed-up operation.

For a given charge pump,

ICOMP = ( IPUMP / 128 ) * ( FDAC / 5*128) * FRD

FRD is the fractional accumulator value.

The target values for FDAC are: 128 for FMOD = 1 (modulo 5) and

80 for FMOD = 0 (modulo 8).

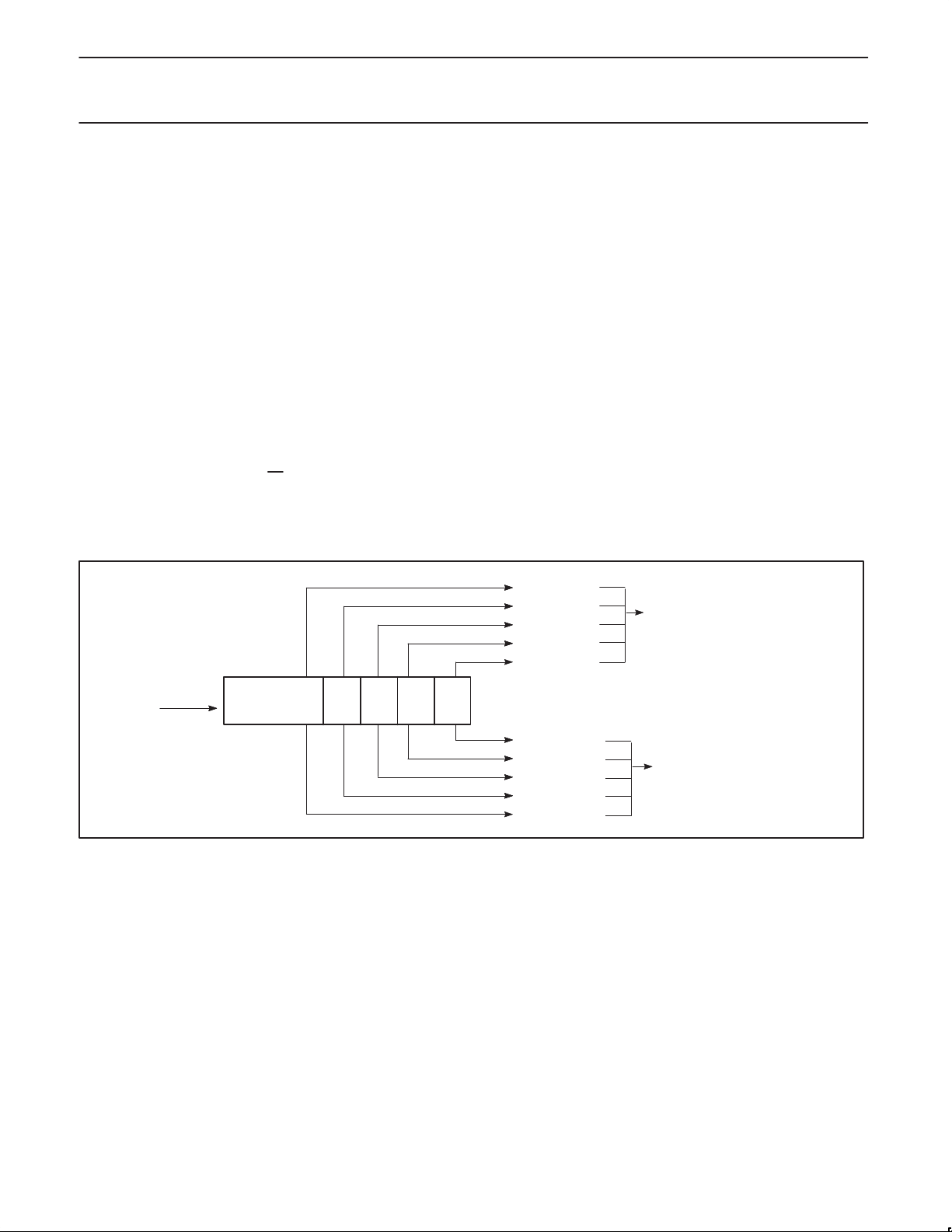

SR01416

REFERENCE R

MAIN M

DIVIDE RATIO

DETECTOR

OUTPUT

ACCUMULATOR

FRACTIONAL

COMPENSATION

CURRENT

OUTPUT ON

PUMP

N N N+1 N N+1

241

30

PULSE

WIDTH

MODULATION

PULSE LEVEL

MODULATION

mA

µA

NOTE: For a proper fractional compensation, the area of the fractional compensation current pulse must be equal to the area of the charge pump ripple output.

Figure 6. Waveforms for NF = 2 Modulo 5 →fraction = 2/5

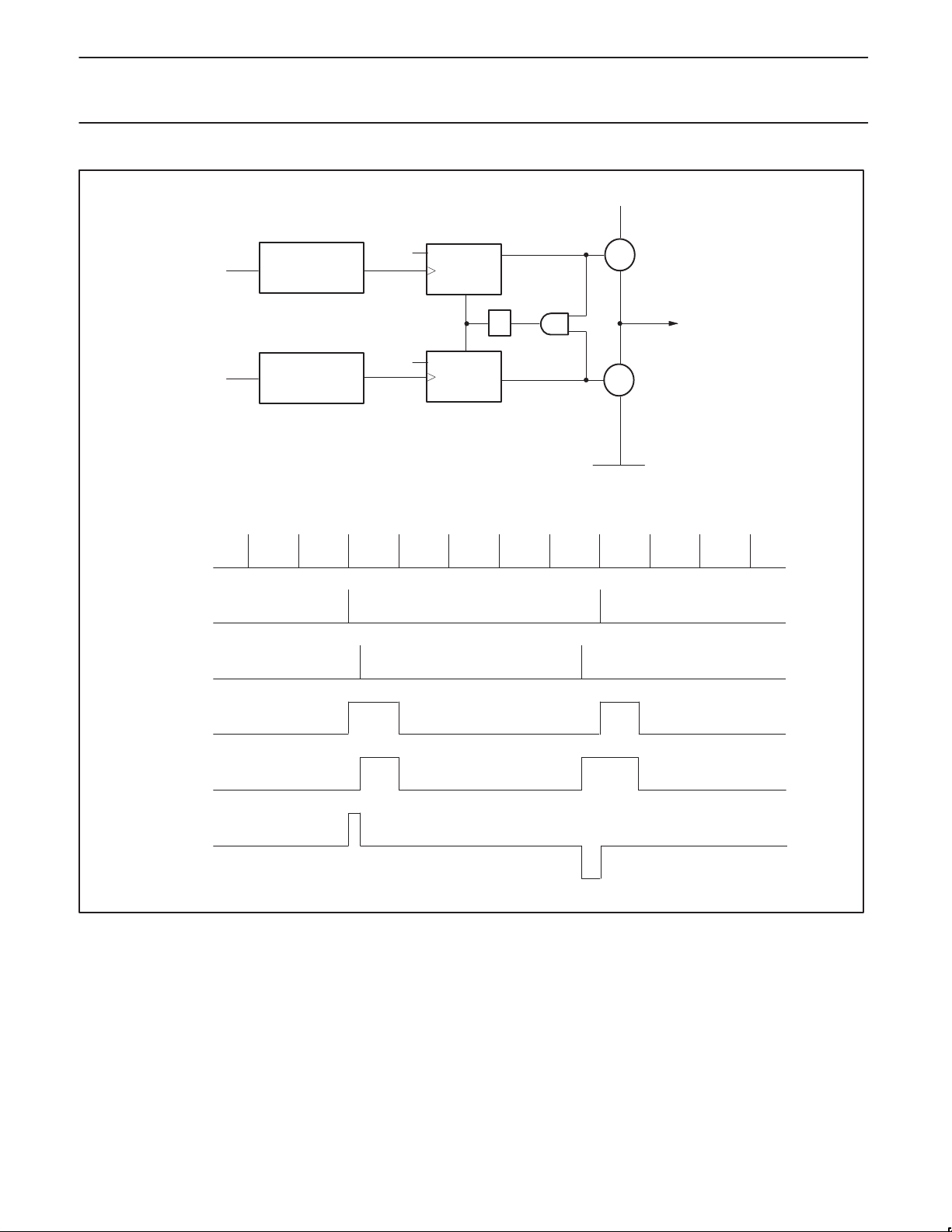

SR01682

fRF

1930.140 MHz MAIN DIVIDER

N = 8042 FRACTIONAL

ACCUMULATOR

fREF

240 kHz

240.016 kHz ICOMP

IPUMP LOOP FILTER

& VCO

FMOD

NF

Figure 7. Current Injection Concept