1

Introduction

The PLECS RT Box is a powerful real-time simulator based on a Xilinx Zynq

system on a chip (SOC). With its digital and analog I/O signals, the RT Box is

well-equipped for hardware-in-the-loop (HIL) testing as well as rapid control

prototyping (RCP).

If employed for HIL testing, the RT Box typically emulates the power stage

of a power electronic system. The power stage could be a simple DC/DC con-

verter, an AC drive system or a complex multi-level inverter system. The de-

vice under test (DUT) is the control hardware connected to the RT Box. In

such a setup, the complete controller can be tested without the real power

stage.

To simplify the connection of external hardware and to provide convenient ac-

cess to the RT Box inputs and outputs, Plexim offers a set of RT Box acces-

sories.

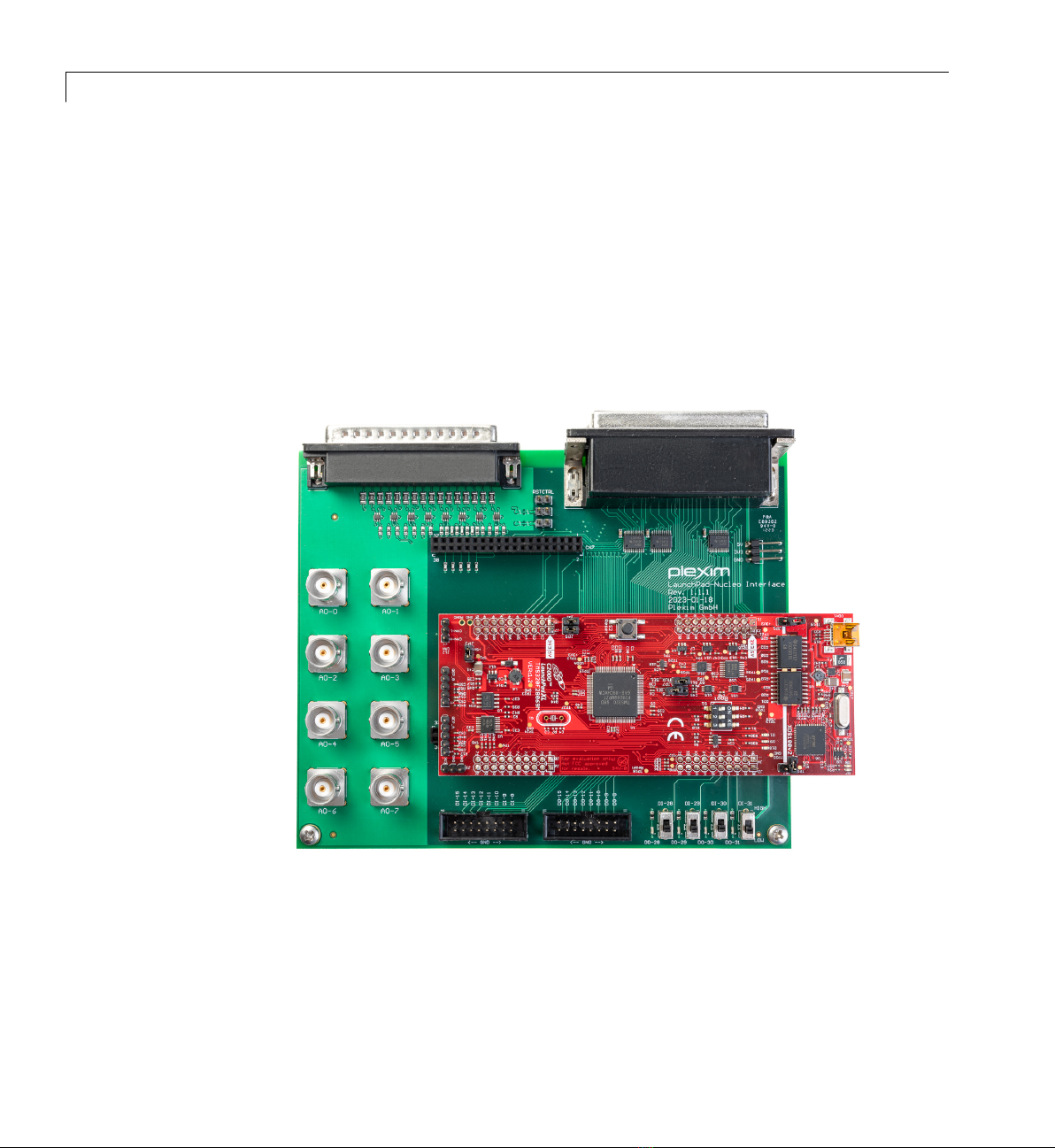

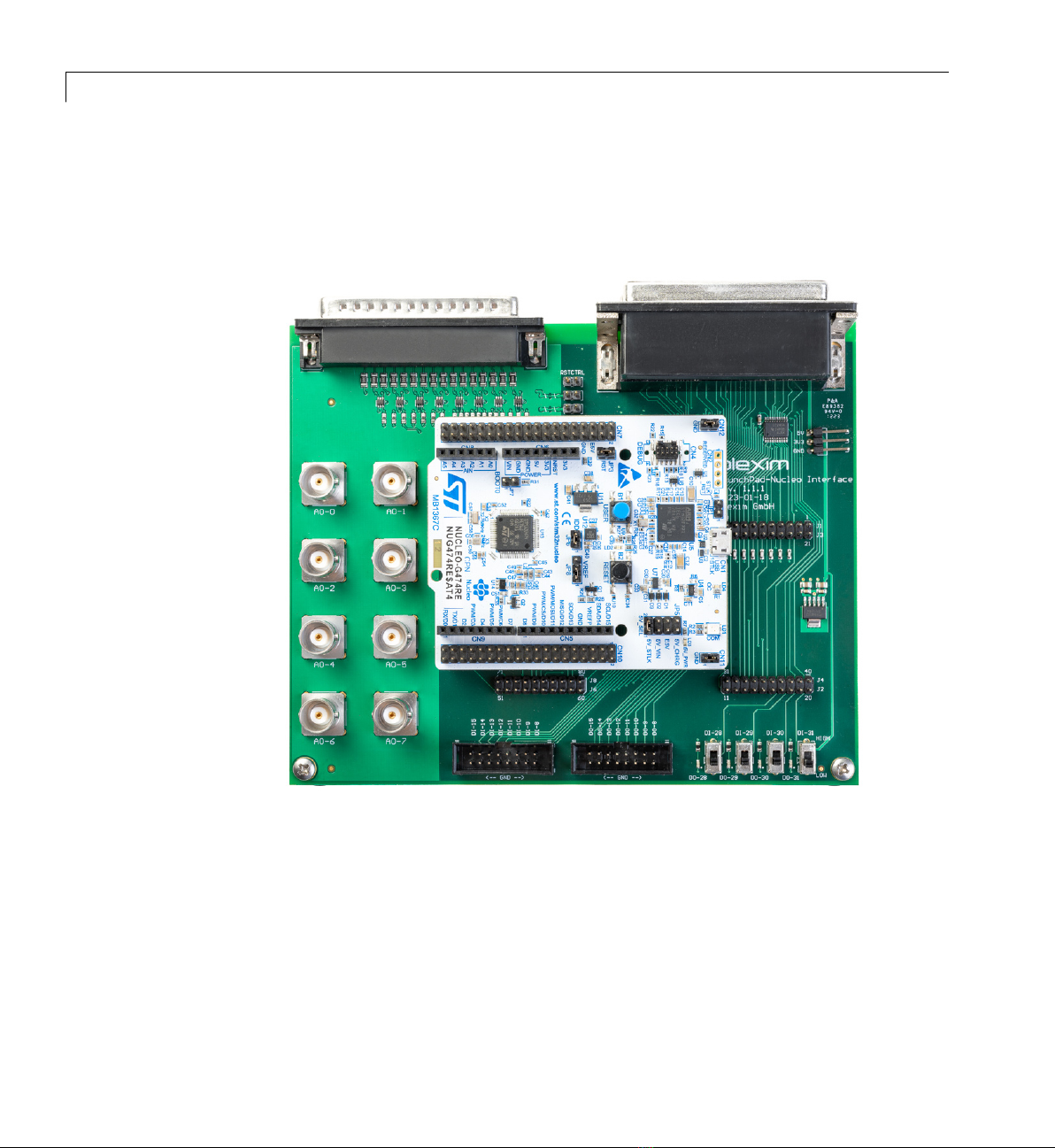

The RT Box LaunchPad-Nucleo Interface described in this document fa-

cilitates a simple connection of the RT Box with the LaunchPad or Launch-

Pad XL development kits from Texas Instruments, and Nucleo-64 development

boards from STMicroelectronics. It enables the user to test control algorithms

implemented on TI C2000 and STM32 MCUs without developing their own

interface hardware. The pinout of the LaunchPad-Nucleo Interface board has

been optimized for the following boards:

TI C2000 LaunchPads:

• LaunchXL-F280039C

• LaunchXL-F280049C

• LaunchXL-F28069M

• LaunchXL-F28377S

• LaunchXL-F28379D

• LaunchXL-F28027