NAR-5620 Series User’s Manual 1

Table of Contents

Chapter 1 Introduction...........................................................................................................2

1.1 About This Manual ..........................................................................................................2

1.2 Manual Organization.......................................................................................................2

1.3 Technical Support Information.........................................................................................2

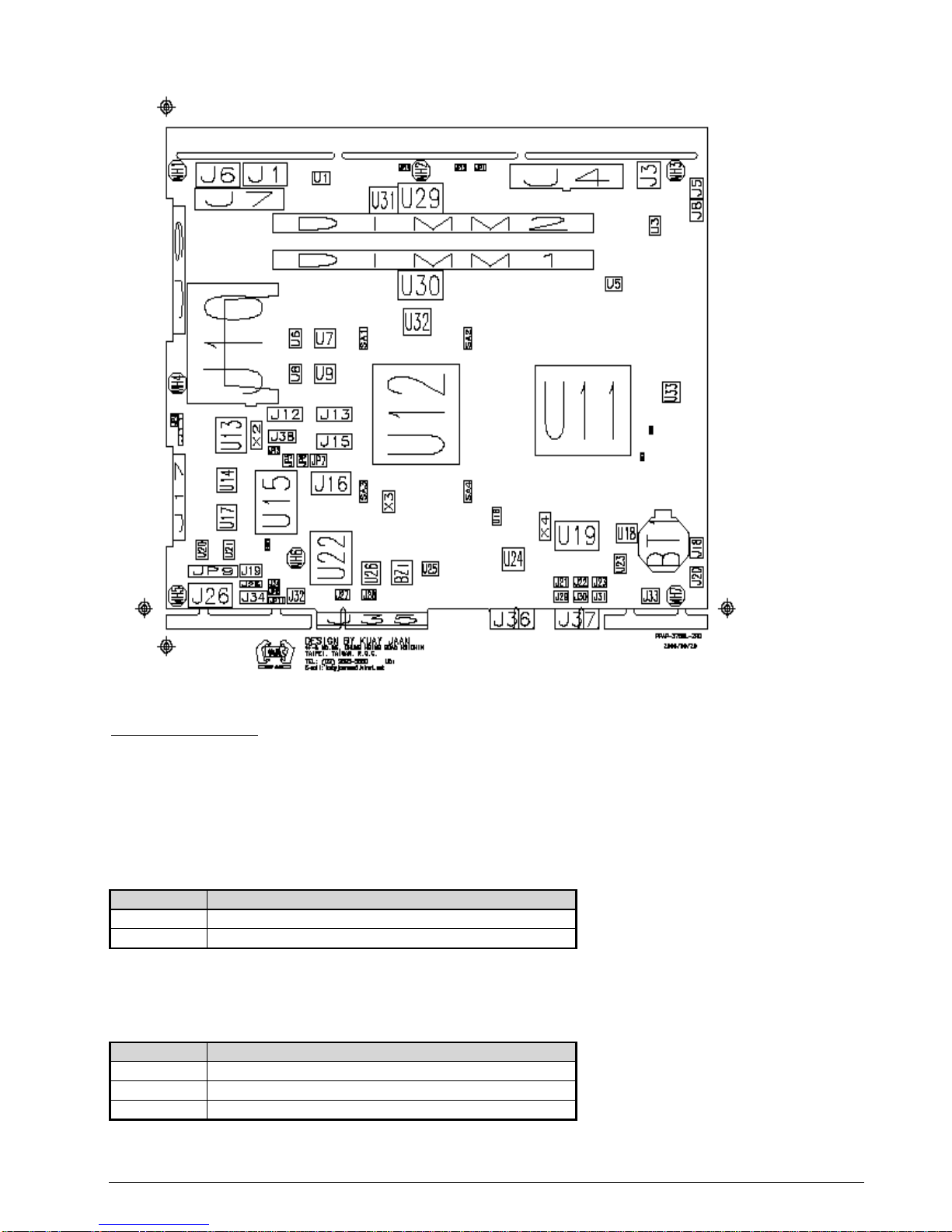

1.4 Board Layout...................................................................................................................3

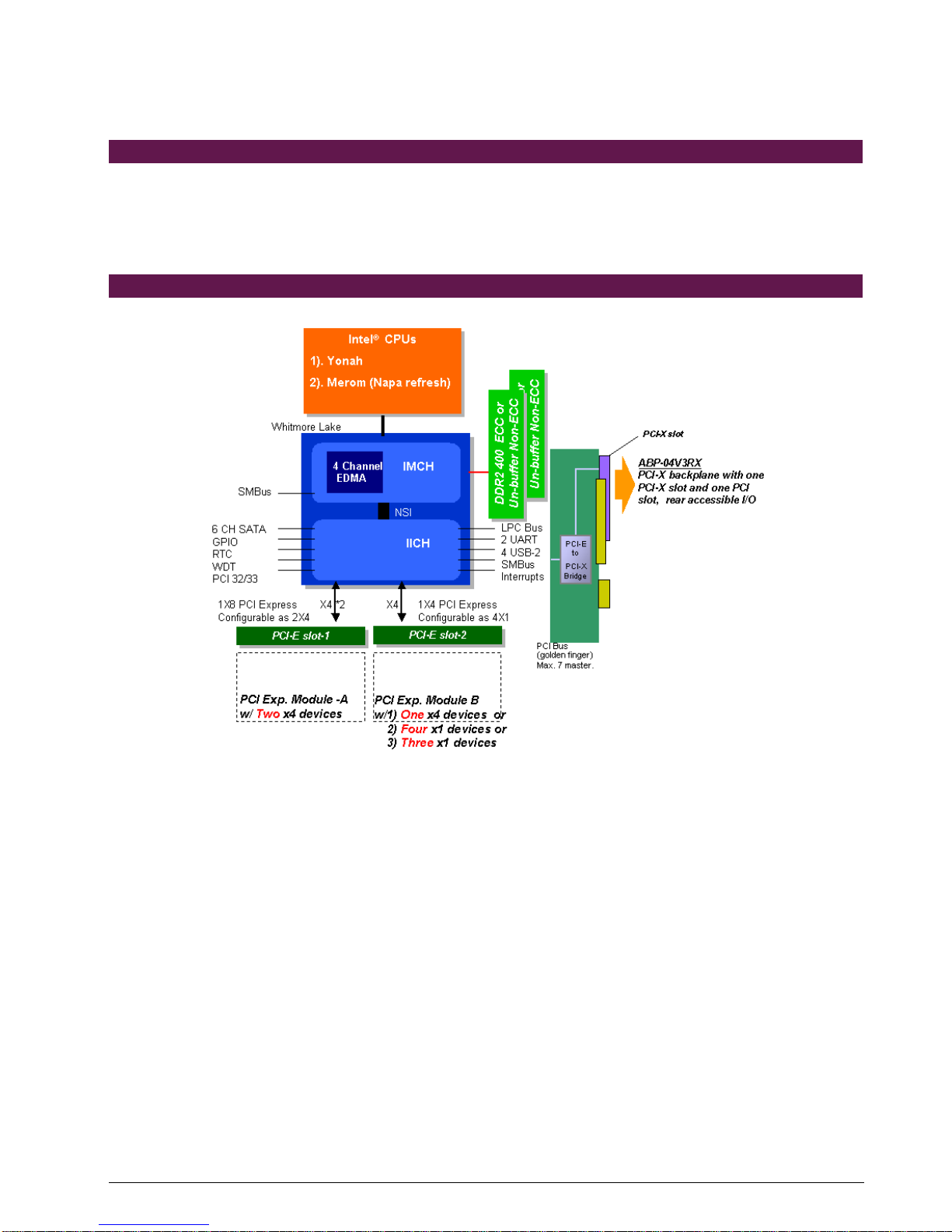

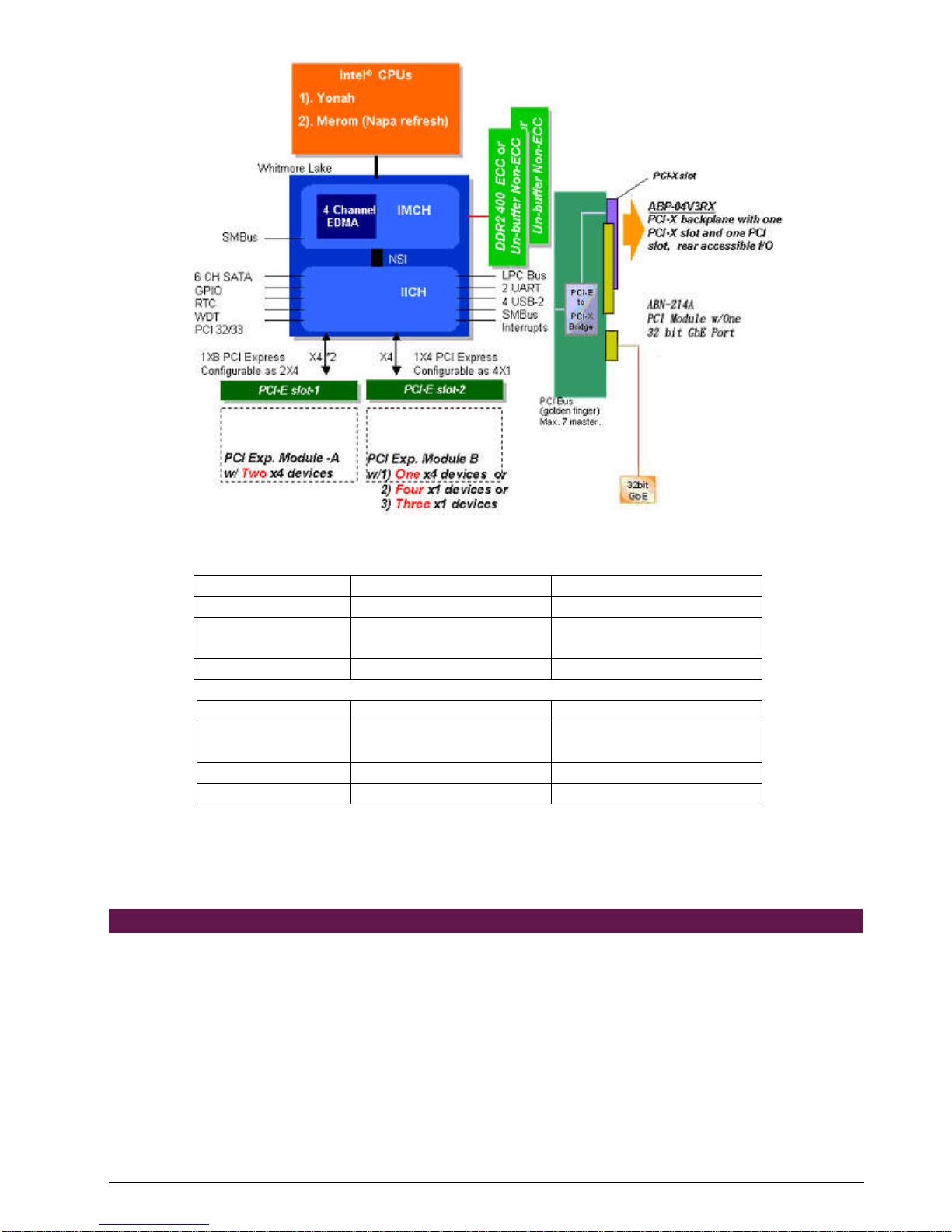

1.5 System Block Diagram....................................................................................................3

1.6 Product Specifications...............................................................................................................4

Chapter 2 Getting Started ....................................................................................................5

2.1 Included Hardware..........................................................................................................5

2.2 Before You Begin............................................................................................................5

2.3 Hardware Configuration Setting.......................................................................................6

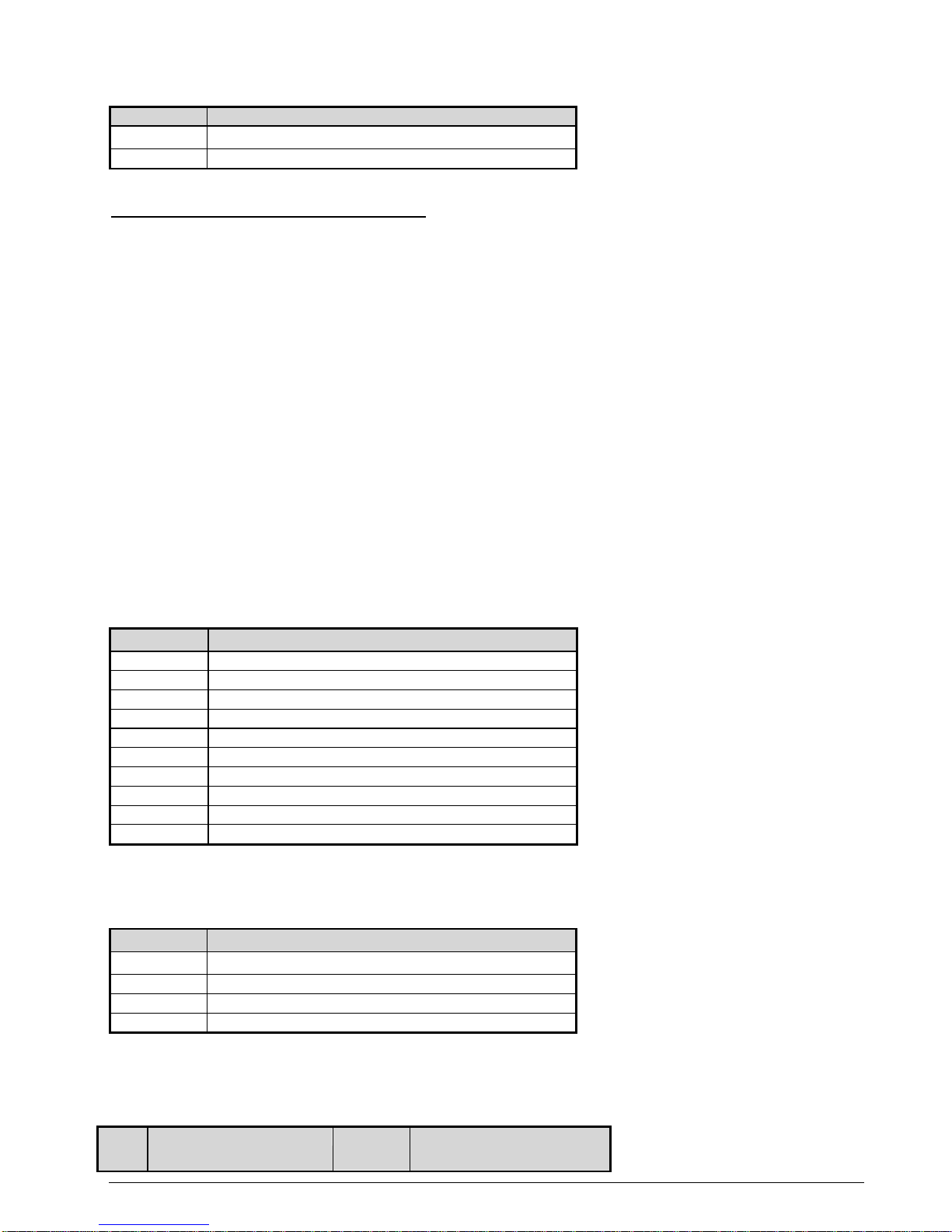

h Location of Jumpers.........................................................................................................................6

2.4 The Chassis..................................................................................................................13

2.12 Use a Client Computer..................................................................................................14

Chapter 3 BIOS Setting .................................................................................................17

BIOS Setup Information .....................................................................................................................17

Chapter 4 Programming Guide..........................................................................................17

4.1 Reset to Default Information..........................................................................................17

4.2 ByPass WDT Programming Guide ...............................................................................38

4.3 About EZIO2 .................................................................................................................38

4.3.1 Features .....................................................................................................................38

4.3.2 Technical Support Information.......................................................................................39

4.3.3 Mechanical Specification...............................................................................................39

4.3.4 General Specification....................................................................................................39

4.3.5 Product Outlook ............................................................................................................40

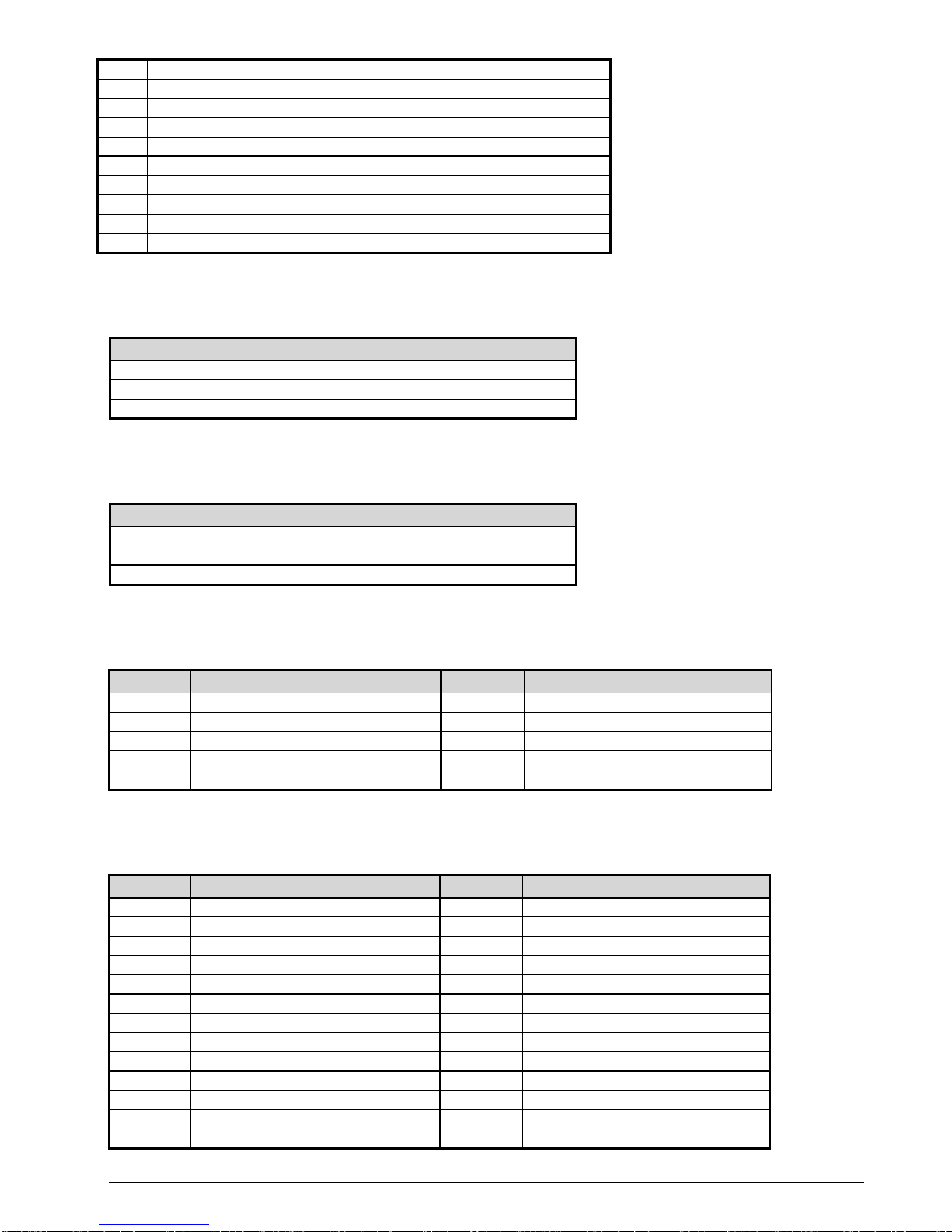

4.3.6 Interface Pin Assignment...............................................................................................40

4.3.7 Hardware installation.....................................................................................................41

4.3.8 EZIO3 Function Command............................................................................................41

4.3.9 Character Generator ROM (CGROM)........................................................................................44

4.3.10 Sample Codes...............................................................................................................45

4.4 GPIO Sample Code......................................................................................................51