R15UZ0002EU0100 Rev.1.00 Page 3

Oct 6, 2021

RTKA788152DE0000BU Evaluation Board Manual

1. Functional Description

1.1 Operational Characteristics

1.1.1 Driver Operation

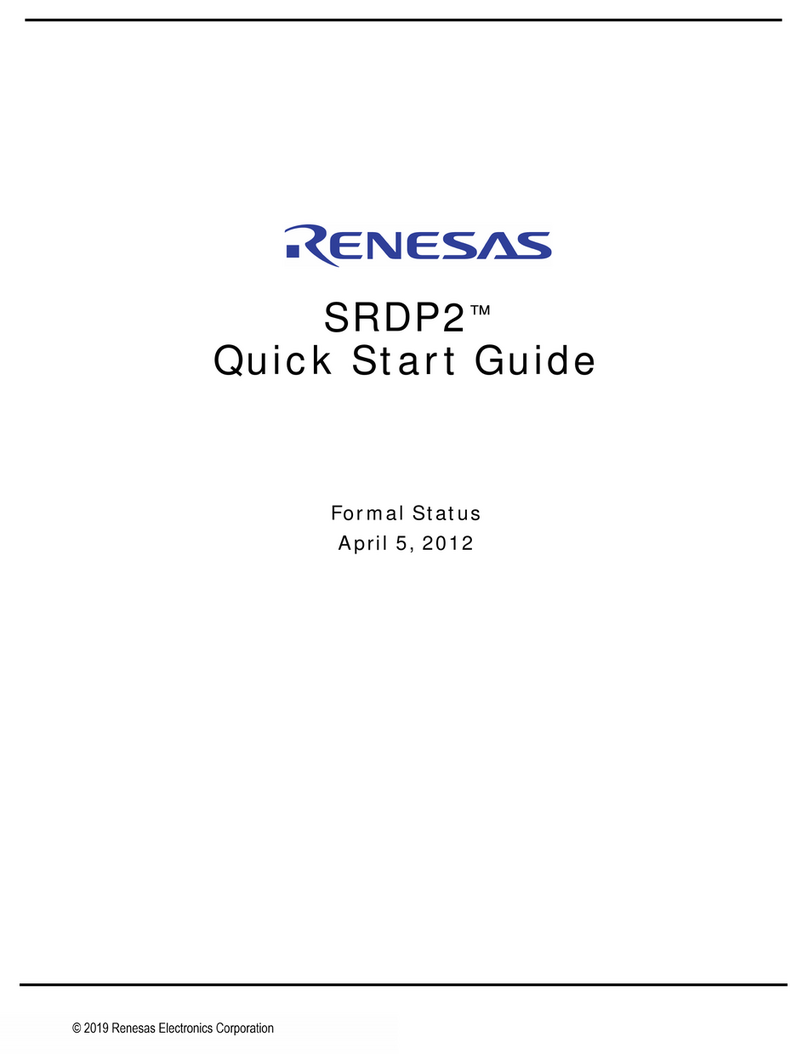

A logic high at the driver enable pin (DE) activates the driver and causes the differential driver outputs (Y and Z) to

follow the logic states at the data input (DI). A logic high at DI causes Y to turn high and Z to turn low. In this case,

the differential output voltage, defined as VOD = VY– VZ, is positive. A logic low at DI reverses the output states

reverse, turning Y low and Z high, therefore, making VOD negative. A logic low at DE disables the driver, making Y

and Z high-impedance. In this condition, the logic state at DI is irrelevant. To ensure the driver remains disabled

after device power-up, Renesas recommends connecting DE through a 1kΩto 10kΩpull-down resistor to ground.

1.1.2 Receiver Operation

A logic low at the receiver enable pin (RE) activates the receiver and causes its output (RO) to follow the bus

voltage at the differential receiver inputs (A and B); the bus voltage is defined as VAB = VA- VB. For VAB ≥-0.05V,

RO turns high, and for VAB ≤-0.2V, RO turns low. For input voltages between -50mV and -200mV, the state of RO

is undetermined, and therefore can be high or low. A logic high at RE disables the receiver, making RO high-

impedance. In this condition, the polarity and magnitude of the input voltage is irrelevant. To ensure the receiver

output remains high when the receiver is disabled, Renesas recommends connecting RO, using a 1kΩto 10kΩ

pull-up resistor to VCC. To enable the receiver to immediately monitor the bus traffic after device power- up,

connect RE through a 1kΩto 10kΩpull-down resistor to ground.

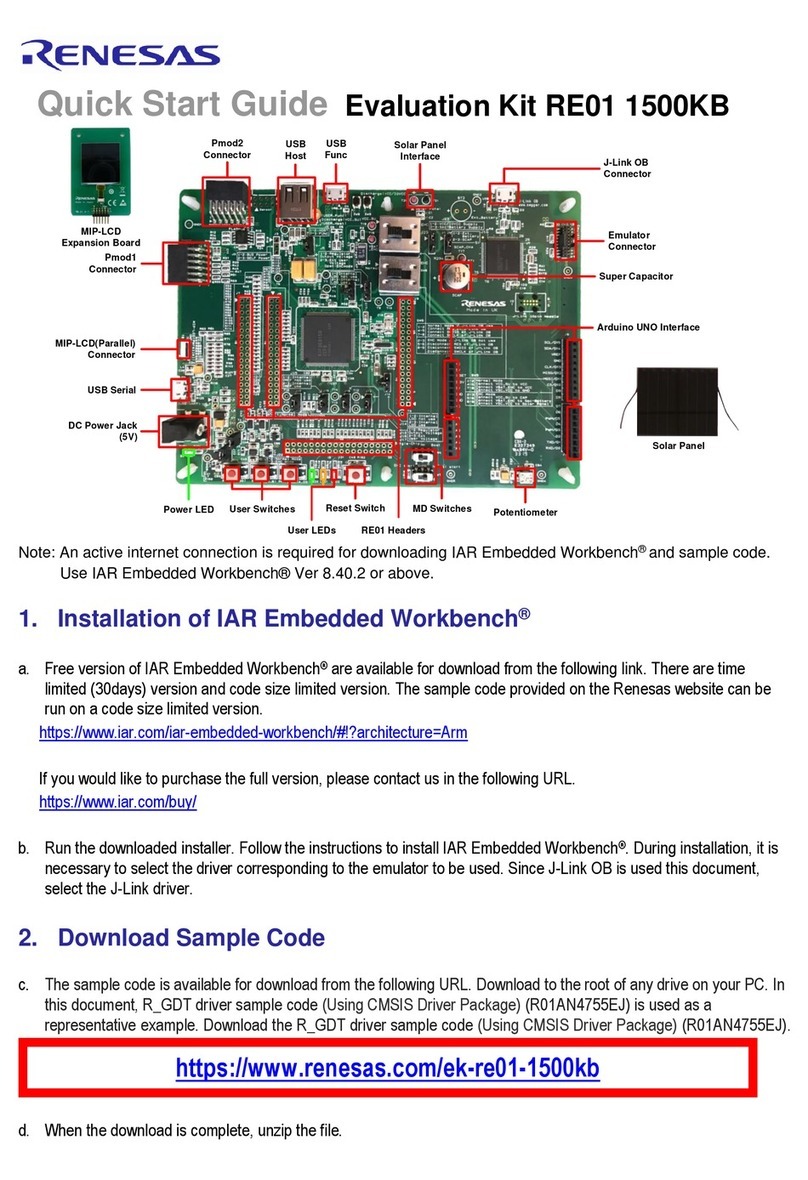

Figure 2. Typical Operating Circuits of Half-Duplex and Full-Duplex Transceivers

Table 1. Driver Truth Table

Inputs Outputs

FunctionRE DE DI Y Z

X H H H L Actively drives bus high

X H L L H Actively drives bus low

L L X Z Z Driver disabled, outputs high-impedance

H L X Z Z Shutdown mode: driver and receiver disabled for more than 600ns

A

B

RO

DE

DI

R

D

RT

GND

VCC

RE

5V

10k

10k 10k

RL78

MCU Y

Z

100n

RB

(option al)

RB

(option al)

A/Y

B/Z

RO

DE

DI

R

D

RT

GND

VCC

RE

5V

10k

10k 10k

RL78

MCU

100n

RB

(option al)

RB

(option al)