CIRCUIT DESCRIPTION

JAN.13,1982

CPU BOARD

when CPU is initialized with power-on RESET signgi, it wants to read

operational program (software -instruction) stored at address (QOOOJi*

to starts controlling the MC-4.

With Os on the addreES bus [All A15) and MREQ, ROM Address

Decoder IC60 selects ROM [a] IC36 which in turn transfers data from

accessed memory cells to DO D7. CPU proceeds steps with fetch&d'

instruction.

The following Is one of steps wilt be done.

(1) To transfer d9ta to or fronn RAMs

(2) To transfer data to or from I/O ports or Programmable Tinner

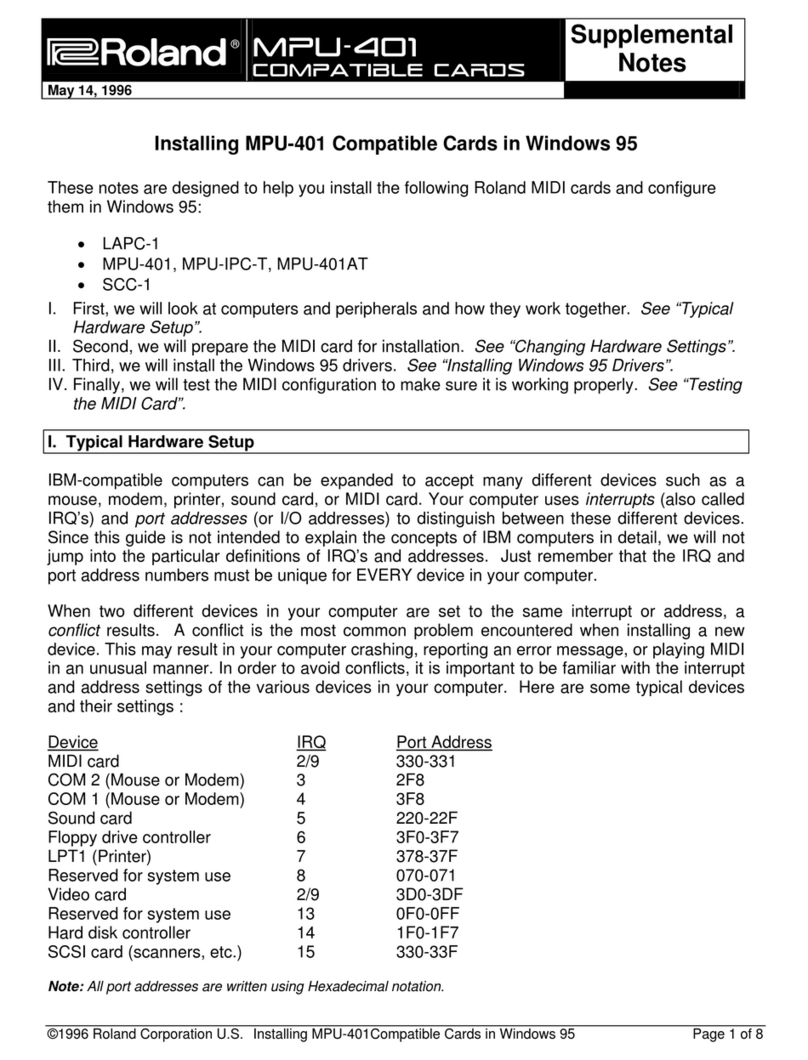

ADDRESS MAP

ft _l

Ti l^ Tj

AO~/^lS^ 1IC 1fi.Zli

MJltfl "

WJ'

WA3T „.J U.

SiT -1J

r^ 1

vSi^

0000

27P?

ROM0 IC56

ROM AREA

IlOMjYj IQYd

BLAHE

4000 ICl-ICS

(CPU BOARD)

Rjm AREA

ICl-ICS

(RAM BOARD)

(RAM BOAED)

6000

cooo

{1> Accessing 1o HAMS ICl-IGS

The CPU places RAM address onto Address bus, then outputs necessary

signals as shown in Fig, 2.

Eight 16K Xtbit RAMs are connected in parallol to form a16K )c8 bit ^

RAM block. The 14 address bits required to decode 1of the 16,384 cell a9-xU

locations within M5K4T15 are multlptexed onto 7address inputs ICffifq

(A0-A6-) of RAMs, First, low&r order 7bits ara fad to RAM$ through f^

RAM Address Multiplexers (I C9 and ICl 1)and latched Into the RAMs'

on-chip ,gddres5 latches by HAS. Second, higlier order 7bits ara fed to "^

the RAMs when SEL pins of IC9 and IC11 go Sow by the delayed t]o~dt

MREQ coming th roughpjn 8of fC12. Thess 7bits are latched into wait

RAMs' chips with CAS fed via RAM Address Decoders (iCTOand IC12),

and an acGes to RAMs completes. Data are stored into selected cells by

acombination of WRITE and CAS, qr re^trieved from the memories

in aread cycle in which CAS is actJ'vt low.

OJk CONVERTER

The digital outputs from the PORT Aof INTE RFACE \\C29| are level-

shifted by the transistors {TR5-TR11), pa$s through the CMOS

INVERTERS (IC27, !C2a), and undergo addition by the weighing

resistors to become an analog voltage. Since the MC-4 has eight CVe,'

eighi data are sampled in the tine sharing system by the 4051 DMPX

!IC46^h?|[Jbythe 081 (IC47-fC54] and output to the output jacks.

The resolution of the D/A converter is 1/'12V, which corresponds to a

half-tone Etep voltage.

The resistance error at the most sfgniflcant t>it, which affects the output

error most significantly, is corrected by adjusting the VR3,

The VR2, equivalent to the width control of asynthesiser, should be

adjusted so that the output changes in 1/12V step. The VR4 is used for

offset adjustment of IC25.

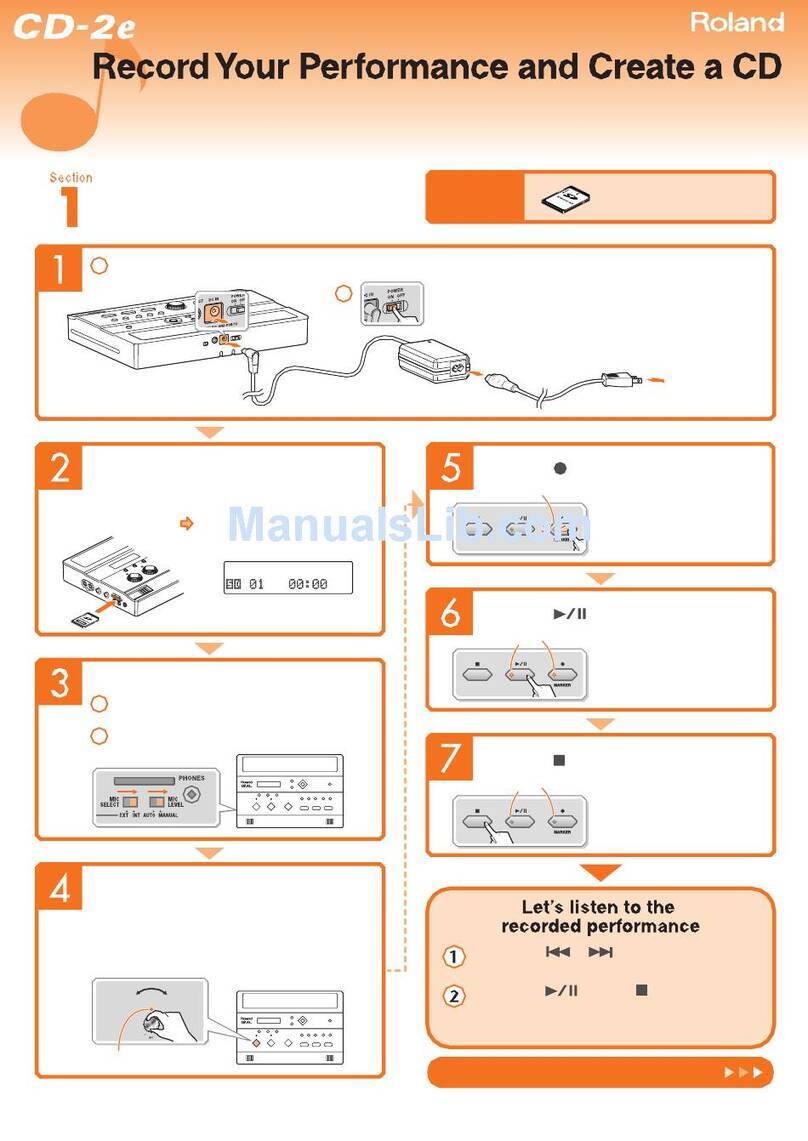

For the GATEs (GT1-GT4) and MPXs {MPX1-MPX4), digital data are

sampled by IC43 in the tinie sharing system [see Fig. 4).

CMT BUOCK

Thi5 block is composed of the input/output circuits for CMT DATA

and TAPE SYNC CLOCK, Th& selection of CMT mode (CMT DATA}

and PLAY mode [TAPE SYJ^C) IS don& by tha hardware (IC41).

The output section delivers an approximately 2JKH!; signal wher> the

DIGITAL DATA is Hand an approximately I.SKH:: signal when the

data is L(see J^ig, 5}.

M

T. Tr T,

Mrr,*Qr,WrJtcCjTrlt ^

T, T. T. —

1'" ^MftijOU. .1nynnr w^in il|

\^ _r~ \ij

\_ ,. .;

rpi IU

DtmDtT >"

.J L.ij L

(2) Accessing to Timer IC30 or lyo Ports IC29 and IC58

The CPU places port address (lower order 8bits, A0-A7] onto the

address bus, then outputs lORQ, etc. as shown in Fig. 3.

As previously explained in CPU terminal functions "ADDRESS BUS",

Port Address Decoder ^IG571 selects the device which in turn reads or

writes data.

iirr:

_r

rMPxV \\\\ \

GT '^ GT \GT \QT \

4 3 \2\1\

MPX MPX MPX

C111IQ

B110 110

A1 1 1 I QFig. 4

S.6Vpp (appr&x.)

JiMJiiJijmriJiiuiMMJUii^

Fig. 5

Fig. 3

For frequency modulation. IC4:2 is wired as afunction generator whose

frequency shifts to the other as R121 is connected to distjonnected

from charging/discharging time constant by F£T SW (TRT5|.

The zen&r diodes (D11, Dl2) are used to prevent tiie output of the

comparator OP amp [operating on 413V arid -15V) from becoming

ur^balanced and to keep tfio duty ratio of the oscillation square wave-

form to 50%. At the input section, asignal from the CMT/SYNC IN

passes through apassive band pass filter and rs ampljfied by the OP amp

(1023). The signal funher pas&es through adiode limitler, is amplified

by !C22 and is separated into asignal for control and asignal for

denriodulation, The signal fordemodulation is democfulat&d bythePLL

(IC19) and the comparator {IC20) and is read via tha S255

INTERFACE {IC5S).

The signal for control passes through arectification circuit and Is

applied TO the tr&nsistor switches (TR^, TR3t to set TP3 in active state.

(While the CMT or SYNC signal is not inputted, TP3 is fixed at Llevel.)

ISee Fig, 6,|

i«5 -^ 7juirurLrumjUL

^JIII

Fig. 6