Sega 32X User manual

Other Sega Game Console manuals

Sega

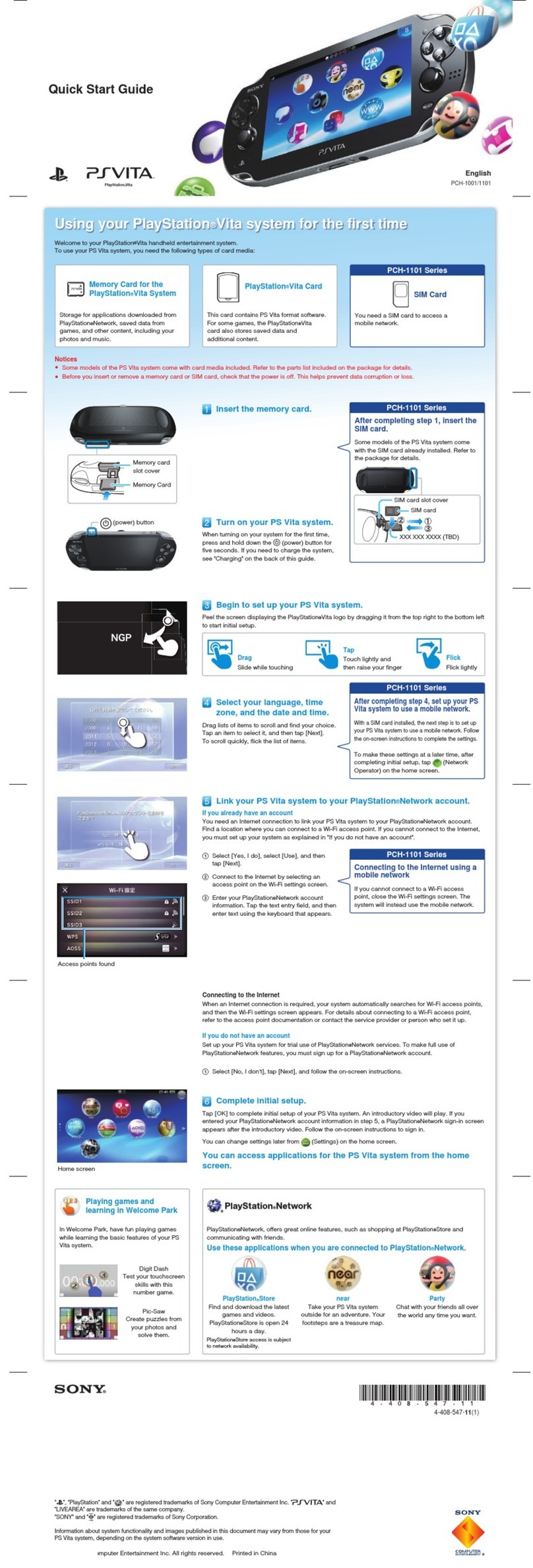

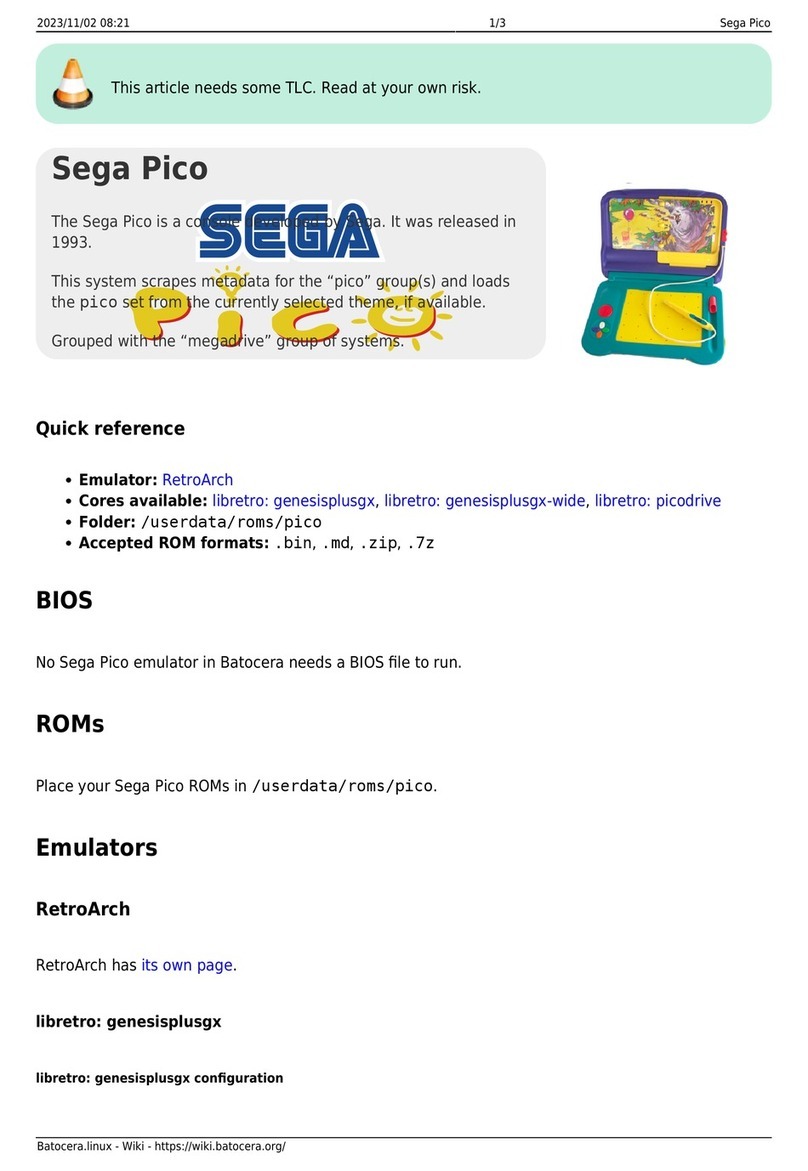

Sega Pico User manual

Sega

Sega SEGA-CD User manual

Sega

Sega 32X User manual

Sega

Sega 32X User manual

Sega

Sega Dreamcast User manual

Sega

Sega Genesis Nomad MK-6100 User manual

Sega

Sega MK - 80200-50 User manual

Sega

Sega Genesis Nomad User manual

Sega

Sega MEGA DRIVE PAL-G User manual

Sega

Sega 32X User manual

Sega

Sega CD User manual

Sega

Sega AtGames FB8280 User manual

Sega

Sega Dreamcast User manual

Sega

Sega ScreenGopher User manual

Sega

Sega ROYAL RUMBLE 999-1117 Supplement

Sega

Sega Mega CD2 User manual

Sega

Sega Saturn User manual

Sega

Sega GENESIS II User manual

Sega

Sega GHOST SQUAD - EVOLUTION User manual

Sega

Sega SUBROC-3D User manual