denotes a physical connector pin, where

c

=connector and

p

=pin. Solid black end is the male side of

the connector. White end is the female side of the connector.

♦connection between different sections.

connection limited to same section.

Arrows indicate direction of signal or energy flow.

♦The symbol without an additional label denotes VDD (–24V).

♦Capacitance in microfarads unless otherwise indicated.

♦This schematic includes the user memory which is not present in the Compet 17 model. Components marked with “§”

are not present in the Compet 17.

♦These drawings based on a Model CS-17C unit with Serial No. 810591T.

Log

♦2000 Jul: Initial drawing / bhilpert.

♦2004 Oct: Signals on the remote connector (NR) elaborated further.

Switches and notes about single-cycle control of P added.

♦2017 May: Format updates. Question of pins on IC 5-6 noted.

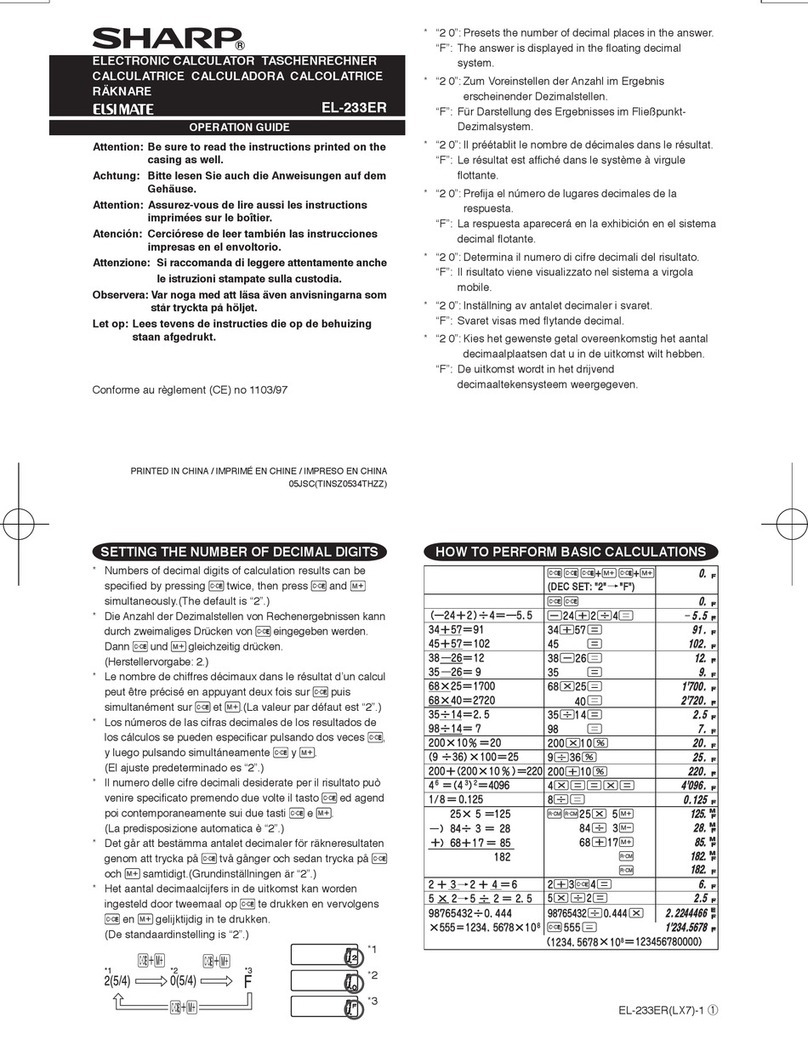

Gate Identification

Gates and logic elements are identified by symbols of the following form:

Gate ID Description

1-

n

inverter in µPD1 IC

2-

n

2 by 2 AND–OR gate in µPD2 IC

3-

n

4-input AND gate in µPD3 IC

4-

n

flip-flop in µPD4 IC

5-

n

4-bit shift register in µPD5 IC

6-

n

8-bit shift register in µPD6 IC

7-

n

MOSFET in µPD7 IC

M-

n

MOSFET discrete

Discrete gates have no distinguishing identifier but their inputs are identified with a label indicating the location of the

diode which implements it:

Label Description

g

.

p

diode in TDA001 or TDA002 package

g

at pin

p

d

n

discrete diode

See the IC Pinouts and Gate Construction page for more about the integrated circuits.

See the Physical Layout and Connectors page for more about IC and gate location.

Signal Names

Section Signal Description

Timing Ø… Master timing.

Ø1 Master clock, data capture phase.

Ø2 Master clock, output transition phase.

Ø3 Master clock, a third phase used by some flip-flops.

ØB… Bit timing.

ØD… Digit timing (4 bits constitutes a digit).

ØnB1+3 Used for triggering digit timing and display latch.

Øn(D16•B8•1) Capture pulse at the end of each full number cycle.

Keyboard K… The keyboard and numeral encoder.

PIndicates a number cycle during which processing occurs.

Control S…, C… The state machine.

CMultiply or divide operation pending.

DDivide operation pending.

F, G, J, M, S Assorted state flags.

S… Assorted internal state signals.

IDLE 1 during display and simple operations, 0 during multi-cycle operations.

CX… Outputs from control to the X register.

CW… “W register.

CM… “M register.

CPX… “ PX decimal point counter.

CPW… “PW decimal point counter.

CPY… “PY digit counter.

X Register X… The operand being displayed. Arithmetic is also incorporated in this register.

XC1,2,4,8 BCD numerals on their way to the display.

CARRY Carry indication to control.

W Register WThe second operand.

M Register MThe user memory.

PX Counter PX Ring counter to hold the place of the decimal point for the X operand.

PXI Signal to the display to turn on the decimal point at the appropriate time.

PW Counter PW Ring counter to hold the place of the decimal point for the W operand.

PY Counter PY Ring counter used during multiply and divide operations.

♦A lowercase “n” in a symbol name indicates the logical NOT operation.

♦The character “ • ” in a symbol name indicates the logical AND operation.

♦The character “+” in a symbol name indicates the logical OR operation.

P-Cycles and Manual Control of Operations

Two switches can be plugged into the remote connector (NR) to provide the ability to single-step through the

major state cycles of an operation. See the Keyboard page for wiring of the switches.

A P-cycle is a full number cycle during which processing occurs and is indicated by the P signal. Major state

transitions occur at the end of a P-cycle. Simple user operations such as numeral entry generate a single P-cycle

without sending IDLE to 0. More complex operations requiring multiple number cycles generate a first P-cycle

and send IDLE to 0. Multiple P-cycles are subsequently generated until the operation is complete, at which time

IDLE returns to 1.

Enabling the MANUAL switch disables the automatic generation of P-cycles for multi-cycle operations. In this

mode, once a multi-cycle operation has been initiated, each press of the STEP pushbutton generates a single

P-cycle, so the operation can be stepped through one P-cycle at a time.