Silego GreenPAK SLG46140 User manual

Silego Technology, Inc. Rev 1.11

000-0046140-111 Revised March 16, 2018

GreenPAK

Programmable Mixed-signal Matrix

SLG46140

General Description

The SLG46140 GreenPAK is a one-time non-volatile memory

(NVM) Programmable Mixed-Signal Matrix designed to

implement a wide variety of mixed-signal functions in a single,

small, low-power device by integrating a number of common

discrete ICs and passive components.

Features

• Logic & Mixed Signal Circuits

• Highly Versatile Macrocells

• 1.8V (±5%) to 5V (±10%) Supply

• Operating Temperature Range: -40°C to 85°C

• RoHS Compliant / Halogen-Free

• Pb-Free: 1.6 x 2.0 x 0.55 mm, 0.4 mm pitch

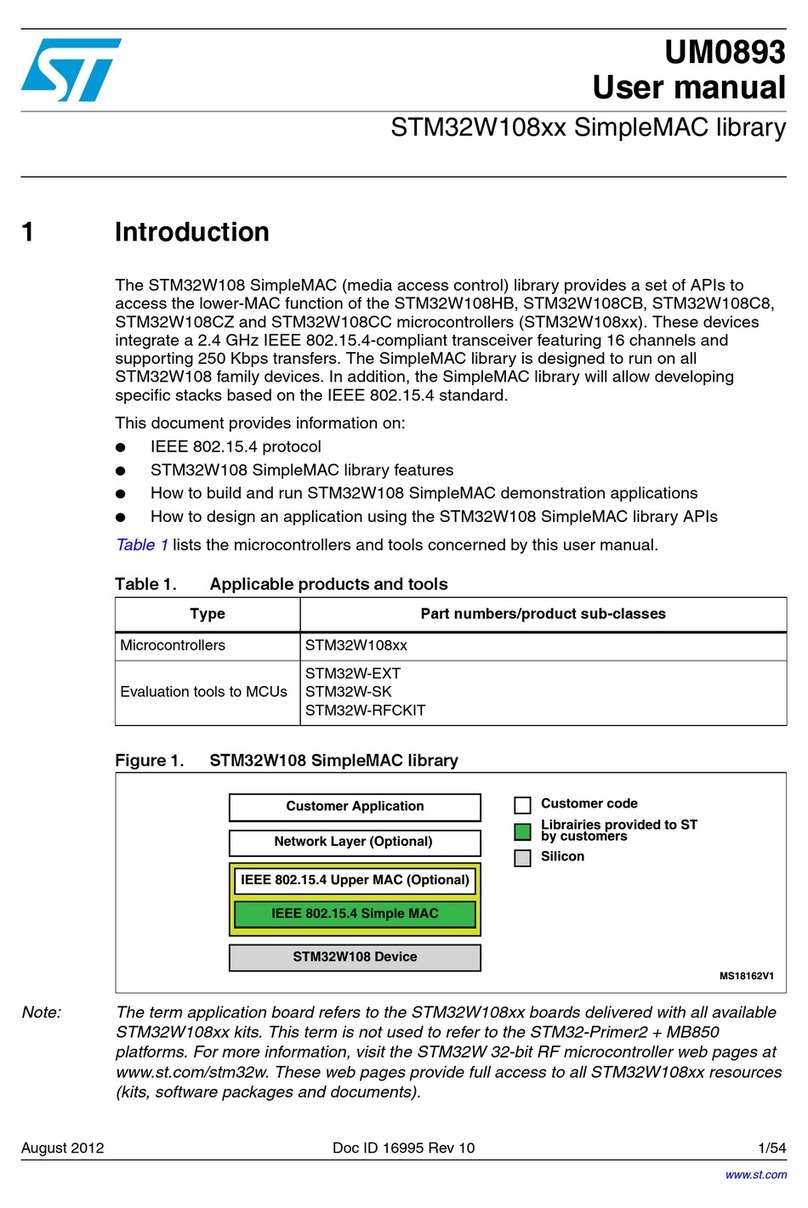

Pin Configuration

Applications

The extensive list of integrated components included in the SLG46140 can be used to implement these and many other

functions, often in combination.

• Ambient Light Detect

• Battery Charge Control

• Fan Control

• Hall Effect Drive

• LED Control

• Level Shift

• One-Shot Detect

• Optical Encode

• Over Voltage Protect

• Port Detection

• Power Sequencing

• Sensor Interface

• Signal De-Glitch

• Signal Delay

• System Reset

• Thermal Management

• Voltage Level Detect

GPIO

GPIO

GPIO

GPIO

GPIO

2

3

49

10

11

GPI

VDD 1

14-pin STQFN

(Top View)

GND

GPIO

8

67

14 13

GPIO GPIO

GPIO

GPIO

GPIO 5

12

000-0046140-111 Page 1 of 169

SLG46140

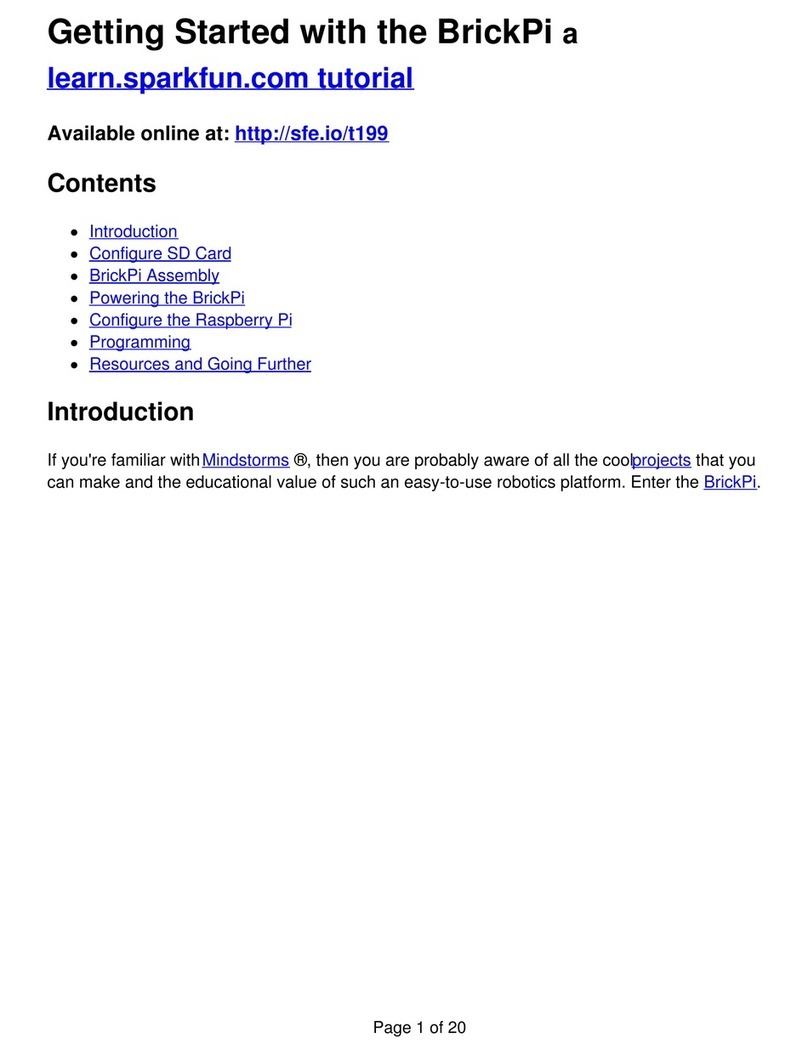

Block Diagram

3-bit

LUT3_7 or

CNT3

Vref

Programmable Delay

RC Oscillator

Pin 1

VDD

Pin 2

GPI

Pin 3

GPIO

Pin 4

GPIO

Pin 14

GPIO

Pin 13

GPIO

Pin 6

GPIO

Pin 7

GPIO

Pin 10

GPIO

Pin 9

GPIO

Pin 12

GPIO

Pin 11

GPIO

ACMP0 ACMP1

FILTER_0

Additional Logic

Functions

Look Up Tables (LUTs)

Counters/Delay Generators

CNT0 CNT1

2-bit

LUT2_0

3-bit

LUT3_0

2-bit

LUT2_1

2-bit

LUT2_3

Combination Function Macrocells

2-bit

LUT2_4

or DFF0

2-bit

LUT2_5

or DFF1

3-bit

LUT3_6 or

Pipe Delay

3bit

LUT3_5

or DFF3

3-bit

LUT3_4

or DFF2

Pin 8

GND

Pin 5

GPIO

DFF/Latches

DFF4 DFF5

2-bit

LUT2_2

3-bit

LUT3_3

3-bit

LUT3_2

3-bit

LUT3_1

4-bit

LUT4_1

or CNT2

4bit

LUT4_0

or PGEN

Digital Comparators/PWMs

DCMP0 DCMP1 DCMP2

POR

PWR DET

DAC1

Ring Oscillator

LF Oscillator

DAC0

8-bit SAR

ADC

PGA

SPI

000-0046140-111 Page 2 of 169

SLG46140

1.0 Overview

In addition to the integrated analog and digital components, the SLG46140 comprises an internal connection matrix and one-time

programmable NVM. By programming the NVM, using the easy-to-use GreenPAK development tools, the designer configures

the connection matrix, I/O Pins, and integrated components of the SLG46140. The SLG46140 includes the following analog and

digital resources:

• 8-bit Successive Approximation Register Analog-to-Digital Converter (SAR ADC)

• ADC 3-bit Programmable Gain Amplifier (PGA)

• Two Digital-to-Analog Converters (DAC)

• Two Analog Comparators (ACMP)

• Voltage Reference (VREF)

• Eight Combinatorial Lookup Tables (LUTs)

• Four 2-bit LUTs

• Four 3-bit LUTs

• Nine Combination Function Macrocells

• One 14-bit Delay/Counter (Wake-Sleep Control)

• Two Selectable DFF/Latch or 2-bit LUTs

• Two Selectable DFF/Latch or 3-bit LUTs

• One Selectable 16-Stage / 3-Output Pipe Delay or 3-bit LUT

• One 8-bit Delay/Counter/Finite State Machine

• One 14-bit Delay/Counter/Finite State Machine

• One Selectable Pattern Generator or 4-bit LUT

• Three Digital Comparators/Pulse Width Modulators (DCMPs /PWMs) w/ Selectable Deadband

• Three Counters/Delays (CNT/DLY)

• One 14-bit Delay/Counter/Finite State Machine

• One 14-bit Delay/Counter

• One 8-bit Delay/Counter

• Two D Flip-flops/Latches

• Programmable Delay w/ Edge Detection

• Three Internal Oscillators

• Low-Frequency

•Ring

• RC 25 kHz and 2 MHz

• Power-On-Reset (POR)

• Slave SPI

• One Bandgap

000-0046140-111 Page 3 of 169

SLG46140

2.0 Pin Description

2.1 Functional Pin Description

Pin # Pin Name Function

1 VDD Power Supply

2 GPI General Purpose Input

3 GPIO General Purpose I/O or ADC Vref_IO

4 GPIO General Purpose I/O or Analog Comparator 0 (-) / PGA_OUT

5 GPIO General Purpose I/O or Analog Comparator 1 (-)

6 GPIO General Purpose I/O or PGA(+)

7 GPIO General Purpose I/O or PGA(-)

8GNDGND

9 GPIO General Purpose I/O or ACMP1(+)

10 GPIO General Purpose I/O or ACMP0(+)

11 GPIO General Purpose I/O or AIN MUX

12 GPIO General Purpose I/O

13 GPIO General Purpose I/O

14 GPIO General Purpose I/O

000-0046140-111 Page 4 of 169

SLG46140

3.0 User Programmability

The SLG46140 is a user programmable device with One-Time-Programmable (OTP) memory elements that are able to construct

combinatorial logic elements. Three of the I/O Pins provide a connection for the bit patterns into the OTP on board memory. A

programming development kit allows the user the ability to create initial devices. Once the design is finalized, the programming

code (.gpx file) is forwarded to Silego to integrate into a production process.

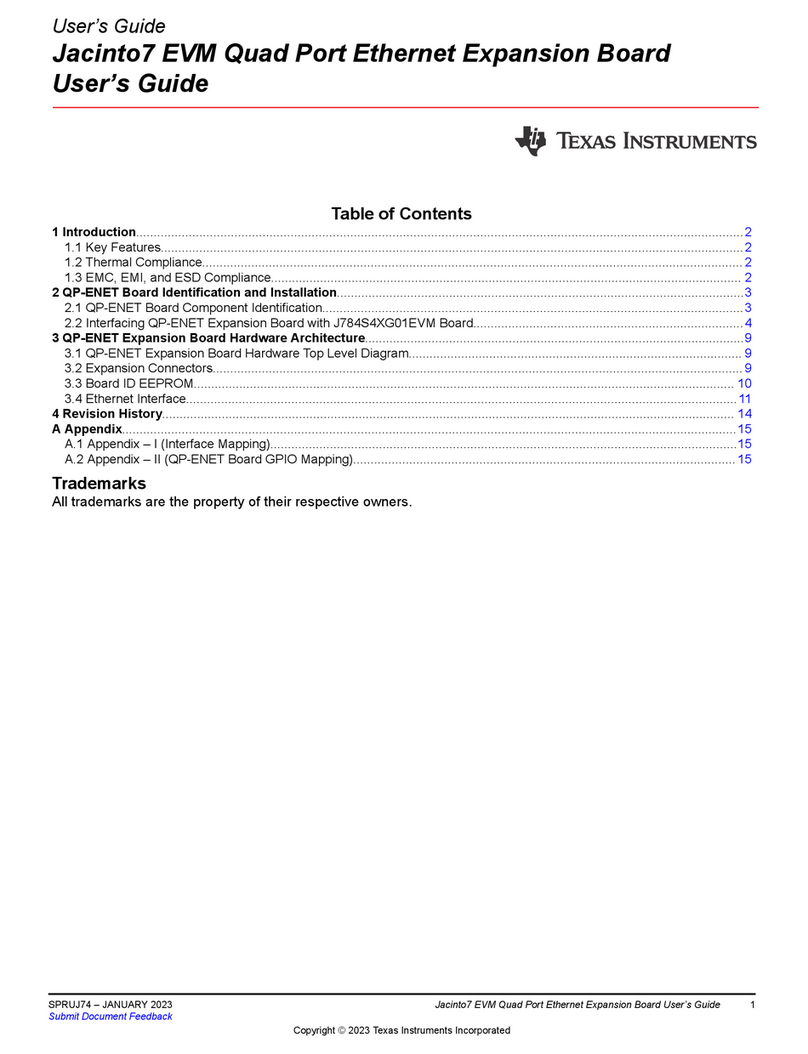

Figure 1. Steps to create a custom Silego GreenPAK device

3URGXFW

'HILQLWLRQ

&XVWRPHU&UHDWHVWKHLURZQGHVLJQLQ

*UHHQ3$.'HVLJQHU

3URJUDP(QJLQHHULQJ6DPSOHVZLWK

*UHHQ3$.3URJUDPPHU

&XVWRPHUYHULILHV*UHHQ3$.

LQV\VWHPGHVLJQ

(PDLOJS[ILOHWR

*UHHQ3$.#VLOHJRFRP

(PDLO3URGXFW,GHD'HILQLWLRQ'UDZLQJRU

6FKHPDWLFWR*UHHQ3$.#VLOHJRFRP

6LOHJR$SSOLFDWLRQV(QJLQHHUVZLOOUHYLHZGHVLJQ

VSHFLILFDWLRQVZLWKFXVWRPHU

6DPSOHVDQG'HVLJQ&KDUDFWHUL]DWLRQ

5HSRUWVHQWWRFXVWRPHU

&XVWRPHUYHULILHV*UHHQ3$.GHVLJQ

&XVWRP*UHHQ3$.SDUW

HQWHUVSURGXFWLRQ

*UHHQ3$.'HVLJQ

DSSURYHGLQV\VWHPWHVW

*UHHQ3$.'HVLJQ

DSSURYHG

*UHHQ3$.'HVLJQ

DSSURYHG

000-0046140-111 Page 5 of 169

SLG46140

4.0 Ordering Information

Part Number Type

SLG46140V 14-pin STQFN

SLG46140VTR 14-pin STQFN - Tape and Reel (3k units)

000-0046140-111 Page 6 of 169

SLG46140

5.0 Electrical Specifications

5.1 Absolute Maximum Conditions

Note*: IN+ relative to GND in Single-ended mode, IN+ and IN- relative to each other in Differential and Pseudo-differential modes.

5.2 Electrical Characteristics (1.8V ±5% VDD)

Parameter Min. Max. Unit

Supply voltage on VDD relative to GND -0.5 7 V

DC Input voltage GND - 0.5 VDD + 0.5 V

PGA Input voltage*

Single-ended -- 1.98/G V

Differential -- (1.98 - 0.55)/G V

Pseudo-

differential -- (1.98 - 0.18)/G V

Maximum Average or DC Current

(Through pin)

Push-Pull 1x -- 12

mA

Push-Pull 2x -- 21

Push-Pull 4x -- 43

OD 1x -- 18

OD 2x -- 45

OD 4x -- 72

Current at Input Pin -1.0 1.0 mA

Storage Temperature Range -65 150 °C

Junction Temperature -- 150 °C

ESD Protection (Human Body Model) 2000 -- V

ESD Protection (Charged Device Model) 500 -- V

Moisture Sensitivity Level 1

Symbol Parameter Condition/Note Min. Typ. Max. Unit

VDD Supply Voltage 1.71 1.80 1.89 V

IQQuiescent Current Static Inputs and Outputs, all

macrocells disabled -- 0.08 -- A

TAOperating Temperature -40 25 85 °C

VPP Programming Voltage 7.25 7.50 7.75 V

VACMP ACMP Input Voltage Range Positive Input 0 -- VDD V

Negative Input 0 -- 1.1 V

VIH HIGH-Level Input Voltage

Logic Input 1.100 -- VDD V

Logic Input with Schmitt Trigger 1.270 -- VDD V

Low-Level Logic Input 0.980 -- VDD V

VIL LOW-Level Input Voltage

Logic Input 0 -- 0.690 V

Logic Input with Schmitt Trigger 0 -- 0.440 V

Low-Level Logic Input 0 -- 0.520 V

VHYS

Schmitt Trigger Hysteresis

Voltage Logic Input with Schmitt Trigger 0.273 0.413 0.553 V

000-0046140-111 Page 7 of 169

SLG46140

ILKG

(Absolute

Value)

ACMP Input Leakage Vin = 0 V -- 0.39 2.39 nA

Vin = VDD -- 0.26 1.29 nA

PGA Input Leakage Vin = 0 V -- 0.04 0.18 nA

Vin = VDD -- 0.12 0.65 nA

Logic Input without Schmitt

Trigger (Floating) Leakage

Vin = 0 V -- 0.04 0.34 nA

Vin = VDD -- 1.55 71.77 nA

Logic Input with Schmitt

Trigger (Floating) Leakage

Vin = 0 V -- 0.04 0.39 nA

Vin = VDD -- 1.55 72.26 nA

Low-Level Logic Input

(Floating) Leakage

Vin = 0 V -- 0.04 0.33 nA

Vin = VDD -- 1.55 72.39 nA

VOH HIGH-Level Output Voltage

Push-Pull 1X, Open Drain PMOS 1X,

IOH = 100 A1.670 1.788 -- V

Push-Pull 2X, Open Drain PMOS 2X,

IOH = 100 A1.679 1.792 -- V

Push-Pull 4X, Open Drain PMOS 4X,

IOH = 100 A1.700 1.798 -- V

VOL LOW-Level Output Voltage

Push-Pull 1X,

IOL= 100 A-- 0.010 0.020 V

Push-Pull 2X,

IOL= 100 A-- 0.007 0.010 V

Push-Pull 4X,

IOL= 100 A-- 0.004 0.009 V

Open Drain NMOS 1X,

IOL= 100 A-- 0.007 0.010 V

Open Drain NMOS 2X,

IOL= 100 A-- 0.002 0.010 V

Open Drain NMOS 4X,

IOL= 100 A-- 0.001 0.004 V

IOH

HIGH-Level Output Pulse

Current (see Note 1)

Push-Pull 1X, Open Drain PMOS 1X,

VOH = VDD - 0.2 1.053 1.690 -- mA

Push-Pull 2X, Open Drain PMOS 2X,

VOH = VDD - 0.2 2.069 3.390 -- mA

Push-Pull 4X, Open Drain PMOS 4X,

VOH = VDD - 0.2 4.007 7.070 -- mA

IOL

LOW-Level Output Pulse

Current (see Note 1)

Push-Pull 1X,

VOL = 0.15 V 0.760 1.420 -- mA

Push-Pull 2X,

VOL = 0.15 V 1.520 2.840 -- mA

Push-Pull 4X,

VOL = 0.15 V 4.430 6.122 -- mA

Open Drain NMOS 1X,

VOL = 0.15 V 1.530 2.840 -- mA

Open Drain NMOS 2X,

VOL = 0.15 V 3.060 5.680 -- mA

Open Drain NMOS 4X,

VOL = 0.15 V 10.504 14.987 -- mA

Symbol Parameter Condition/Note Min. Typ. Max. Unit

000-0046140-111 Page 8 of 169

SLG46140

IVDD

Maximum Average or DC

Current Through VDD Pin

(Per chip side, see Note 2)

TJ = 85°C -- -- 45 mA

TJ = 110°C -- -- 21 mA

IGND

Maximum Average or DC

Current Through GND Pin

(Per chip side, see Note 2)

TJ = 85°C -- -- 45 mA

TJ = 110°C -- -- 21 mA

VO

Maximal Voltage Applied

to any PIN in High-

Impedance State

VDD V

TSU Startup Time (see Note 3) from VDD rising past PONTHR 0.671 1.179 4.999 ms

PONTHR Power On Threshold VDD Level Required to Start Up the

Chip 0.961 1.310 1.657 V

POFFTHR Power Off Threshold VDD Level Required to Switch Off the

Chip 0.875 1.109 1.287 V

RPUP Pull Up Resistance

1 M Pull Up 896.67 1075.81 1337.85 kΩ

100 k Pull Up 93.13 111.06 132.78 kΩ

10 k Pull Up 11.10 12.95 15.30 kΩ

RPDWN Pull Down Resistance

1 M Pull Down 660.68 1074.06 1287.58 kΩ

100 k Pull Down 93.29 111.06 132.78 kΩ

10 k Pull Down 10.90 12.75 15.51 kΩ

Note 1: DC or average current through any pin should not exceed value given in Absolute Maximum Conditions.

Note 2: The GreenPAK’s power rails are divided in two sides. Pins 2, 3, 4, 5, 6 and 7 are connected to one side, pins 9,10, 11,

12, 13 and 14 to another.

Note 3: VDD ramp rising speed must be less than 0.6 V/µs after power on. Violating this specification may cause chip to restart.

Symbol Parameter Condition/Note Min. Typ. Max. Unit

000-0046140-111 Page 9 of 169

SLG46140

5.3 Electrical Characteristics (3.3V ±10% VDD)

Symbol Parameter Condition/Note Min. Typ. Max. Unit

VDD Supply Voltage 3.0 3.3 3.6 V

IQQuiescent Current

Static Inputs and Outputs

(when all macrocells that require

internal RC OSC or bandgap are

inactive)

-- 0.16 -- A

TAOperating Temperature -40 25 85 °C

VPP Programming Voltage 7.25 7.50 7.75 V

VACMP ACMP Input Voltage Range Positive Input 0 -- VDD V

Negative Input 0 -- 1.2 V

VIH HIGH-Level Input Voltage

Logic Input 1.780 -- VDD V

Logic Input with Schmitt Trigger 2.130 -- VDD V

Low-Level Logic Input 1.130 -- VDD V

VIL LOW-Level Input Voltage

Logic Input 0 -- 1.210 V

Logic Input with Schmitt Trigger 0 -- 0.950 V

Low-Level Logic Input 0 -- 0.690 V

VHYS

Schmitt Trigger Hysteresis

Voltage Logic Input with Schmitt Trigger 0.346 0.486 0.625 V

ILKG

(Absolute

Value)

ACMP Input Leakage Vin = 0 V -- 0.42 2.49 nA

Vin = VDD -- 0.30 1.48 nA

PGA Input Leakage Vin = 0 V -- 0.05 0.21 nA

Vin = VDD -- 0.13 0.73 nA

Logic Input without Schmitt

Trigger (Floating) Leakage

Vin = 0 V -- 0.05 0.39 nA

Vin = VDD -- 1.47 67.45 nA

Logic Input with Schmitt

Trigger (Floating) Leakage

Vin = 0 V -- 0.05 0.40 nA

Vin = VDD -- 1.47 67.80 nA

Low-Level Logic Input

(Floating) Leakage

Vin = 0 V -- 0.05 0.39 nA

Vin = VDD -- 1.47 67.84 nA

VOH HIGH-Level Output Voltage

Push-Pull 1X, Open Drain PMOS 1X,

IOH = 3 mA 2.722 3.102 -- V

Push-Pull 2X, Open Drain PMOS 2X,

IOH = 3 mA 2.861 3.201 -- V

Push-Pull 4X, Open Drain PMOS 4X,

IOH = 3 mA 2.927 3.248 -- V

000-0046140-111 Page 10 of 169

SLG46140

VOL LOW-Level Output Voltage

Push-Pull 1X,

IOL= 3 mA -- 0.151 0.280 V

Push-Pull 2X,

IOL= 3 mA -- 0.079 0.130 V

Push-Pull 4X,

IOL= 3 mA -- 0.055 0.104 V

Open Drain NMOS 1X,

IOL= 3 mA -- 0.070 0.130 V

Open Drain NMOS 2X,

IOL= 3 mA -- 0.040 0.070 V

Open Drain NMOS 4X,

IOL= 3 mA -- 0.018 0.023 V

IOH

HIGH-Level Output Pulse

Current (see Note 1)

Push-Pull 1X, Open Drain PMOS 1X,

VOH = 2.4 V 5.770 11.151 -- mA

Push-Pull 2X, Open Drain PMOS 2X,

VOH = 2.4 V 11.278 21.750 -- mA

Push-Pull 4X, Open Drain PMOS 4X,

VOH = 2.4 V 21.458 40.903 -- mA

IOL

LOW-Level Output Pulse

Current (see Note 1)

Push-Pull 1X,

VOL = 0.4 V 4.060 6.920 -- mA

Push-Pull 2X,

VOL = 0.4 V 8.130 13.840 -- mA

Push-Pull 4X,

VOL = 0.4 V 19.628 28.240 -- mA

Open Drain NMOS 1X,

VOL = 0.4 V 8.130 13.850 -- mA

Open Drain NMOS 2X,

VOL = 0.4 V 16.260 23.700 -- mA

Open Drain NMOS 4X,

VOL = 0.4 V 45.976 66.769 -- mA

IVDD

Maximum Average or DC

Current Through VDD Pin

(Per chip side, see Note 2)

TJ = 85°C -- -- 45 mA

TJ = 110°C -- -- 21 mA

IGND

Maximum Average or DC

Current Through GND Pin

(Per chip side, see Note 2)

TJ = 85°C -- -- 45 mA

TJ = 110°C -- -- 21 mA

VO

Maximal Voltage Applied

to any PIN in High-

Impedance State

VDD V

TSU Startup Time (see Note 3) from VDD rising past PONTHR 0.504 0.927 3.092 ms

PONTHR Power On Threshold VDD Level Required to Start Up the

Chip 0.962 1.312 1.658 V

POFFTHR Power Off Threshold VDD Level Required to Switch Off the

Chip 0.876 1.109 1.287 V

RPUP Pull Up Resistance

1 M Pull Up 888.18 1075.30 1316.50 kΩ

100 k Pull Up 92.15 110.40 132.16 kΩ

10 k Pull Up 9.83 11.99 14.49 kΩ

Symbol Parameter Condition/Note Min. Typ. Max. Unit

000-0046140-111 Page 11 of 169

SLG46140

RPDWN Pull Down Resistance

1 M Pull Down 662.60 1074.47 1285.21 kΩ

100 k Pull Down 92.42 110.60 132.48 kΩ

10 k Pull Down 10.00 11.88 14.25 kΩ

Note 1: DC or average current through any pin should not exceed value given in Absolute Maximum Conditions.

Note 2: The GreenPAK’s power rails are divided in two sides. Pins 2, 3, 4, 5, 6 and 7 are connected to one side, pins 9,10, 11,

12, 13 and 14 to another.

Note 3: VDD ramp rising speed must be less than 0.6 V/µs after power on. Violating this specification may cause chip to restart.

Symbol Parameter Condition/Note Min. Typ. Max. Unit

000-0046140-111 Page 12 of 169

SLG46140

5.4 Electrical Characteristics (5V ±10% VDD)

Symbol Parameter Condition/Note Min. Typ. Max. Unit

VDD Supply Voltage 4.5 5.0 5.5 V

IQQuiescent Current

Static Inputs and Outputs

(when all macrocells that require

internal RC OSC or bandgap are

inactive)

-- 0.25 -- A

TAOperating Temperature -40 25 85 °C

VPP Programming Voltage 7.25 7.50 7.75 V

VACMP ACMP Input Voltage Range Positive Input 0 -- VDD V

Negative Input 0 -- 1.2 V

VIH HIGH-Level Input Voltage

Logic Input 2.901 -- VDD V

Logic Input with Schmitt Trigger 3.254 -- VDD V

Low-Level Logic Input 1.209 -- VDD V

VIL LOW-Level Input Voltage

Logic Input 0 -- 1.840 V

Logic Input with Schmitt Trigger 0 -- 1.510 V

Low-Level Logic Input 0 -- 0.780 V

VHYS

Schmitt Trigger Hysteresis

Voltage Logic Input with Schmitt Trigger 0.443 0.618 0.792 V

ILKG

(Absolute

Value)

ACMP Input Leakage Vin = 0 V -- 0.70 3.30 nA

Vin = VDD -- 0.38 1.84 nA

PGA Input Leakage Vin = 0 V -- 0.25 1.05 nA

Vin = VDD -- 0.17 0.91 nA

Logic Input without Schmitt

Trigger (Floating) Leakage

Vin = 0 V -- 0.29 1.40 nA

Vin = VDD -- 1.46 64.99 nA

Logic Input with Schmitt

Trigger (Floating) Leakage

Vin = 0 V -- 0.29 1.40 nA

Vin = VDD -- 1.45 65.16 nA

Low-Level Logic Input

(Floating) Leakage

Vin = 0 V -- 0.29 1.40 nA

Vin = VDD -- 1.45 66.16 nA

VOH HIGH-Level Output Voltage

Push-Pull 1X, Open Drain PMOS 1X,

IOH = 5 mA 4.168 4.759 -- V

Push-Pull 2X, Open Drain PMOS 2X,

IOH = 5 mA 4.330 4.878 -- V

Push-Pull 4X, Open Drain PMOS 4X,

IOH = 5 mA 4.405 4.932 -- V

000-0046140-111 Page 13 of 169

SLG46140

VOL LOW-Level Output Voltage

Push-Pull 1X,

IOL= 5 mA -- 0.193 0.330 V

Push-Pull 2X,

IOL= 5 mA -- 0.101 0.160 V

Push-Pull 4X,

IOL= 5 mA -- 0.071 0.135 V

Open Drain NMOS 1X,

IOL= 5 mA -- 0.090 0.160 V

Open Drain NMOS 2X,

IOL= 5 mA -- 0.050 0.080 V

Open Drain NMOS 4X,

IOL= 5 mA -- 0.021 0.030 V

IOH

HIGH-Level Output Pulse

Current (see Note 1)

Push-Pull 1X, Open Drain PMOS 1X,

VOH = 2.4 V 20.716 30.759 -- mA

Push-Pull 2X, Open Drain PMOS 2X,

VOH = 2.4 V 40.059 59.691 -- mA

Push-Pull 4X, Open Drain PMOS 4X,

VOH = 2.4 V 76.137 112.724 -- mA

IOL

LOW-Level Output Pulse

Current (see Note 1)

Push-Pull 1X,

VOL = 0.4 V 6.010 9.730 -- mA

Push-Pull 2X,

VOL = 0.4 V 12.020 19.460 -- mA

Push-Pull 4X,

VOL = 0.4 V 26.150 37.191 -- mA

Open Drain NMOS 1X,

VOL = 0.4 V 12.030 19.460 -- mA

Open Drain NMOS 2X,

VOL = 0.4 V 24.060 38.920 -- mA

Open Drain NMOS 4X,

VOL = 0.4 V 60.071 86.737 -- mA

IVDD

Maximum Average or DC

Current Through VDD Pin

(Per chip side, see Note 2)

TJ = 85°C -- -- 45 mA

TJ = 110°C -- -- 21 mA

IGND

Maximum Average or DC

Current Through GND Pin

(Per chip side, see Note 2)

TJ = 85°C -- -- 45 mA

TJ = 110°C -- -- 21 mA

VO

Maximal Voltage Applied

to any PIN in High-

Impedance State

VDD V

TSU Startup Time (see Note 3) from VDD rising past PONTHR 0.462 0.848 2.693 ms

PONTHR Power On Threshold VDD Level Required to Start Up the

Chip 0.963 1.314 1.659 V

POFFTHR Power Off Threshold VDD Level Required to Switch Off the

Chip 0.877 1.109 1.288 V

RPUP Pull Up Resistance

1 M Pull Up 884.96 1074.96 1306.99 kΩ

100 k Pull Up 91.90 110.17 131.96 kΩ

10 k Pull Up 8.98 11.64 14.55 kΩ

Symbol Parameter Condition/Note Min. Typ. Max. Unit

000-0046140-111 Page 14 of 169

SLG46140

RPDWN Pull Down Resistance

1 M Pull Down 667.10 1074.89 1287.81 kΩ

100 k Pull Down 92.03 110.34 132.21 kΩ

10 k Pull Down 9.45 11.55 14.05 kΩ

Note 1: DC or average current through any pin should not exceed value given in Absolute Maximum Conditions.

Note 2: The GreenPAK’s power rails are divided in two sides. Pins 2, 3, 4, 5, 6 and 7 are connected to one side, pins 9,10, 11,

12, 13 and 14 to another.

Note 3: VDD ramp rising speed must be less than 0.6 V/µs after power on. Violating this specification may cause chip to restart.

Symbol Parameter Condition/Note Min. Typ. Max. Unit

000-0046140-111 Page 15 of 169

SLG46140

5.5 Typical Delay Estimated for Each Macrocell

Table 1. Typical Delay Estimated for Each Macrocell

Symbol Parameter Note VDD=1.8V VDD=3.3V VDD=5.0V Unit

Rising Falling Rising Falling Rising Falling

tpd Delay LUT 2-bit 17.43 15.33 6.31 6.09 4.20 4.31 ns

tpd Delay LUT 2-bit (Shared with DFF/Latch) 21.53 20.67 8.13 8.33 5.45 6.01 ns

tpd Delay LUT 3-bit 18.49 15.69 6.74 6.31 4.49 4.52 ns

tpd Delay LUT 3-bit (Shared with DFF/Latch) 23.04 21.51 8.74 8.75 5.86 6.37 ns

tpd Delay LUT 3-bit (Shared with Pipe Delay) 25.65 24.01 9.37 9.47 6.677.32ns

tpd Delay LUT 3-bit (Shared with CNT/DLY) 23.17 20.67 8.62 8.32 5.73 6.05 ns

tpd Delay LUT 4-bit (Shared with PGEN) 21.13 22.27 9.07 8.97 6.04 6.46 ns

tpd Delay LUT 4-bit (Shared with CNT/DLY) 25.42 22.29 9.54 9.02 6.41 6.59 ns

tpd Delay DFF (Shared with 2-bit LUT) 27.25 28.68 10.67 10.78 7.30 7.51 ns

tpd Delay DFF (Shared with 3-bit LUT) 27.87 28.96 10.87 10.93 7.44 7.61 ns

tpd Delay DFF (Shared with 3-bit LUT) nRe-

set -- 29.84 -- 12.41 -- 8.95 ns

tpd Delay DFF (Shared with 3-bit LUT) nSet -- 36.73 -- 14.00 -- 9.42 ns

tpd Delay DFF 23.01 23.77 8.91 8.73 5.95 6.15 ns

tpd Delay DFF nReset -- 23.64 -- 9.71 -- 7.11 ns

tpd Delay DFF nSet -- 31.5 -- 11.4 -- 7.68 ns

tpd Delay CNT/DLY opposite to selected

edge delay 46.61 36.87 18.56 15.62 12.53 11.23 ns

tpd Delay CNT/DLY (Shared) opposite to se-

lected edge delay 47.30 37.16 18.78 15.78 12.68 11.77 ns

tpd Delay CNT/DLY Both edge detect 49.5 52.9 20.07 20.84 13.81 14.32 ns

tpd Delay CNT/DLY Rising edge detect 52.39 -- 21.32 -- 14.67 -- ns

tpd Delay CNT/DLY Falling edge detect -- 55.94 -- 22.15 -- 15.27 ns

tw Width CNT/DLY Both edge detect 25.17 24.93 11.98 12.01 8.76 8.83 ns

tw Width CNT/DLY Rising edge detect 25.76 -- 12.14 -- 8.86 -- ns

tw Width CNT/DLY Falling edge detect -- 24.51 -- 11.79 -- 8.57 ns

tpd Delay Latch (Shared with 2-bit LUT) 26.25 25.43 10.2 10.43 6.99 7.58ns

tpd Delay Latch (Shared with 3-bit LUT) 26.93 25.72 10.42 10.6 7.11 7.72ns

tpd Delay Latch (Shared with 3-bit LUT) nRe-

set -- 31.8 -- 13.17 -- 9.61 ns

tpd Delay Latch (Shared with 3-bit LUT) nSet -- 34.23 -- 12.97 -- 8.76 ns

tpd Delay Latch 21.28 19.87 8.17 8.13 5.51 5.92 ns

tpd Delay Latch nReset -- 25.45 -- 10.52 -- 7.74 ns

tpd Delay Latch nSet -- 28.36 -- 10.37 -- 6.76 ns

tpd Delay Pipe Delay (Shared) 33.44 34.93 13.39 13.21 9.40 9.17 ns

tpd Delay Pipe Delay (Shared) nReset -- 35.42 -- 15.07 -- 11.24 ns

tpd Delay PGEN (Shared) 22.44 23.52 8.69 9.00 5.77 6.01 ns

tpd Delay PGEN (Shared) nReset to 0 -- 21.73 -- 8.88 -- 6.60 ns

tpd Delay PGEN (Shared) nReset to 1 22.81 -- 9.75 -- 6.99 -- ns

tpd Delay PDLY 1Cells Both edge detect 30.71 35.23 12.00 13.45 8.42 9.26ns

tpd Delay PDLY 1Cells delayed output Both

edge detect 191.41 195.73 75.44 76.67 48.41 49.32 ns

000-0046140-111 Page 16 of 169

SLG46140

tpd Delay PDLY 1Cells delayed output Rising

edge detect 192.15 -- 75.71 -- 48.65 -- ns

tpd Delay PDLY 1Cells delayed output Fall-

ing edge detect -- 195.73 -- 76.60 -- 49.42 ns

tpd Delay PDLY 1Cells Rising edge detect 31.32 -- 12.33 -- 8.65 -- ns

tpd Delay PDLY 1Cells Falling edge detect -- 35.52 -- 13.63 -- 9.36 ns

tpd Delay PDLY 2Cells Both edge detect 30.68 35.23 12.04 13.47 8.44 9.25ns

tpd Delay PDLY 2Cells delayed output Both

edge detect 358.75 362.80 139.97 141.13 88.68 89.64 ns

tpd Delay PDLY 2Cells delayed output Rising

edge detect 359.61 -- 140.37 -- 88.92 -- ns

tpd Delay PDLY 2Cells delayed output Fall-

ing edge detect -- 362.93 -- 141.33 -- 89.66 ns

tpd Delay PDLY 2Cells Rising edge detect 31.35 -- 12.33 -- 8.65 -- ns

tpd Delay PDLY 2Cells Falling edge detect -- 35.49 -- 13.60 -- 9.37 ns

tpd Delay PDLY 3Cells Both edge detect 30.65 35.25 12.04 13.51 8.43 9.26ns

tpd Delay PDLY 3Cells delayed output Both

edge detect 517.41 521.47 202.97 204.20 128.17 129.08 ns

tpd Delay PDLY 3Cells delayed output Rising

edge detect 518.35 -- 203.44 -- 128.36 -- ns

tpd Delay PDLY 3Cells delayed output Fall-

ing edge detect -- 522.00 -- 204.27 -- 129.16 ns

tpd Delay PDLY 3Cells Rising edge detect 31.35 -- 12.33 -- 8.68 -- ns

tpd Delay PDLY 3Cells Falling edge detect -- 35.60 -- 13.65 -- 9.37 ns

tpd Delay PDLY 4Cells Both edge detect 30.76 35.23 12.03 13.53 8.42 9.25ns

tpd Delay PDLY 4Cells delayed output Both

edge detect 684.15 688.20 267.31 268.47 168.33 169.41 ns

tpd Delay PDLY 4Cells delayed output Rising

edge detect 685.08 -- 267.57 -- 168.46 -- ns

tpd Delay PDLY 4Cells delayed output Fall-

ing edge detect -- 688.67 -- 268.47 -- 169.54 ns

tpd Delay PDLY 4Cells Rising edge detect 31.37 -- 12.35 -- 8.66 -- ns

tpd Delay PDLY 4Cells Falling edge detect -- 35.73 -- 13.63 -- 9.35 ns

tpd Delay PDLY Both edge delay Delayed

output 1CELLs Rising 382.08 382.60 166.57 167.53 121.00 122.74 ns

tpd Delay PDLY Both edge delay Delayed

output 2CELLs Rising 730.35 730.80 319.84 321.13 232.80 234.41 ns

tpd Delay PDLY Both edge delay Delayed

output 3CELLs Rising 1074.28 1075.93 471.71 473.47 343.46 345.28 ns

tpd Delay PDLY Both edge delay Delayed

output 4CELLs Rising 1421.41 1422.60 624.77 626.47 455.13 456.94 ns

tw Width PDLY 1Cells Both edge detect 344.67 346.13 153.20 153.73 111.89 112.43 ns

tw Width PDLY 1Cells delayed output Both

edge detect 348.67 350.20 152.07 152.73 110.93 111.13 ns

tw Width PDLY 1Cells delayed output Rising

edge detect 348.80 -- 152.20 -- 110.80 -- ns

tw Width PDLY 1Cells delayed output Fall-

ing edge detect -- 349.93 -- 152.87 -- 111.39 ns

Symbol Parameter Note VDD=1.8V VDD=3.3V VDD=5.0V Unit

Rising Falling Rising Falling Rising Falling

000-0046140-111 Page 17 of 169

SLG46140

tw Width PDLY 1Cells Rising edge detect 344.67 -- 153.27 -- 111.95 -- ns

tw Width PDLY 1Cells Falling edge detect -- 345.80 -- 153.73 -- 112.43 ns

tw Width PDLY 2Cells Both edge detect 692.87 694.27 306.80 307.33 223.53 224.33 ns

tw Width PDLY 2Cells delayed output Both

edge detect 687.40 688.73 301.60 302.27 220.20 220.80 ns

tw Width PDLY 2Cells delayed output Rising

edge detect 687.33 -- 301.93 -- 219.93 -- ns

tw Width PDLY 2Cells delayed output Fall-

ing edge detect -- 688.60 -- 302.47 -- 220.47 ns

tw Width PDLY 2Cells Rising edge detect 693.00 -- 306.87 -- 223.87 -- ns

tw Width PDLY 2Cells Falling edge detect -- 693.73 -- 307.33 -- 224.13 ns

tw Width PDLY 3Cells Both edge detect 1036.87 1039.20 458.53 459.93 334.20 335.27 ns

tw Width PDLY 3Cells delayed output Both

edge detect 1034.47 1036.87 452.07 453.20 329.47 330.27 ns

tw Width PDLY 3Cells delayed output Rising

edge detect 1034.33 -- 452.27 -- 329.20 -- ns

tw Width PDLY 3Cells delayed output Fall-

ing edge detect -- 1036.80 -- 453.27 -- 330.00 ns

tw Width PDLY 3Cells Rising edge detect 1036.73 -- 458.73 -- 334.47 -- ns

tw Width PDLY 3Cells Falling edge detect -- 1038.73 -- 459.73 -- 335.13 ns

tw Width PDLY 4Cells Both edge detect 1383.47 1385.73 611.73 612.67 445.93 446.80 ns

tw Width PDLY 4Cells delayed output Both

edge detect 1371.27 1373.67 600.93 602.07 439.00 439.93 ns

tw Width PDLY 4Cells delayed output Rising

edge detect 1371.47 -- 601.13 -- 438.73 -- ns

tw Width PDLY 4Cells delayed output Fall-

ing edge detect -- 1373.80 -- 602.20 -- 439.73 ns

tw Width PDLY 4Cells Rising edge detect 1383.40 -- 611.67 -- 446.07 -- ns

tw Width PDLY 4Cells Falling edge detect -- 1385.13 -- 612.60 -- 446.53 ns

tpd Delay Digital Input without Schmitt trigger

-- NMOS -- 34.18 -- 13.60 -- 9.47 ns

tpd Delay Digital Input without Schmitt trigger

-- NMOS 2x -- 31.88 -- 12.85 -- 8.97 ns

tpd Delay Digital Input without Schmitt trigger

-- NMOS 4x -- 31.80 -- 12.51 -- 8.80 ns

tpd Delay Digital Input without Schmitt trigger

-- PMOS 41.12 -- 15.24 -- 10.58 -- ns

tpd Delay Digital Input without Schmitt trigger

-- PMOS 2x 40.29 -- 14.93 -- 10.38 -- ns

tpd Delay Digital Input with Schmitt Trigger --

Push Pull 41.10 35.59 15.64 15.03 10.89 10.69 ns

tpd Delay Low Voltage Digital Input -- Push

Pull 41.67 476.4 15.39 -- 10.49 120.93 ns

tpd Delay Digital Input without Schmitt trigger

-- 3-state 40.28 34.33 15.11 14.38 10.46 10.23 ns

tpd Delay Digital Input without Schmitt trigger

-- 3-state 2x 38.65 33.95 14.50 13.95 10.11 9.94 ns

Symbol Parameter Note VDD=1.8V VDD=3.3V VDD=5.0V Unit

Rising Falling Rising Falling Rising Falling

000-0046140-111 Page 18 of 169

SLG46140

tpd Delay Digital Input without Schmitt trigger

-- 3-state 4x 37.83 33.03 14.14 13.54 9.93 9.67 ns

tpd Delay Digital Input without Schmitt trigger

-- Push Pull Z to 1 42.03 -- 15.61 -- 10.78 -- ns

tpd Delay Digital Input without Schmitt trigger

-- Push Pull Z to 0 -- 36.09 -- 13.83 -- 9.51 ns

tpd Delay Digital Input without Schmitt Trig-

ger -- Push Pull 1x 40.92 35.45 15.32 14.79 10.60 10.52 ns

tpd Delay Digital Input without Schmitt Trig-

ger -- Push Pull 2x 39.61 34.98 14.8 14.37 10.31 10.17 ns

tpd Delay Digital Input without Schmitt Trig-

ger -- Push Pull 4x 37.84 33.40 14.11 13.80 9.93 9.92 ns

Symbol Parameter Note VDD=1.8V VDD=3.3V VDD=5.0V Unit

Rising Falling Rising Falling Rising Falling

000-0046140-111 Page 19 of 169

SLG46140

5.6 Typical Current Consumption

Table 2. Typical Current Consumption

Note VDD = 1.8V VDD = 3.3V VDD = 5.0V Unit

Quiescent current 0.08 0.16 0.25 uA

Low frequency OSC; Clock predivider by 1 0.37 0.48 0.67 uA

Low frequency OSC; Clock predivider by 16 0.36 0.46 0.64 uA

RC OSC 25kHz; First Clock predivider by 1 4.85 5.24 6.07 uA

RC OSC 25kHz; First Clock predivider by 8 4.77 5.08 5.81 uA

RC OSC 2MHz; First Clock predivider by 1 23.94 35.78 51.44 uA

RC OSC 2MHz; First Clock predivider by 8 16.70 21.17 27.94 uA

Ring OSC; First Clock predivider by 1 70.80 83.81 116.94 uA

Ring OSC; First Clock predivider by 16 57.82 57.31 71.86 uA

ACMP; Hysteresis 0mv/25mV; Low bandwidth Dis-

able; Input PIN10; Gain 0.25x - 1x 47.49 39.65 43.72 uA

ACMP; Hysteresis 0mV/25mV; Low bandwidth En-

able; Input PIN10; Gain 1x 42.50 34.64 38.71 uA

Bandgap 37.06 29.18 33.26 uA

VREF 79.08 71.38 75.46 uA

PGA; Single-end mode; Gain 0.25x; 97.58 119.37 132.18 uA

PGA; Single-end mode; Gain 0.5x; 103.04 119.59 131.32 uA

PGA; Single-end mode; Gain 1x 69.44 73.44 77.36 uA

PGA; Single-end mode; Gain 2x 116.42 91.50 111.10 uA

PGA; Single-end mode; Gain 4x 117.87 97.20 114.72 uA

DAC0; Power on 48.24 40.40 44.47 uA

DAC1; DCMP1 Input 62.83 55.04 59.11 uA

ADC; Single-end mode; Vref: 1.2 V; Force analog

part Enable; Speed selection 100 kHz + RC OSC

25 kHz; First Clock predivider by 1; Sample rate

1.56 kHz

172.24 166.10 171.01 uA

ADC; Single-end mode; Vref: 1.2 V; Force analog

part Enable; Speed selection 100 kHz + RC OSC

25 kHz; First Clock predivider by 16; Sample rate

97.66 Hz

172.58 166.00 170.76 uA

ADC; Single-end mode; Vref: 1.2 V; Force analog

part Enable; Speed selection 100 kHz + RC OSC

2 MHz; First Clock predivider by 16; Sample rate

7.81 kHz

190.91 196.84 216.93 uA

ADC; Single-end mode; Vref: 1.2 V; Force analog

part Enable; Speed selection 100 kHz + RC OSC

2 MHz; First Clock predivider by 1; Sample rate

125.00 kHz

195.71 208.71 255.56 uA

ADC; Single-end mode; Vref: 1.2 V; Force analog

part Enable; Speed selection 100 kHz + Ring OSC;

First Clock predivider by 16; Sample rate 106.45 kHz

224.60 297.64 380.98 uA

ADC; Single-end mode; Vref: 1.2 V; Force analog

part Enable; Speed selection 100 kHz + Ring OSC;

First Clock predivider by 1; Sample rate 1.70 MHz

260.15 342.27 697.94 uA

Table of contents

Other Silego Microcontroller manuals

Popular Microcontroller manuals by other brands

PIMORONI

PIMORONI OctoCam PIM286 Assembling

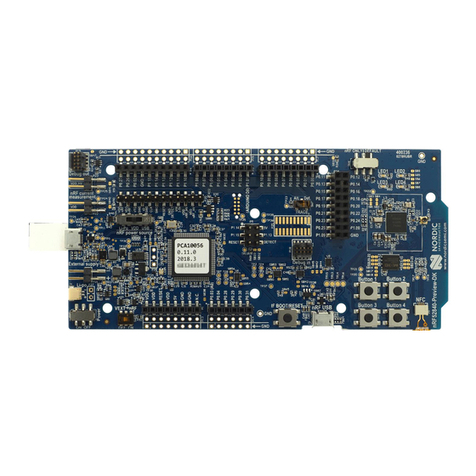

Nordic

Nordic nRF5 Series: nRF52 Getting started guide

Dialog Semiconductor

Dialog Semiconductor DA14531 PRO Hardware user manual

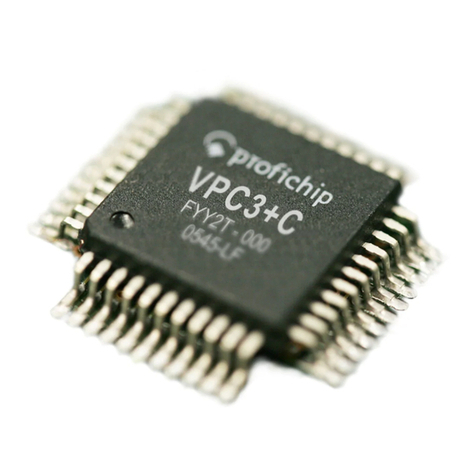

Profichip

Profichip VPC3+C user manual

NXP Semiconductors

NXP Semiconductors MTRCKTSPS5744P quick start guide

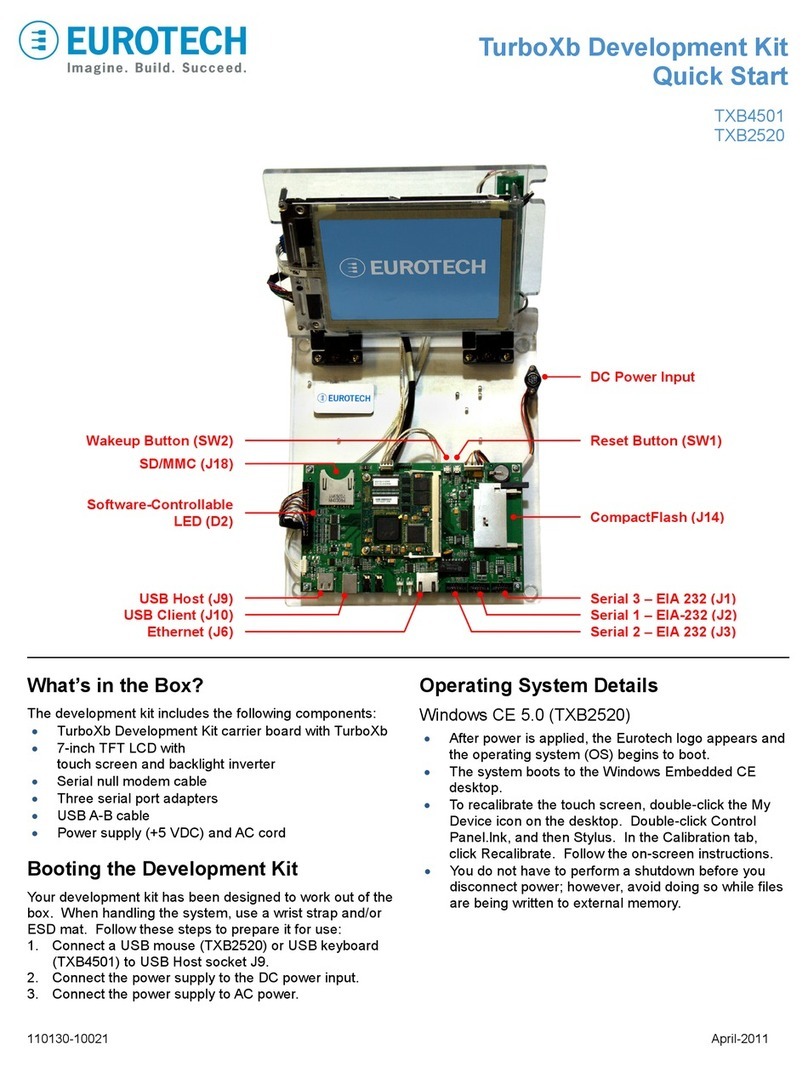

Eurotech

Eurotech TXB4501 quick start

Thundercomm

Thundercomm TurboX C8550 quick start guide

NXP Semiconductors

NXP Semiconductors KE1xF Series Reference manual

ST

ST STM32F105 series Application note

ST

ST STM32 Nucleo Application note

Nuvoton

Nuvoton NuMicro M0A21 Series Technical reference manual

Nuvoton

Nuvoton Mini51 Series Technical reference manual