Table of Contents

1. Overview .................................5

1.1 Work Flow Expectations with ClockBuilder Pro and the Register Map ...........5

1.2 Family Product Comparison .........................6

1.3 Available Software Tools and Support ......................7

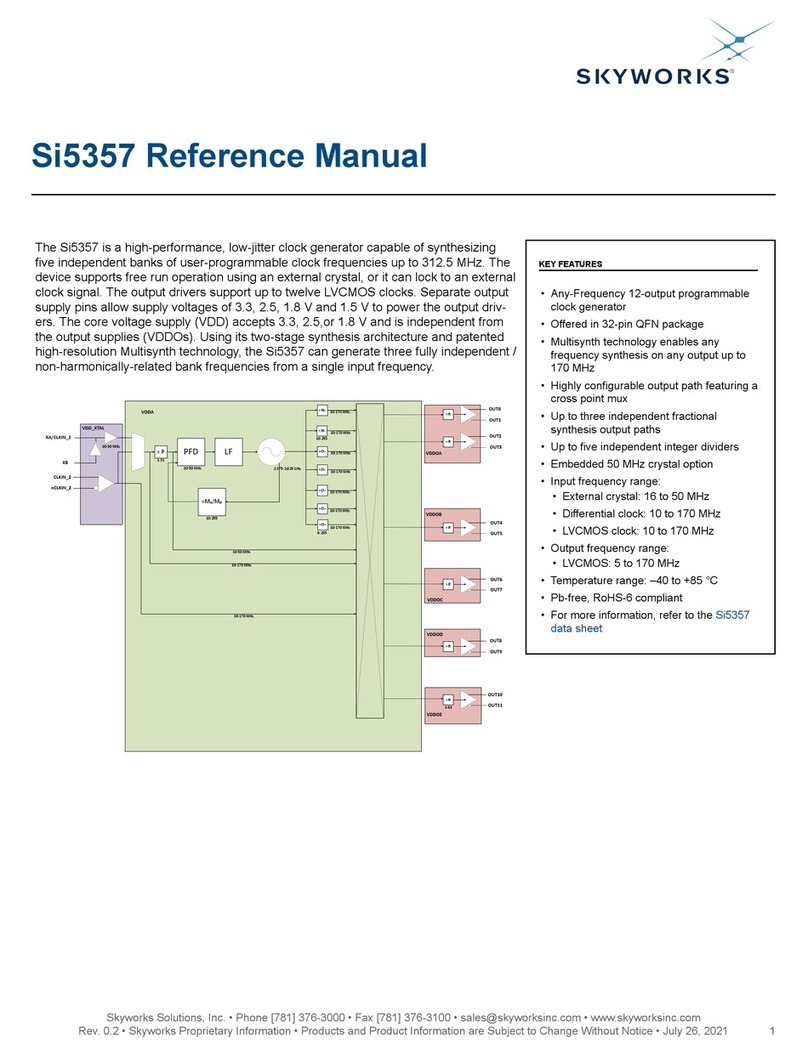

2. Functional Description............................8

2.1 Dividers ................................9

3. Powerup and Initialization ......................... 12

3.1 Reset and Initialization ...........................12

3.1.1 Power Supply Sequencing ........................12

3.2 NVM Programming ............................13

4. Clock Inputs............................... 15

4.1 Inputs on XA/XB .............................15

4.1.1 Crystal on XA/XB............................15

4.1.2 Clock Input on XA/XB ..........................16

4.2 Clock Inputs on IN2, IN1, IN0 .........................17

4.3 Unused Inputs ..............................17

4.4 Reference Input Selection (IN0, IN1, IN2, XA/XB) ..................18

4.5 Fault Monitoring .............................19

4.5.1 Status Indicators ............................20

4.5.2 Interrupt Pin (INTRb) ..........................21

5. Output Clocks .............................. 22

5.1 Outputs ................................22

5.2 Performance Guidelines for Outputs .......................22

5.3 Output Signal Format ............................23

5.3.1 Differential Output Terminations .......................24

5.3.2 Differential Amplitude Controls .......................24

5.3.3 Output Driver Settings for LVPECL, LVDS, HCSL, and CML .............25

5.3.4 LVCMOS Output Terminations .......................26

5.3.5 LVCMOS Output Impedance and Drive Strength Selection ..............27

5.3.6 LVCMOS Output Signal Swing .......................27

5.3.7 LVCMOS Output Polarity .........................28

5.3.8 Output Enable/Disable ..........................29

5.3.9 Output Driver State When Disabled .....................30

5.3.10 Synchronous/Asynchronous Output Disable Feature ...............30

5.4 Output Crosspoint .............................31

5.5 Zero Delay Mode .............................32

6. Digitally Controlled Oscillator (DCO) Modes ................... 34

6.1 Using the N Dividers for DCO Applications ....................34

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 •

[email protected] • www

.skyworksinc.com

2Rev. 1.3 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • July 26, 2021 2