– 1 – E01X50C34

Sony reserves the right to change products and specifications without prior notice.This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices.Sony cannot assume responsibility for any problems arising out of the use of these circuits.

ICX274AL

20 pin DIP (Plastic)

Description

The ICX274AL is a diagonal 8.923mm (Type 1/1.8)

interline CCD solid-state image sensor with a square

pixel array and 2.01M effective pixels. Progressive

scan allows all pixels' signals to be output

independently within approximately 1/15 second,

and output is also possible using various addition

and pulse elimination methods.This chip features an

electronic shutter with variable charge-storage time

which makes it possible to realize full-frame still

images without a mechanical shutter. Further, high

sensitivity and low dark current are achieved through

the adoption of Super HAD CCD technology.

This chip is suitable for image input applications

such as still cameras which require high resolution,

etc.

Features

•High horizontal and vertical resolution

•Supports the following modes

Progressive scan mode (with/without mechanical shutter)

2/8-line readout mode

2/4-line readout mode

2-line addition mode

Center scan modes (1), (2) and (3)

AF modes (1) and (2)

•Square pixel

•Horizontal drive frequency: 28.6364MHz (typ.), 36.0MHz (max.)

•Reset gate bias are not adjusted

•High sensitivity, low dark current

•Continuous variable-speed shutter function

•Excellent anti-blooming characteristics

•20-pin high-precision plastic package

Device Structure

•Interline CCD image sensor

•Image size: Diagonal 8.923mm (Type 1/1.8)

•Total number of pixels: 1688 (H) ×1248 (V) approx. 2.11M pixels

•Number of effective pixels: 1628 (H) ×1236 (V) approx. 2.01M pixels

•Number of active pixels: 1620 (H) ×1220 (V) approx. 1.98M pixels

•Recommended number of

recording pixels: 1600 (H) ×1200 (V) approx. 1.92M pixels

•Chip size: 8.50mm (H) ×6.80mm (V)

•Unit cell size: 4.40µm (H) ×4.40µm (V)

•Optical black: Horizontal (H) direction: Front 12 pixels, rear 48 pixels

Vertical (V) direction: Front 10 pixels, rear 2 pixels

•Number of dummy bits: Horizontal 28

Vertical 1

•Substrate material: Silicon

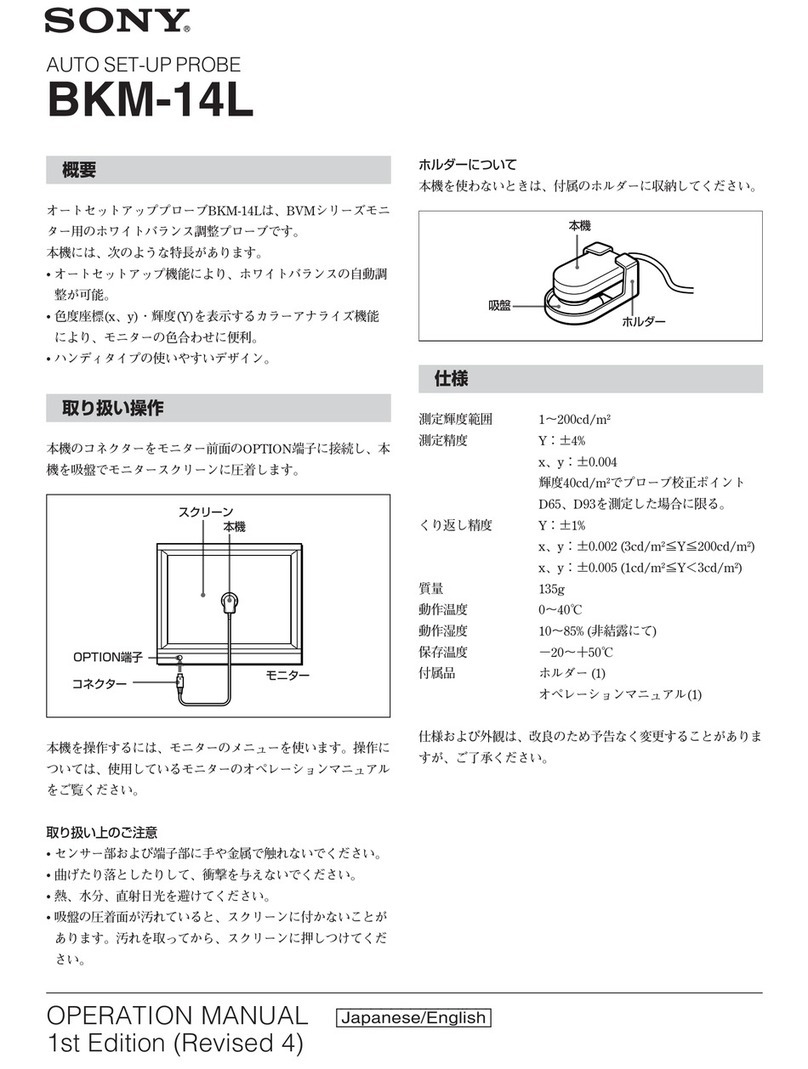

Optical black position

(Top View)

2

10

V

H

Pin 1

Pin 11 48

12

Diagonal 8.923mm (Type 1/1.8) Progressive Scan CCD Image Sensor with Square Pixel for B/W Video Cameras