– 8 –

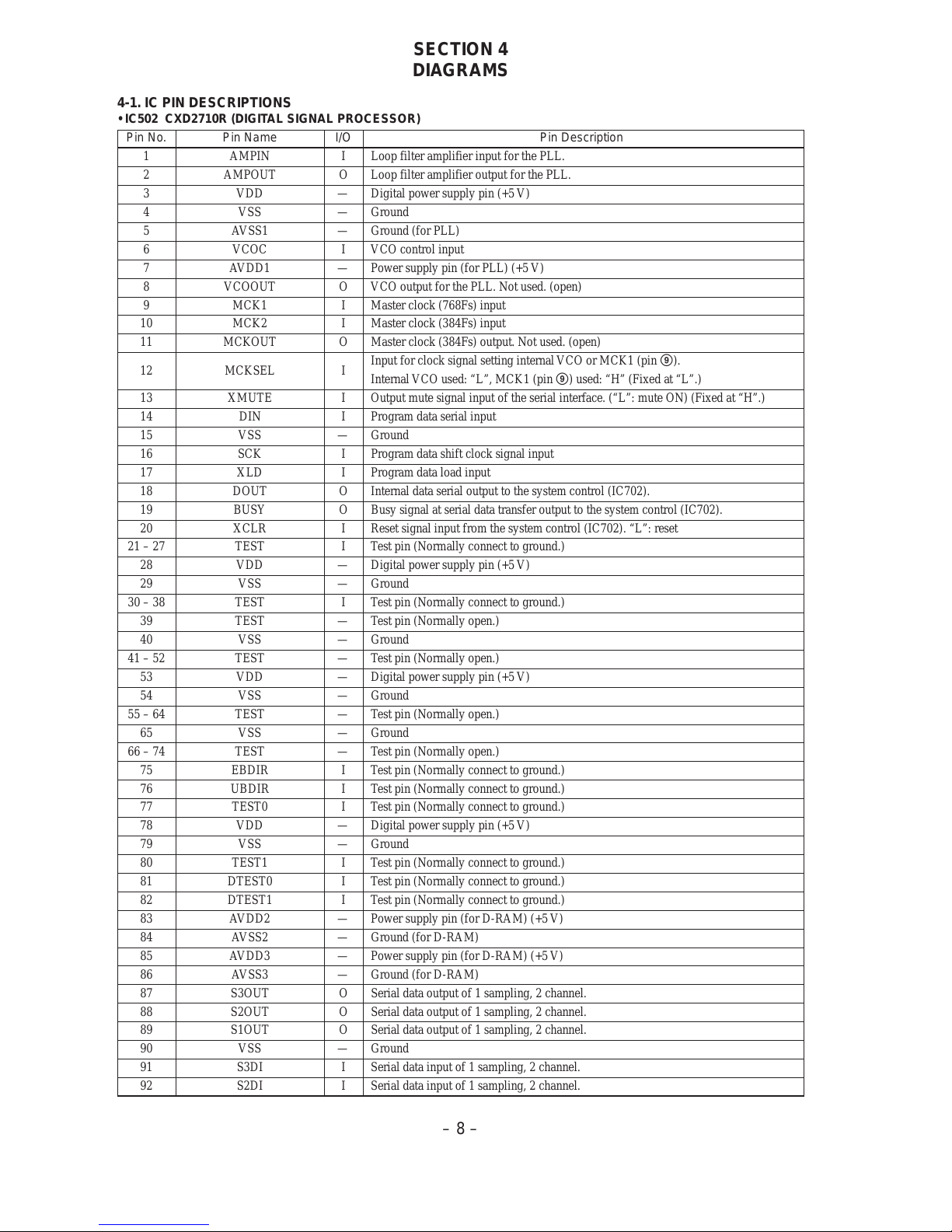

SECTION 4

DIAGRAMS

4-1. IC PIN DESCRIPTIONS

• IC502 CXD2710R (DIGITAL SIGNAL PROCESSOR)

Pin No. Pin Name I/O Pin Description

1 AMPIN I Loop filter amplifier input for the PLL.

2 AMPOUT O Loop filter amplifier output for the PLL.

3 VDD — Digital power supply pin (+5 V)

4 VSS — Ground

5 AVSS1 — Ground (for PLL)

6 VCOC I VCO control input

7 AVDD1 — Power supply pin (for PLL) (+5V)

8 VCOOUT O VCO output for the PLL. Not used. (open)

9 MCK1 I Master clock (768Fs) input

10 MCK2 I Master clock (384Fs) input

11 MCKOUT O Master clock (384Fs) output. Not used. (open)

12 MCKSEL I Input for clock signal setting internal VCO or MCK1 (pin 9).

Internal VCO used: “L”, MCK1 (pin 9) used: “H” (Fixed at “L”.)

13 XMUTE I Output mute signal input of the serial interface. (“L”: mute ON) (Fixed at “H”.)

14 DIN I Program data serial input

15 VSS — Ground

16 SCK I Program data shift clock signal input

17 XLD I Program data load input

18 DOUT O Internal data serial output to the system control (IC702).

19 BUSY O Busy signal at serial data transfer output to the system control (IC702).

20 XCLR I Reset signal input from the system control (IC702). “L”: reset

21 – 27 TEST I Test pin (Normally connect to ground.)

28 VDD — Digital power supply pin (+5 V)

29 VSS — Ground

30 – 38 TEST I Test pin (Normally connect to ground.)

39 TEST — Test pin (Normally open.)

40 VSS — Ground

41 – 52 TEST — Test pin (Normally open.)

53 VDD — Digital power supply pin (+5 V)

54 VSS — Ground

55 – 64 TEST — Test pin (Normally open.)

65 VSS — Ground

66 – 74 TEST — Test pin (Normally open.)

75 EBDIR I Test pin (Normally connect to ground.)

76 UBDIR I Test pin (Normally connect to ground.)

77 TEST0 I Test pin (Normally connect to ground.)

78 VDD — Digital power supply pin (+5 V)

79 VSS — Ground

80 TEST1 I Test pin (Normally connect to ground.)

81 DTEST0 I Test pin (Normally connect to ground.)

82 DTEST1 I Test pin (Normally connect to ground.)

83 AVDD2 — Power supply pin (for D-RAM) (+5V)

84 AVSS2 — Ground (for D-RAM)

85 AVDD3 — Power supply pin (for D-RAM) (+5V)

86 AVSS3 — Ground (for D-RAM)

87 S3OUT O Serial data output of 1 sampling, 2 channel.

88 S2OUT O Serial data output of 1 sampling, 2 channel.

89 S1OUT O Serial data output of 1 sampling, 2 channel.

90 VSS — Ground

91 S3DI I Serial data input of 1 sampling, 2 channel.

92 S2DI I Serial data input of 1 sampling, 2 channel.