– 3 –

NOTES ON HANDLING THE OPTICAL PICK-UP

BLOCK OR BASE UNIT

The laser diode in the optical pick-up block may suffer electro-

static break-down because of the potential difference generated

by the charged electrostatic load, etc. on clothing and the human

body.

During repair, pay attention to electrostatic break-down and also

use the procedure in the printed matter which is included in the

repair parts.

The flexible board is easily damaged and should be handled with

care.

NOTES ON LASER DIODE EMISSION CHECK

The laser beam on this model is concentrated so as to be focused

on the disc reflective surface by the objective lens in the optical

pick-up block. Therefore, when checking the laser diode emis-

sion, observe from more than 30 cm away from the objective lens.

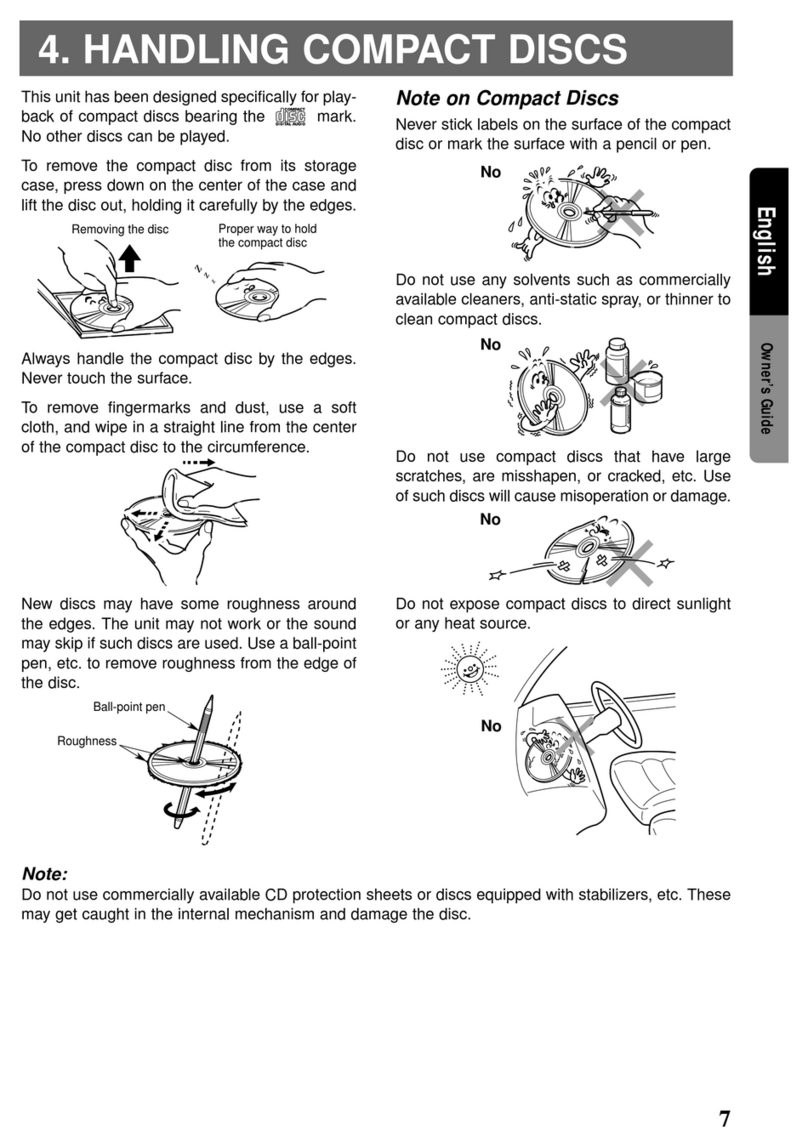

Notes on chip component replacement

•Never reuse a disconnected chip component.

•Notice that the minus side of a tantalum capacitor may be dam-

aged by heat.

Flexible Circuit Board Repairing

•Keep the temperature of the soldering iron around 270 ˚C dur-

ing repairing.

•Do not touch the soldering iron on the same conductor of the

circuit board (within 3 times).

•Be careful not to apply force on the conductor when soldering

or unsoldering.

This appliance is classified as a CLASS 1 LASER product.

The CLASS 1 LASER PRODUCT MARKING is located on

the rear exterior.

Laser component in this product is capable of emitting radiation

exceeding the limit for Class 1.

The following caution label is located inside the unit.

CAUTION

Use of controls or adjustments or performance of

procedures other than those specified herein may

result in hazardous radiation exposure.

SAFETY CHECK-OUT

After correcting the original service problem, perform the follow-

ing safety check before releasing the set to the customer:

Check the antenna terminals, metal trim, “metallized” knobs,

screws, and all other exposed metal parts for AC leakage. Check

leakage as described below.

LEAKAGE TEST

The AC leakage from any exposed metal part to earth ground and

from all exposed metal parts to any exposed metal part having a

return to chassis, must not exceed 0.5 mA (500 microampers).

Leakage current can be measured by any one of three methods.

1. A commercial leakage tester, such as the Simpson 229 or RCA

WT-540A. Follow the manufacturers’instructions to use these

instruments.

2. A battery-operated AC milliammeter. The Data Precision 245

digital multimeter is suitable for this job.

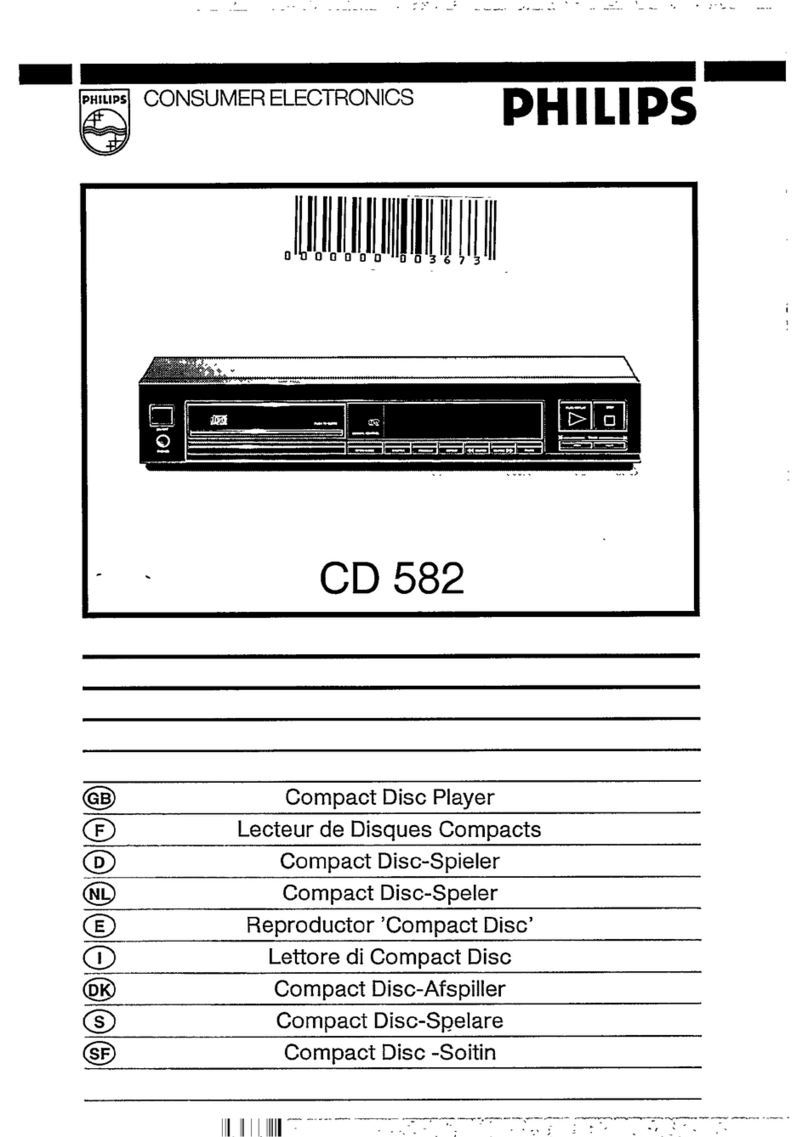

3. Measuring the voltage drop across a resistor by means of a

VOM or battery-operated AC voltmeter. The “limit” indica-

tion is 0.75 V, so analog meters must have an accurate low-

voltage scale. The Simpson 250 and Sanwa SH-63Trd are ex-

amples of a passive VOM that is suitable. Nearly all battery

operated digital multimeters that have a 2VAC range are suit-

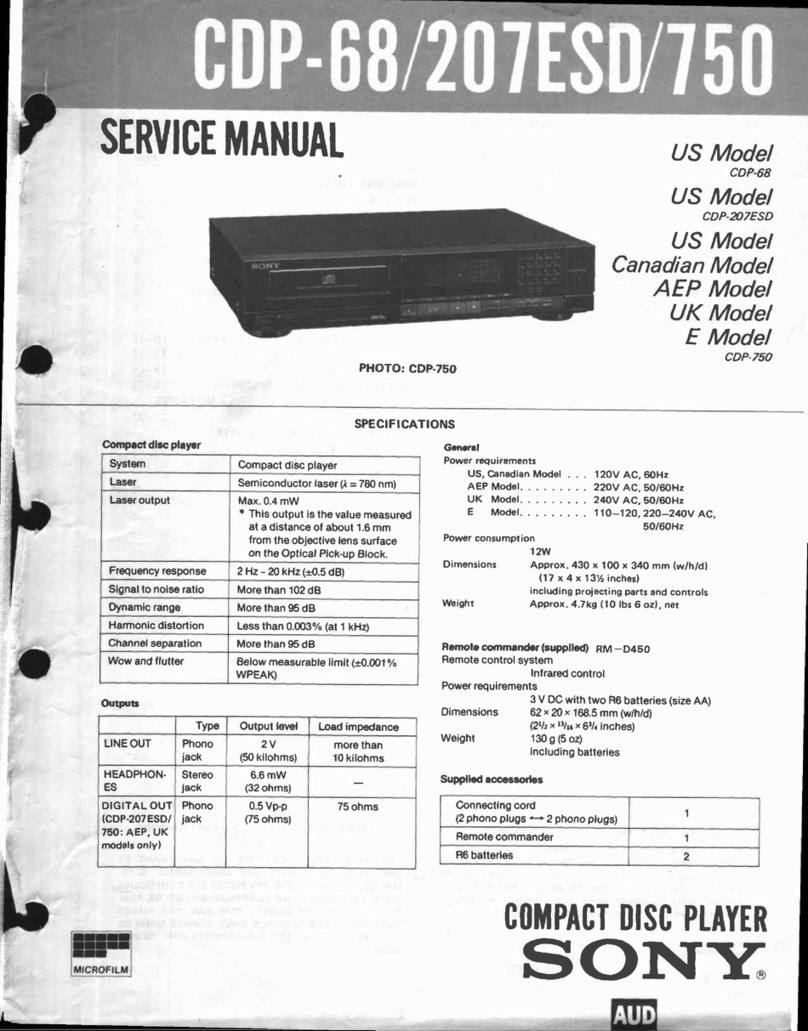

able. (See Fig. A)

1.5 k

Ω

0.15

µ

FAC

voltmeter

(0.75 V)

To Exposed Metal

Parts on Set

Earth Ground

Fig. A. Using an AC voltmeter to check AC leakage.